Introduction à la programmation // sur GPUs en CUDA et Python

Introduction à la programmation // sur GPUs

en CUDA et Python

Denis Robilliard

Équipe CAMOME: C. Fonlupt, V. Marion-Poty, A. Boumaza

LISIC — ULCO

Univ Lille Nord de France

BP 719, F-62228 Calais Cedex, France

Email: [email protected]

Séminaire LISIC 19/05/2011

Denis Robilliard Introduction à la programmation // sur GPUs en CUDA et Python Séminaire LISIC 19/05/2011 1 / 24

Introduction

Cadre de l’exposé

Historique : suite à l’exposé de François Rousselle du 17 février 2011

Objectif : présenter quelques bases de la programmation // sur GPU

Matériel : machine "baru" 8 cartes Tesla C2050, fabricant Nvidia

Langages : CUDA (seulement sur matériel Nvidia), Python

Application : "les nombres de Schur", problème de combinatoire

Note

On ne s’intéressera pas aux aspects calculs pour le graphisme

Denis Robilliard Introduction à la programmation // sur GPUs en CUDA et Python Séminaire LISIC 19/05/2011 2 / 24

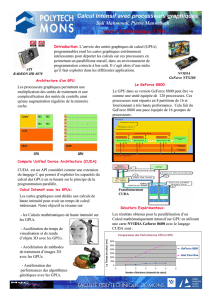

Architecture matérielle –1

Rappel

Valable uniquement pour GPUs Nvidia post-2006 (GPU G-80 et suivants)

Modèle de programmation vu à travers le langage CUDA

Schéma de l’architecture d’une carte (device) C2050

...

Device = x 14 multiprocessors = 448 cores

48 Ko Fast Shared RAM

Stream proc

/ Core

Registres

...

Multiprocesseur = x 32 cores

Stream proc

/ Core

Registres

...

48 Ko Fast Shared RAM

Stream proc

/ Core

Registres

...

Multiprocesseur = x 32 cores

Stream proc

/ Core

Registres

2 Go Global RAM

Denis Robilliard Introduction à la programmation // sur GPUs en CUDA et Python Séminaire LISIC 19/05/2011 4 / 24

Architecture matérielle –2

Constitution d’un multi-processeur : les cœurs

Un cœur (core /stream processor) a son propre jeu de registres

Un multiprocesseur = 32 cœurs + 48 Ko de mémoire partagée rapide

(aussi rapide que les registres — accès en 4 cycles)

Ils accèdent tous à la mémoire globale de la carte (2 Go — accès en 400

cycles)

Les 32 cœurs d’un multiprocesseur sont en SIMD (Single Instruction,

Multiple Data) : même instruction "en même temps", potentiellement sur

des données différentes

Cas des structures conditionnelles : tous les cœurs ne doivent pas

forcément faire la même chose ⇒certains cœurs seront oisifs (idle) et on

parle de divergence (= perte d’efficacité)

Denis Robilliard Introduction à la programmation // sur GPUs en CUDA et Python Séminaire LISIC 19/05/2011 5 / 24

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

1

/

31

100%