Implantation de H.264 sur MPSoC

UNIVERSITÉ BADJI UNIVERSITÉ DE

MOKHTAR-ANNABA BOURGOGNE

THESE

Présentée pour obtenir le grade de Docteur de l’Université de Bourgogne

Spécialité : INSTRUMENTATION ET INFORMATIQUE DE L’IMAGE

Présentée pour obtenir le grade de Docteur en science de l’université de Annaba

Spécialité : ELECTRONIQUE

Par

MESSAOUDI Kamel

Traitement des Signaux et Images en Temps

Réel « Implantation de H.264 sur MPSoC »

Soutenue le 19 Décembre 2012 devant la commission d’examen composée de :

M. Nadir FARAH Professeur, Université Badji Mokhtar d’Annaba , Algérie Président

M. Camel TANOUGAST Maître de conférences, Université Paul Verlaine-Metz, France Rapporteur

M. Alaoua CHAOUI Professeur, Université Mentouri-Constantine, Algérie Rapporteur

M. Jean-Marie BILBAULT Professeur, Université de Bourgogne-Dijon, France Membre

M. Ahmed BOURIDANE Professeur, Université de New Castle, UK Membre

M. N.E BOUKEZZOULA Maitre de Conférences, Université de Sétif, Algérie Membre

M. El-Bay BOURENNANE Professeur, Université de Bourgogne-Dijon, France Directeur

M. Salah TOUMI Professeur, Université Badji Mokhtar d’Annaba , Algérie Co-Directeur

LERICA

Université Badji

Mokhtar - Annaba

N° d’ordre : ……………..

i

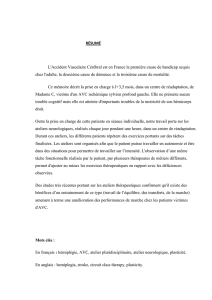

RÉSUMÉ

Cette thèse est élaborée en cotutelle entre l’université Badji Mokhtar (Laboratoire LERICA) et

l’université de bourgogne (Laboratoire LE2I, UMR CNRS 5158). Elle constitue une contribution à

l’étude et l’implantation de l’encodeur H.264/AVC. Durent l’évolution des normes de compression

vidéo, une réalité sure est vérifiée de plus en plus : avoir une bonne performance du processus de

compression nécessite l’élaboration d’équipements beaucoup plus performants en termes de puissance

de calcul, de flexibilité et de portabilité et ceci afin de répondre aux exigences des différents

traitements et satisfaire au critère « Temps Réel ». Pour assurer un temps réel pour ce genre

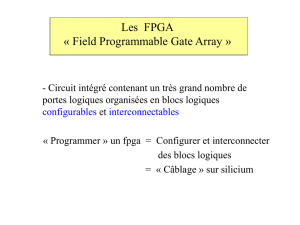

d’applications, une solution reste possible est l’utilisation des systèmes sur puce (SoC) ou bien des

systèmes multiprocesseurs sur puce (MPSoC) implantés sur des plateformes reconfigurables à base de

circuit FPGA.

L’objective de cette thèse consiste à l’étude et l’implantation des algorithmes de traitement des signaux

et images et en particulier la norme H.264/AVC, et cela dans le but d’assurer un temps réel pour le

cycle codage-décodage. Nous utilisons deux plateformes FPGA de Xilinx (ML501 et XUPV5). Dans

la littérature, il existe déjà plusieurs implémentations du décodeur. Pour l’encodeur, malgré les efforts

énormes réalisés, il reste toujours du travail pour l’optimisation des algorithmes et l’extraction des

parallélismes possibles surtout avec une variété de profils et de niveaux de la norme H.264/AVC.

Dans un premier temps de cette thèse, nous proposons une implantation matérielle d’un contrôleur

mémoire spécialement pour l’encodeur H.264/AVC. Ce contrôleur est réalisé en ajoutant, au

contrôleur mémoire DDR2 des deux plateformes de Xilinx, une couche intelligente capable de calculer

les adresses et récupérer les données nécessaires pour les différents modules de traitement de

l’encodeur. Ensuite, nous proposons des implantations matérielles (niveau RTL) des modules de

traitement de l’encodeur H.264. Sur ces implantations, nous allons exploiter les deux principes de

parallélisme et de pipelining autorisé par l’encodeur en vue de la grande dépendance inter-blocs. Nous

avons ainsi proposé plusieurs améliorations et nouvelles techniques dans les modules de la chaine Intra

et le filtre anti-blocs. A la fin de cette thèse, nous utilisons les modules réalisés en matériels pour la

l’implantation Matérielle/logicielle de l’encodeur H.264/AVC. Des résultats de synthèse et de

simulation, en utilisant les deux plateformes de Xilinx, sont montrés et comparés avec les autres

implémentations existantes.

Mots clés : Implantation matérielle, Codesign, L’encodeur H.264/AVC, Temps réel, Gestion de

mémoire, Contrôleur mémoire, Parallélisme, Pipelining, SoC, MPSoC, FPGA,

Plateforme de prototypage, Xilinx, ML501, XUPV5.

ii

ABSTRACT

This thesis has been carried out in joint supervision between the Badji Mokhtar University (LERICA

Laboratory) and the University of Burgundy (LE2I laboratory, UMR CNRS 5158). It is a contribution

to the study and implementation of the H.264/AVC encoder. The evolution in video coding standards

have historically demanded stringent performances of the compression process, which imposes the

development of platforms that perform much better in terms of computing power, flexibility and

portability. Such demands are necessary to fulfill requirements of the different treatments and to meet

"Real Time" processing constraints. In order to ensure real-time performances, a possible solution is to

made use of systems on chip (SoC) or multiprocessor systems on chip (MPSoC) built on platforms

based reconfigurable FPGAs.

The objective of this thesis is the study and implementation of algorithms for signal and image

processing (in particular the H.264/AVC standard); especial attention was given to provide real-time

coding-decoding cycles. We use two FPGA platforms (ML501 and XUPV5 from Xilinx) to implement

our architectures. In the literature, there are already several implementations of the decoder. For the

encoder part, despite the enormous efforts made, work remains to optimize algorithms and extract the

inherent parallelism of the architecture. This is especially true with a variety of profiles and levels of

H.264/AVC.

Initially, we proposed a hardware implementation of a memory controller specifically targeted to the

H.264/AVC encoder. This controller is obtained by adding, to the DDR2 memory controller, an

intelligent layer capable of calculating the addresses and to retrieve the necessary data for several of

the processing modules of the encoder. Afterwards, we proposed hardware implementations (RTL) for

the processing modules of the H.264 encoder. In these implementations, we made use of principles of

parallelism and pipelining, taking into account the constraints imposed by the inter-block dependency

in the encoder. We proposed several enhancements and new technologies in the channel Intra modules

and the deblocking filter. At the end of this thesis, we use the modules implemented in hardware for

implementing the H.264/AVC encoder in a hardware/software design. Synthesis and simulation

results, using both platforms for Xilinx, are shown and compared with other existing implementations.

Keywords : Hardware implementation, Codesign, H.264/AVC encoder, Real time, memory

management, Memory controller, Parallelism, Pipelining, SoC, MPSoC, FPGA,

Prototyping platform, Xilinx, ML501, XUPV5.

iii

LERICAbourgogne

LE2IUMR-CNRS 5158. H.264/AVC

Temps Réel"

systèmes sur puce

systèmes multiprocesseurs sur puce MPSoC FPGA

H.264/AVC

FPGAML501 et XUPV5Xilinx

H.264/AVC

H.264/AVC

H.264/AVC

DDR2 FPGA

Xilinx

RTL

H.264/AVC Pipeline

H.264/AVC

: Codesign H.264

PipeliningSoCMPSoCFPGAFPGAXilinxML501

XUPV5

iv

A la mémoire de mon père

Puisse Dieu, le tout puissant,

l’avoir en sa sainte miséricorde

A ma mère

A celle que j’aime

A ma petite fille Maissane

A ma famille

A tous ceux qui me tiennent à cœur

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

141

141

142

142

143

143

144

144

145

145

146

146

147

147

148

148

149

149

150

150

151

151

152

152

153

153

154

154

155

155

156

156

157

157

158

158

159

159

160

160

161

161

162

162

163

163

164

164

165

165

166

166

167

167

168

168

169

169

170

170

171

171

172

172

173

173

174

174

175

175

176

176

177

177

178

178

1

/

178

100%