Introduction au Calcul Haute Performance

publicité

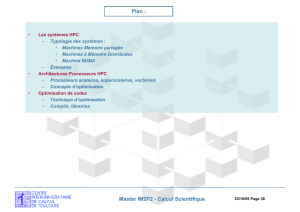

Introduction au Calcul Haute Performance Nicolas Renon, Ingénieur en Calcul Scientifique, Ph. D CICT ( Centre Interuniversitaire de Calcul de Toulouse ) ([email protected]) http://www.calmip.cict.fr ; http://www.cict.fr Master IM2P2 - Calcul Scientifique 19/10/09 Page 1 Plan : • • • Les systèmes HPC – Typologie des systèmes : • Machines Mémoire partagée • Machines à Mémoire Distribuées • Machine NUMA – Exemple : Visite CICT Architectures Processeurs HPC – Processeurs scalaires, superscalaires, vectoriels – Concepts d’optimisation Optimisation de codes – Technique d’optimisation – Compilo, librairies Master IM2P2 - Calcul Scientifique 19/10/09 Page 2 Calcul Intensif et Système HPC Calcul Intensif : Principes des systèmes HPC Hardware et Software Performance Calcul Flottants Flop/s + Mémoire (RAM et espace fichier) Flop : floating operation (mult, add) opération Stockage, I/O sur les nombres à virgule flottantes (nombre réels) ++ Mutualisation, Centralisation 3,14159 -6,8675456342 E+08 Plusieurs Utilisateurs d’un même serveur Partage des ressources cohérent : Règles Utilisation OS performant : Multi-applications, Multi-User Serveur Totalement Dédié au Calcul Applications Scientifiques Calcul uniquement Sauvegarde Espace Fichier / Stockage Accès distant contrainte d’hébergement lourdes : Electricité, (secouru) Refroidissement Poids Sécurité …. Master IM2P2 - Calcul Scientifique 19/10/09 Page 3 Panorama Systèmes HPC UMA Accès Mémoire Uniforme Machine à Mémoire Partagée : •Multiprocesseurs •Un seul espace d’adressage •Mémoire partagée NUMA Accès Mémoire Non Uniforme PROGRAMME Machine à Mémoire Distribuées (Cluster) : NORMA no-remote memory access •Multi-Ordinateurs •Espace d’Adressage Multiple Master IM2P2 - Calcul Scientifique 19/10/09 Page 4 Panorama MIMD UMA NUMA NORMA MPP Multiple Instruction s Multiple Data Uniform Memory Access Non-Uniform Memory Access No-Remote Memory Access Massively Parallel Processor PVP (Cray T90) UMA Central Memory Multiprocessors Single Address space Shared Memory PVP SMP COMA CC-NUMA NCC-NUMA NUMA Parallel Vector Processor Symmetric Multi-Processor Cache Only Memory Architecture Cache-Coherent NUMA Non-Cache Coherent NUMA distributed memory SMP (Intel SHV, SUN E10000, DEC 8400 SGI Power Challenge, IBM R60, etc.) COMA (KSR-1, DDM) CC-NUMA (SGI 3000, SGI 2000, Altix HP Exemplar,Sequent NUMA-Q, Data General) NCC-NUMA (Cray T3E) MIMD Multicomputers Multiple Address spaces NORMA no-remote memory access Cluster (IBM SP2, DEC TruCluster, Microsoft Wolfpack, etc.) loosely coupled “MPP” (Intel TFLOPS, Cray T3E) tightly coupled Master IM2P2 - Calcul Scientifique 19/10/09 Page 5 Mémoire Partagée : Architecture UMA – Coté utilisateur : • Une seule Machine (1 seul OS) - plusieurs processeurs - un seul espace d’adressage mémoire • Programmation : extension programmation monoprocesseur – Coté Machine : SMP Symmetric MultiProcessor • Bus Interconnexion entre la mémoire et les processeurs • Mémoire centrale et les E/S : partagées par tous les processeurs • Proc. accèdent même mémoire centrale Cohérence de Cache – cohérence de cache # processeurs modifient éléments même ligne de cache Register File Shared memory Cache Functional Unit (mult, add) Cache Coherency Unit Register File Cache Processor Functional Unit (mult, add) Cache Coherency Unit Processor OS Master IM2P2 - Calcul Scientifique 19/10/09 Page 6 Cohérence des caches A=1.5E8 Shared memory Bus interconnect A=1.5E8 cache cache cache FPU FPU FPU Master IM2P2 - Calcul Scientifique 19/10/09 Page 7 Cohérence des caches A=1.5E8 Shared memory Bus interconnect A=1.5E8 cache cache cache FPU FPU FPU Master IM2P2 - Calcul Scientifique A=1.5E8 19/10/09 Page 8 Cohérence des caches Shared memory A=1.5E8 Bus interconnect A=1.5E8 cache FPU A=0.6E-2 cache cache FPU FPU A=1.5E8 Les processeurs ont des valeurs différentes de A Master IM2P2 - Calcul Scientifique 19/10/09 Page 9 Cohérence des caches Shared memory A=1.5E8 Bus interconnect ? A=1.5E8 cache FPU A=0.6E-2 cache cache FPU FPU A=1.5E8 ? Les processeurs ont des valeurs différentes de A Intolérable point de vue programmeur Master IM2P2 - Calcul Scientifique 19/10/09 Page 10 Machine UMA - Cohérence des caches – Différents protocoles de cohérence des caches • Invalidation – 1 write invalidation données autres processeurs • Snooping – Transparent pour l’utilisateur – Mais : • Pèse sur la performance de la machine • Le programmeur doit en avoir conscience OpenMP Master IM2P2 - Calcul Scientifique 19/10/09 Page 11 Problèmes des architectures UMA – Accès à la mémoire: – les accès concourants des processeurs à la mémoire partagée créent un goulot d’étranglement Dégradation des performances (temps accès donnée ) – des niveaux de caches (tailles) efficaces permettent d’économiser des références à la mémoire Register File memory Cache Functional Unit (mult, add) Cache Coherency Unit Processor Register File Cache Functional Unit (mult, add) Cache Coherency Unit Processor OS Conséquence : faible nombre de processeurs •Cette difficulté peut être levée avec les architectures à mémoire distribuée : •Ressource mémoire décentralisée Master IM2P2 - Calcul Scientifique 19/10/09 Page 12 Machine mémoire partagée Retour Architecture processeurs Multi-core : •Différents choix d’architectures 2 cores distincts Caches distincts Cache partagé Cohérence des caches 2 bi-core Cohérence des caches/ bi-core Machines à Mémoire Partagée ! 1 bi-core = 2 mono-core ? Nécessité parallèlisation des applications Master IM2P2 - Calcul Scientifique 19/10/09 Page 13 Mémoire Distribuée (NORMA) – Ensemble processeurs mémoire interconnecté par un réseaux • MPP : Massively Parallel Processing : intégration avec couplage/interconnexion étroite, une seule machine • Cluster : interconnexion de machines(SMP) entre elles (switch) Master IM2P2 - Calcul Scientifique 19/10/09 Page 14 Mémoire Distribuée : Cluster Cluster : Point fort • Technologie de masse, beaucoup de processeurs • Beaucoup de « machines » interconnectées • Les nœuds ou machines : plusieurs processeurs M E/S M P E/S M E/S E/S E/S P M M P E/S P Réseau d’interconnexion P P M E/S P Master IM2P2 - Calcul Scientifique 19/10/09 Page 15 M E/S P M Mémoire Distribuée : Architecture multi-ordinateurs (Clusters) – Coté Machine : • Technologie de masse, beaucoup de processeurs • Les processeurs accèdent uniquement à leur propre mémoire locale • réseau Interconnexion entre « ordinateurs » défi technique capacité transfert données (n OS, etc…) Main Register File memory Functional Unit (mult, add) Cache Main Register File memory Functional Unit (mult, add) Cache Processor disk OS 1 Master IM2P2 - Calcul Scientifique Processor disk OS 2 19/10/09 Page 16 Mémoire Distribuée : Architecture multi-ordinateurs (Clusters) – Coté utilisateur : • n Machine différentes (n OS) interconnectées, 1 (ou +) proc. par machine • Programmation parallèle transfert de message (MPI , charge du programmeur) • Outils pour faciliter accès ressources et aux données Main Register File memory Functional Unit (mult, add) Cache Main Register File memory Functional Unit (mult, add) Cache Processor disk OS 1 Master IM2P2 - Calcul Scientifique Processor disk OS 2 19/10/09 Page 17 Architecture à mémoire partagée physiquement distribuée Machine NUMA : Non-Uniform Memory Access • Mixage SMP/cluster • Souplesse d’utilisation et performance • Dépendance « spatiale » par rapport aux ressources utilisées P M P M P M P M Réseau d’interconnexion P M P M M P Master IM2P2 - Calcul Scientifique 19/10/09 Page 18 P M Architecture à mémoire partagée physiquement distribuée – Coté Machine : Non-uniform memory access (NUMA) • • • • La mémoire est globalement adressable mais physiquement distribuées Proc. accèdent mémoire locale et mémoire distante Cohérence de Cache (ccNUMA) Interconnex très performant + topologie complexe (chemin redondants) Accès locaux + rapides accès lointains Register File Main memory Cache Functional Unit (mult, add) Cache Coherency Unit Register File Main memory Cache Processor Functional Unit (mult, add) Cache Coherency Unit Processor OS interconnect Master IM2P2 - Calcul Scientifique 19/10/09 Page 19 Architecture à mémoire partagée physiquement distribuée – Machine NUMA : Coté utilisateur • une seule Machine, 1 seul OS • Accès à un grand nbre de proc. Et beaucoup de mémoire (globalement adressable) • Programmation en mémoire partagée et mémoire distribuée(échange de message) Register File Main memory Cache Functional Unit (mult, add) Cache Coherency Unit Register File Main memory Cache Processor Functional Unit (mult, add) Cache Coherency Unit Processor OS interconnect Master IM2P2 - Calcul Scientifique 19/10/09 Page 20 Actuellement : Nœud de Calcul NUMA Nœud de Calcul 8 cores : NUMA Dual x4 DDR IB (4GB/s each) Master IM2P2 - Calcul Scientifique 19/10/09 Page 21 Interconnexion / réseaux Système à mémoire partagée et distribués Processeurs : commodity, RISC processeur mémoire : barrette standard DRAM Réseau/Interconnexion : liaison entre les processeur et la mémoire (bus, crossbar) entre les machines (cluster) ou des « unité » de calcul (NUMA) : Ethernet Protocole spécifique : infiniband, myrinet, NUMAlink topologie : Anneau, étoile, fat-tree, tore, hypercube Interconnexion : Latence : Combien de temps avant de démarrer un transfert de données ? Ordre de la microseconde Débit (bandwidth): A quel taux les données sont transférées ? Mbytes/sec Topologie : graphe d’interconnexion des unités de calcul Garantie les capacités du réseau à pleine charge 1 Mo/s 1 Megaoctet/s 106 octets/sec 1 Go/s 1 Gigaoctet/s 109 octets/sec 1 To/s 1 Téraoctet/s 1012 octets/s Master IM2P2 - Calcul Scientifique 19/10/09 Page 22 Interconnexion / réseaux Interconnexion : Topologie : Meilleur choix : Chaque processeur connecté à tous les autres : prix irréalisable à grande échelle (10000 procs, etc…) Faire des choix sous contraintes : Repousser les goulots d’étranglements réalisation physique (faisabilité, coûts, etc…) Extensibilité du réseau (combien de procs) Différentes stratégies Cross-bar Master IM2P2 - Calcul Scientifique 19/10/09 Page 23 Interconnexion / réseaux : complexité Notations: # procs = N = 2P diamètre = d (chemin critique entre 2 processeurs , le plus petit des pires chemin possible) # liens = w inf calcul du diamètre pour une topologie en anneau (N=4): sup d p,q P d D( p,q ) ( p,q) P, p = 0, p = 1 {d,d D(0,1)} = {d1;d2 + d3 + d4 } sup = {d2 + d3 + d4 } Topologie Anneau: 0,1 sup = sup = sup = sup 0,1 1,2 2,3 3,0 d4 ( p,q) P, p = 0, p = 2 3 sup = {d1 + d2 }ou{d3 + d4 } 0,2 d3 sup = sup sup 0,2 inf 1,3 1 2 d2 0,1 sup d = {d1 + d2 } = ( p,q ) P d D ( p,q ) d1 0 N 2 Master IM2P2 - Calcul Scientifique 19/10/09 Page 24 Interconnexion / réseaux : complexité Notations: # procs = N = 2P diamètre = d (chemin critique entre 2 processeurs , le plus petit des pires chemin possible) # liens = w inf Anneau: Grille 2D : Tore 2D : d= N ,w = N 2 ( N ) 1 1 1 d = 2 N 2 1,w = 2 N 2 N 2 1 1 2 sup d p,q P d D( p,q ) d = N ,w = 2 N 1 N 2 ,( N ) 1 N 2 ,( N ) Master IM2P2 - Calcul Scientifique 19/10/09 Page 25 Interconnexion / réseaux comparaison: p= N=2 4 16 Anneau grille2D Tore2DEnhanced d 8 6 4 P 6 64 8 256 16 10 1024 64 w 16 24 32 d 32 14 8 256 w 64 240 128 128 30 16 Master IM2P2 - Calcul Scientifique 1024 256 480 512 512 62 32 1024 1984 2048 19/10/09 Page 26 Interconnexion / réseaux : complexité topologie Hypercube 3D, 4D, 8D Master IM2P2 - Calcul Scientifique 19/10/09 Page 27 Interconnexion / réseaux : complexité Fat-tree « mirrored » Master IM2P2 - Calcul Scientifique 19/10/09 Page 28 Interconnexion / réseaux : complexité Réseaux actuels (sur machines parallèles) : Atténuation des effets « spaciaux » : Peu de différences de coût (en temps) entre source/destination Développement algorithmique moins contraint par le hardware Master IM2P2 - Calcul Scientifique 19/10/09 Page 29 Interconnexion / réseaux : implémentation Contexte Ssi (Machine ccNUMA) : 1 seule image OS Crossbar : « Routage gravé » BUS machine Unité de Calcul Master IM2P2 - Calcul Scientifique 19/10/09 Page 30 Interconnexion / réseaux : implémentation Contexte cluster : n machine n image OS Defi technique : Protocole TCP/IP Dialogue OS à OS Switch x ports Cable réseaux RJ45 Machine (nœud) de Calcul Master IM2P2 - Calcul Scientifique 19/10/09 Page 31 Interconnexion / réseaux : mise en oeuvre Contexte cluster : block élémentaires à n nœuds de calcul (128,256 cores) Block élémentaire => topologie optimale on interconnecte les blocks Master IM2P2 - Calcul Scientifique 19/10/09 Page 32 Interconnexion / réseaux : mise en oeuvre Contexte cluster : on interconnecte les blocks Master IM2P2 - Calcul Scientifique 19/10/09 Page 33 Interconnexion / réseaux : mise en oeuvre Contexte cluster : on interconnecte les blocks 352 nœuds ( 8 cores/nœuds 36 Go /nœuds) ; 2816 cores Nehalem EP Quad-core - 2,8 Ghz technologie réseaux : infiniband 88 switchs Infiniband Stockage : 250 To Master IM2P2 - Calcul Scientifique 19/10/09 Page 34 Interconnexion / réseaux : protocoles Différents Réseaux / Protocoles d’interconnexion Source : Journées JoSy, Groupe Calcul CNRS, 13/09/2007 Lyon Master IM2P2 - Calcul Scientifique 19/10/09 Page 35 Interconnexion / réseaux TOP 500 Master IM2P2 - Calcul Scientifique 19/10/09 Page 36 Calcul Haute Performance : TOP 500 List Les plus grands systèmes de calcul actuellement : classement TOP 500 Juin 2008 Benchmark : Linpack (kw) Puissance Centrale nucléaire de 40 MW à 1450 MW Master IM2P2 - Calcul Scientifique 19/10/09 Page 37 Plan : • • • Les systèmes HPC – Typologie des systèmes : • Machines Mémoire partagée • Machines à Mémoire Distribuées • Machine NUMA – Exemples Architectures Processeurs HPC – Processeurs scalaires, superscalaires, vectoriels – Concepts d’optimisation Optimisation de codes – Technique d’optimisation – Compilo, librairies Master IM2P2 - Calcul Scientifique 19/10/09 Page 38 Architecture Processeurs : MIMD Processeurs Généralistes () Jeu d’instruction complexe : multimedia, add, mult,… Spécialisé Entiers Processeurs HPC () Jeu d’instruction simple : Mult., Add, Div., Sub. Spécialisé Flottants 64 bit 32 bit Exemple : Pentium IV Exemple : Itanium II 3,2 GHz Cache 500 ko 6,4 Gflop/s peak 1,5 GHz Cache 6 Mo 6 Gflop/s peak Linpack 0,7 Linpack 5,4 Gflop/s Gflop/s Temps de restitution 8 fois + rapide! Fondeurs : Intel (Itanium), AMD (Opteron), IBM (Power), SUN (UltraSparc) , NEC (Processeurs Vectoriels) Master IM2P2 - Calcul Scientifique 19/10/09 Page 39 Architecture Processeurs HPC Définition : cycle •Fréquence d’horloge = nombre d’impulsions par seconde •200 Mhz 200 Millions de cycles par seconde •Restitution d’une opération n cycles avec n 1 Spécificités processeur HPC: •Instruction Level Parallelism (ILP) : •Pipeline •multiple Functional unit (FPU) •Memoire Hierarchique •Accès mémoire rapide •Différents niveaux de cache L1, L2, L3 •Exécution Spéculative •Branch prediction •Prefetching Master IM2P2 - Calcul Scientifique 19/10/09 Page 40 Architecture Processeurs HPC Exemple schéma Architecture Proc. Superscalaire: Itanium Master IM2P2 - Calcul Scientifique 19/10/09 Page 41 Proc. Scalaire : Pentium 4 IA32 Master IM2P2 - Calcul Scientifique 19/10/09 Page 42 Architecture Processeurs HPC Objectif Pipeline 1 cycle = 1 résultat •Vision très schématique A1 = B1 + C1 load exec write 3 phases 1 phase/cycle Pipeline : exemple •3 Opérations indépendantes A1 = B1 + C1 A2 = B2 + C2 A3 = B3 + C3 Master IM2P2 - Calcul Scientifique 19/10/09 Page 43 Architecture Processeurs HPC Objectif Pipeline 1 cycle = 1 résultat A1 = B1 + C1 A2 = B2 + C2 A3 = B3 + C3 •Opérations indépendantes load Cycle 1 exec Load B1,C1 Cycle 2 Add B1,C1 Store in A1 Cycle 3 Cycle 4 write Load B2,C2 Add B2,C2 Résultats des 3 opérations : 9 cycles Store in A2 Load B3,C3 Cycle 8 Cycle 9 Cycles (Time) Add B3,C3 Store in A3 •Ressources « idle » Master IM2P2 - Calcul Scientifique 19/10/09 Page 44 Architecture Processeurs HPC Objectif Pipeline 1 cycle = 1 résultat A1 = B1 + C1 A2 = B2 + C2 A3 = B3 + C3 •Opérations indépendantes exec load Résultats des 3 opérations : 9 cycles Pipelining : Latence : 3 cycles 1 res/cycle write Cycle 1 Load B1,C1 Cycle 2 Load B2,C2 Add B1,C1 Cycle 3 Load B3,C3 Add B2,C2 Store in A1 Add B3,C3 Store in A2 Cycle 4 Store in A3 Cycle 5 Cycles (Time) Opérations indépendantes Exhiber le maximum d’opérations indépendantes alimenter Pipiline Master IM2P2 - Calcul Scientifique 19/10/09 Page 45 Architecture Processeurs HPC Plusieurs niveaux de pipeline : •Beaucoup d’opération atomiques (dépend micor-architecture, jeu instruction) : A1 = B1 + C1 load instruc. fetch decode instruc. exec exec write Mem Store ou load Write back Master IM2P2 - Calcul Scientifique 19/10/09 Page 46 Architecture Processeurs HPC longueur pipeline : Master IM2P2 - Calcul Scientifique 19/10/09 Page 47 Architecture Processeurs HPC Alimenter le processeur : Mémoire Hiérarchique Temps •Unité de Calcul « travaille » sur données dans les registres •Registre : taille très petite Mo Hit ? load B1 A1 = B1 + C1 yes no = miss •Cache ? load C1 •Coût n cycles Unité de Calcul « attend » n cycles Master IM2P2 - Calcul Scientifique 19/10/09 Page 48 Architecture Processeurs Plusieurs Niveaux de Cache : exemple processeur Itanium2 ® d ’INTEL ® Débits et Latences 1 cycle = 0,6 ns 2 cycles 256 ko 1.5-6 Mo-9 Mo 6.4 Go/s 32 Go/s L3U cache 16 Go/s 32 Go/s 12 cycles L2U cache 128 Integer Registers 128 FP Registers 16 Go/s L1D cache 16 ko 1 ko 1 ko 5 cycles 16Rd / 6Wr 32 Go/s 16 Go/s 5+1 cycles 12+1cycles Master IM2P2 - Calcul Scientifique Altix™: 145+ ns 19/10/09 Page 49 Architecture Processeurs Effet taille de cache : Master IM2P2 - Calcul Scientifique 19/10/09 Page 50 Architecture Processeurs HPC Exécution Spéculative : Alimenter le Pipeline If (cond1) then a1 = b1 + c1 … else a1 = b1 * c1 … End if « Casser » dépendances •Dépendances : •Branch prediction Cond1 a1 = b1 + c1,… •On « parie » Cond1 vraie •On calcule a1 = b1 + c1,.… •On vérifie plus tard …. Master IM2P2 - Calcul Scientifique 19/10/09 Page 51 Architecture Processeurs HPC Exécution Spéculative : Alimenter le Pipeline •Prefetching •Charger 1 instruction ET voisins mémoire • On remplit les registres Master IM2P2 - Calcul Scientifique 19/10/09 Page 52 Architecture Processeurs HPC Concepts : ILP, Pipeline, speculation : Mie en œuvre pour différentes micro-architectures (jeux d’instructions machine scalaire) x86 32 bit : Pentium (IA_32), Athlon AMD CISC : Complex instruction Set Computer Prix, mais 32 bit x86 : Xeon, Opteron (AMD) bon rapport prix/performance 32 et/ou 64 bit Pour le HPC RISC : Power6 Reduce Instruction Set Computer Puissance VLIW : Itanium Intel Bande passante mémoire Master IM2P2 - Calcul Scientifique 19/10/09 Page 53 Architecture Processeurs HPC Différentes approches : x86 vs. EPIC (Explicit Parallel Instruction Computing) Master IM2P2 - Calcul Scientifique 19/10/09 Page 54 Architecture Processeurs HPC Tendance Actuelle : processeurs multi-cœur (core) •Fondeurs : Intel, AMD, IBM, SUN(Sparc) Cache Cache Cache core core core Réduction taille gravure (45 nm) 1 processeurs mono-core 1 processeurs ( ou socket) multi-core (multi = 2, 4, 8 ) Plus de puissance BRUTE (2, 4, 8 ) Plus de mémoire Cache / core Meilleur ratio flop/watt, flop/m2 Même niveau fréquence, même concept architectural Adaptation carte mère débit vers la RAM Master IM2P2 - Calcul Scientifique 19/10/09 Page 55 Architecture Processeurs HPC TOP 500 Master IM2P2 - Calcul Scientifique 19/10/09 Page 56 TOP 500 : evolution processeurs Master IM2P2 - Calcul Scientifique 19/10/09 Page 57 Architecture Processeurs : Vectoriel Processeur Vectoriel opération sur vecteurs (non plus sur scalaire) : Single instruction multiple data (SIMD) Potentiellement très très puissant adaptation du code : meteo, Onera,etc… très très très cher NEC Peak Gflop Debit mémoire 100 Gflop/s 4TB/s TOP 500 Approche/ principe(SIMD) utilisé dans les architecture scalaire : X86 (32bit) SSE : Streaming SIMD Extension Altivec Superscalaire (2 FPU) Master IM2P2 - Calcul Scientifique 19/10/09 Page 58 Accélérer les processeurs Accélérateurs GP-GPU : General Purpose Graphic process Unit Adaptation des cartes graphiques Précision, compilateurs, langages (CUDA), etc… Stream processing (data centric process) Flop intensif (Double Precision ?) parallèlisme de données localité des données Futur : Intégration dans les processeurs GP-GPU Peak Gflop Debit mémoire Tesla (Nvidia) 500 Gflop/s 80GB/s Accélérateurs FPGA : Processeur reconfigurables (CRAY, SGI) CELL : 9 cores : 1 cpu + 8 SPE IBM Roadrunner Master IM2P2 - Calcul Scientifique 19/10/09 Page 59 Architecture Processeurs HPC • Comment on calcule le peak de perf. : – – Peak = Freq. * (Nbre opération par cycle) Nbre Opération par cycle : • • – Multicore : • – Combien de FPU ?(scalaire, super scalaire) Vectoriel Somme puissance core Exemple (itanium) • Fréquence : 1.5 Ghz, • Puissance crête : 6 Gflops/s : 1500 MHz * 2 madd/cycle 6 GFLOP/s Fréquence Processeurs Vectoriels (NEC) Peak Gflop Debit mémoire Byte/flop 100 Gflop/s 4TB/s 40 GP-GPU (Nvidia) 600 Mhz 500 Gflop/s 80 Gb/s 0,16 Itanium mono-core 1,5 Ghz 6 Gflop/s 6,4 Gb/s 1,06 Xeon Quad-Core 3 Ghz 40 Gflop 9,7 Gb/s 0,24 Xeon « NHM » 2,8Ghz 38Gflop 32 Gb/s 0,84 Power6 Bi-core 4,7 Ghz 36 Gflop ? Master IM2P2 - Calcul Scientifique 19/10/09 Page 60 Calcul Haute Performance : TOP 500 List Les plus grands systèmes de calcul actuellement : classement TOP 500 Juin 2008 Benchmark : Linpack (kw) Puissance Centrale nucléaire de 40 MW à 1450 MW Master IM2P2 - Calcul Scientifique 19/10/09 Page 61 Plan : • • • Les systèmes HPC – Typologie des systèmes : • Machines Mémoire partagée • Machines à Mémoire Distribuées • Machine NUMA – Exemples Architectures Processeurs HPC – Processeurs scalaires, superscalaires, vectoriels – Concepts d’optimisation Optimisation de codes – Technique d’optimisation – Compilo, librairies Master IM2P2 - Calcul Scientifique 19/10/09 Page 62 Optimisation de Codes Constat : efficacité des applications Ce qu’on observe : 10% du peak de performance processeur certaines applications font mieux…et d’autres beaucoup moins bien ! Des raisons avancées : instructions par cycles Architecture actuelle: 4 opérations par cycle (potentiel) Application (réalité): 1,2 -1,4 opérations restituées par cycle mémoire Comment optimiser au niveau des sources du code Master IM2P2 - Calcul Scientifique 19/10/09 Page 63 Optimisation de Codes Concepts Optimisation •tirer le meilleur de l’architecture processeur •Unrolling : Dérouler les boucles Pipeline et ILP •Blocking : Mémoire hiérarchique Alimenter processeurs •Compilateur « Doper » le code avec les librairies scientifiques , , IR; u, v, b IR n ; A IR nm , B IR mn , A IR nn u u Av + u C AB + C Au = b Au = u A = LU Master IM2P2 - Calcul Scientifique 19/10/09 Page 64 Optimisation de Codes Concept : Unrolling •Produit Matrice : C , A, B nn ; n = 500 C = A B •Option Compilation : -O1 le compilo traduit le pgm tel quel •Processeur Itanium 6Gflop/s Peak do i = 1, m do j = 1, n do k = 1, m A11 A12 A13 A21 A22 A23 A31 A32 A33 B11 B12 B13 B21 B22 B23 B31 B32 B33 = C11 C12 C13 C21 C22 C23 C31 C32 C33 c(i,j) = c(i,j) + a(i,k) * b(k,j) end do end do end do 347 Mflop/s Master IM2P2 - Calcul Scientifique 19/10/09 Page 65 Optimisation de Codes Concept : Unrolling •Produit Matrice : C = A B C , A, B n n ; n = 500 •Option Compilation : -O1 le compilo traduit le pgm tel quel do i = 1, m do j = 1, n do k = 1, m c(i,j) = c(i,j) + a(i,k) * b(k,j) end do end do end do 347 Mflop/s Unrolling do i = 1, m do j = 1, n do k = 1, m,8 s0= a(i,k) * b(k,j) s1= a(i,k+1) * b(k+1,j) s2= a(i,k+2) * b(k+2,j) s3= a(i,k+3) * b(k+3,j) s4= a(i,k+4) * b(k+4,j) s5= a(i,k+5) * b(k+5,j) s6= a(i,k+6) * b(k+6,j) s7= a(i,k+7) * b(k+7,j) c(i,j)=c(i,j)+s0+s1+s2+s3 end do end do end do itération s 454 Mflop/s (Gain 30%) Unrolling Tire bénéfice du pipeline et ILP Niveau Unrolling optim. : dépend architecture processeurs Master IM2P2 - Calcul Scientifique Cycles (Time) 19/10/09 Page 66 Optimisation de Codes Concept : Unrolling C = A B C , A, B nn ; n = 500 •Option Compilation (v8) : -O1 le compilo traduit le pgm tel quel do i = 1, m do j = 1, n do k = 1, m c(i,j) = c(i,j) + a(i,k) * b(k,j) end do end do end do do i = 1, m do j = 1, n do k = 1, m-4,4 s0= a(i,k) * b(k,j) s1= a(i,k+1) * b(k+1,j) s2= a(i,k+2) * b(k+2,j) s3= a(i,k+3) * b(k+3,j) c(i,j)=c(i,j)+s0+s1+s2+s3 end do end do end do do i = 1, m do j = 1, n do k = 1, m,8 s0= a(i,k) * b(k,j) s1= a(i,k+1) * b(k+1,j) s2= a(i,k+2) * b(k+2,j) s3= a(i,k+3) * b(k+3,j) s4= a(i,k+4) * b(k+4,j) s5= a(i,k+5) * b(k+5,j) s6= a(i,k+6) * b(k+6,j) s7= a(i,k+7) * b(k+7,j) c(i,j)=c(i,j)+s0+s1+s2+s3 end do end do end do 347 Mflop/s 396 Mflop/s Master IM2P2 - Calcul Scientifique 454 Mflop/s 19/10/09 Page 67 Optimisation de Codes Concept : Unrolling •Niveau Unrolling optimal : ? •dépend architecture processeurs (profondeur pipeline) •Pipeline vs. accès donnée Master IM2P2 - Calcul Scientifique 19/10/09 Page 68 Optimisation de Codes Concept : Blocking •Produit Matrice : n n C = A B C , A, B ; n = 1000 •Option Compilation : -O1 le compilo traduit le pgm tel quel •Processeur Itanium 6Gflop/s Peak do i = 1, m do j = 1, n do k = 1, m A11 A12 A13 A21 A22 A23 A31 A32 A33 B11 B12 B13 B21 B22 B23 B31 B32 B33 = C11 C12 C13 C21 C22 C23 C31 C32 C33 c(i,j) = c(i,j) + a(i,k) * b(k,j) end do end do end do 116 Mflop/s Master IM2P2 - Calcul Scientifique 19/10/09 Page 69 Optimisation de Codes Exemple : Blocking •Produit Matrice : C , A, B nn ; n = 1000 C = A B •Option Compilation : -O1 le compilo traduit le pgm tel quel • Taille des blocks : B1=50;B2=50;B3=50 B A j i Block B1=50;B2=50;B3=50 do i = 1, m,B1 do j = 1, n,B2 do k = 1, m,B3 do i1=i,min(i+B1-1,m) do j1 =j,min(j+B2-1,n) do k1=k,min(k+B3-1,m) c(i1,j1)=c(i1,j1)+a(i1,k1)*b(k1,j1) enddo end do end do enddo end do end do Master IM2P2 - Calcul Scientifique 19/10/09 Page 70 Optimisation de Codes Exemple : Blocking •Produit Matrice : C = A B C , A, B nn ; n = 1000 •Option Compilation : -O1 le compilo traduit le pgm tel quel B A Gain 300% j •Blocking : 379 Mflop/s i Block • Taille des blocks : B1=50;B2=50;B3=50 Master IM2P2 - Calcul Scientifique 19/10/09 Page 71 Optimisation de Codes Exemple : Blocking Temps Mo Blocking Tire bénéfice mémoire hierarchique Master IM2P2 - Calcul Scientifique 19/10/09 Page 72 Optimisation de Codes Exemple : Multiplication de Matrice C = A B C , A, B nn ; n = 1000 do i = 1, m do j = 1, n do k = 1, m c(i,j) = c(i,j) + a(i,k) * b(k,j) end do end do end do •En poussant le compilateur : •Opt= -O1 •Opt= -O2 Unrolling Pipelining ILP •Opt= -O3 Unrolling (+ agressif -O2) Pipelining (+ agressif -O2) ILP Modifs. Boucles Prefetching (Speculation) Master IM2P2 - Calcul Scientifique 19/10/09 Page 73 Optimisation de Codes Exemple : Multiplication de Matrice C , A, B nn ; n = 1000 C = A B •En poussant le compilateur : •Opt= -O1 116 Mflop •Opt= -O2 Unrolling Pipelining ILP •Opt= -O3 Unrolling (+ agressif -O2) Pipelining (+ agressif -O2) ILP Modifs. Boucles Prefetching (Speculation) 147 Mflop 4,2 Gflop/s Peak Itanium : 6 Gflop/s Master IM2P2 - Calcul Scientifique 19/10/09 Page 74 Optimisation de Codes Conclusions Compilateurs : •Compilateur : moins mauvais des optimisateurs de codes, mais ne fait pas tout •Bien coder pour faciliter le travail Compilo •Option -O3 sur les hot spots •Option –O3 pas forcement meilleur que -O2 Exécution Spéculative • Utiliser les librairies scientifiques •Les langages • procedural : •Fortran ,C do i = 1, m do j = 1, n •Pgm Objet : if (j==1) then • C++ …. endif end do end do Master IM2P2 - Calcul Scientifique 19/10/09 Page 75 Optimisation de Codes Langage ( C ) et Alignement mémoire : •On parcourt par ligne : n=5000; for (i=0;i<n;i++) { for (j=0;j<n;j++) { c[i][j]=i+j; } } 94 Mflop : •Compilation O1 •On parcourt par colonne : n=5000; for (j=0;j<n;j++) { for (i=0;i<n;i++) { c[i][j]=i+j; } } 34 Mflop : Master IM2P2 - Calcul Scientifique 19/10/09 Page 76 Optimisation de Codes Langage (Fortran) et Alignement mémoire : •On parcourt par ligne : n=5000 do j = 1, n do i = 1, n •Compilation O1 •On parcourt par colonne : n=5000 do i = 1, n do j = 1, n c(i,j) = real(i+j,kind=8); end do end do c(i,j) = real(i+j,kind=8); end do end do 36 Mflop 98 Mflop Master IM2P2 - Calcul Scientifique 19/10/09 Page 77 Optimisation de Codes : Librairies Librairies Scientifiques : Exemple routine DGEMM •DGEMM (Librairie BLAS: Basic Linear Algebra Subprogram) •D=Double, GE=General, MM=MatrixMultiplication C = A B + C =1 =0 C , A, B nn n = 5000 program prod_mat implicit none integer, parameter :: n=5000 real(kind=8), dimension(n,n) :: A,B,C …. … !C=A*B (C=1*A*B+0*C) call DGEMM('N','N',n,n,n,1.D0,A,n,B,n,0.D0,C,n) …. end program prod_mat Master IM2P2 - Calcul Scientifique 19/10/09 Page 78 Optimisation de Codes : Librairies Librairies Scientifiques : Exemple routine DGEMM C = A B + C •DGEMM (Librairie BLAS: Basic Linear Algebra Subprogram) •D=Double, GE=General, MM=MatrixMultiplication … !C=A*B =1 =0 C , A, B nn n = 5000 program prod_mat implicit none integer, parameter :: n=5000 real(kind=8), dimension(n,n) :: A,B,C …. … !C=A*B (C=1*A*B+0*C) call DGEMM('N','N',n,n,n,1.D0,A,n,B,n,0.D0,C,n) …. do i = 1, m do j = 1, n do k = 1, m C(i,j) = C(i,j) + A(i,k) * B(k,j) end do end do end do …. end program prod_mat 3 boucles Imbriquées (-O2) : 44 minutes !! DGEMM: 47 secondes!!! Master IM2P2 - Calcul Scientifique 19/10/09 Page 79 Optimisation de Codes : Librairies Librairies Scientifiques Parallélisées : Exemple routine DGEMM •Linkage avec version librairie Parallèle (MultiThreadé OpenMP) program prod_mat implicit none integer, parameter :: n=5000 real(kind=8), dimension(n,n) :: a,b,c …. … !C=A*B call DGEMM('N','N',m,m,n,1.D0,a,m,b,n,0.D0,c,m) …. On ne touche pas aux sources du code !! N=10000 Seq 2procs. 4procs. 8procs 16 procs 32 procs Temps sec. 365 181 95 54 34 38 Et avec les accélérateurs ? Master IM2P2 - Calcul Scientifique 19/10/09 Page 80 Optimisation de Codes : Librairies Exemple : Multiplication de Matrice •Opt= -O2 Unrolling Pipelining ILP •Opt= -O3 Unrolling Pipelining ILP Modifs. Boucles Prefetching (Speculation) 147 Mflop 4,2 Gflop/s •DGEMM Unrolling Blocking + -O3 5,2 Gflop/s Peak Itanium = 6 Gflop/s Master IM2P2 - Calcul Scientifique 19/10/09 Page 81 Optimisation de Codes librairies scientifiques (LIBRES!!): catalogue très riche •Librairies : •Algébre Linéaire •Solveur Directs, Itératif…. •FFT •…. •Librairies déjà Parallèlisées : •MultiTâche •Echange de Message (MPI) http://www.netlib.org/ , , IR; u, v, b IR n ; A IR nm , B IR mn , A IR nn u u Av + u C AB + C Au = b Au = u A = LU •Solveurs : •Solveur Direct parallèle (décomposition LU) : SuperLU, MUMPS •Solveur Itératif (Gradient Conjugué) : Petsc Master IM2P2 - Calcul Scientifique 19/10/09 Page 82 Optimisation de Codes Conclusion Optimisation de codes •Optimiser le Séquentiel •« Bien » coder, au sens compilo •Compilation, Architecture Processeur. •Analyser le code outil analyse section suivante •Librairies Scientifiques •Ultra optimisées •Parallèlisées •accélérées •Parallélisation •Multitâche : OpenMP •Echange de message : MPI Master IM2P2 - Calcul Scientifique 19/10/09 Page 83 Outils de développement (http://www.calmip.cict.fr/spip/rubrique.php?id_rubrique=34) Comment analyser un code Code Performance Temps •Temps restitution code : •Mesurer le temps de restitution %time ./a.out •flop/s ? (vs. peak proc.) : • Mesurer la perf de l’application •real 1m32.029s temps de restitution •user 1m30.177s temps effectif CPU •sys 0m0.736s temps système •Analyse fine code // •Où passe-t-on du temps dans le code ? : •Temps routines •Temps par lignes Master IM2P2 - Calcul Scientifique 19/10/09 Page 84 Outils de développement Profiling : Où passe-t-on du temps dans le code % histx -f -l -o out_histx ./a.out % iprep < out_histx.a.out.29591 > prof.out % cat prof.out Temps en micro sec. Functions sorted by count Nom routine ========= ====== == ==== Count Self % Cum. % Name -------------------- ------- ------- -------------------381 72.989 72.989 libscs.so:__scsl_dgemm_hoistc_ 122 23.372 96.360 a.out:MAIN__ [test_dgemm.f90:9] 11 2.107 98.467 libscs.so:__scsl_dgecpy_at_ 8 1.533 100.000 libscs.so:__scsl_dgemm1_ Source lines sorted by count ====== ===== ====== == ==== Count Self % Cum. % Name -------------------- ------- ------- -------------------41 32.283 32.283 [test_dgemm.f90:50] (a.out) 37 29.134 61.417 [test_dgemm.f90:44] (a.out) 27 21.260 82.677 [test_dgemm.f90:56] (a.out) 9 7.087 89.764 [test_dgemm.f90:57] (a.out) 7 5.512 95.276 [test_dgemm.f90:45] (a.out) 6 4.724 100.000 [test_dgemm.f90:51] (a.out) Master IM2P2 - Calcul Scientifique Fichier:ligne 19/10/09 Page 85 Outils de développement Outil mesure de performance • Exemple : utilisation du cache L3 et des debits des accès en mémoire % lipfpm -e FP_OPS_RETIRED -e L3_READS.DATA_READ.ALL -e L3_READS.DATA_READ.MISS ./a.out lipfpm summary ====== ======= Retired FP Operations...................................... 152499228205 L3 Reads -- L3 Load References ........................... 2499734811 L3 Reads -- L3 Load Misses ............................... 1712387197 CPU Cycles................................................. 348636126093 Average MFLOP/s............................................ 656.12 Average data read MB/s requested by L3..................... 817.303 (Retired FP Operations/ CPU Cycles)*Freq = flop/s Master IM2P2 - Calcul Scientifique 19/10/09 Page 86