Module EN1 - Composants de base de l`électronique Travaux Dirigés

Module EN1 - Composants de base de l’´electronique

Travaux Dirig´es

´

Eric PERONNIN

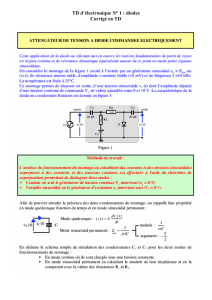

VeVpVe(t) = Ve1(t) = Ve2(t) = Veef f .√2.sin(ω.t)

Vp(t) = Vpef f .√2.sin(ω.t)

Veef f = 12v Vpef f = 240v R = 15Ω ω= 2.π.F F = 50Hz

D

RVe Vs

I

V

D

D

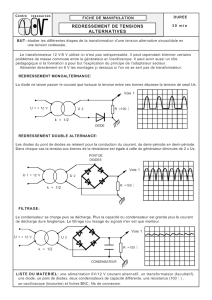

D1

Vp

I

Vs

V

D1

R

T1

2 6

9

7

104

D2I

V

D2

D1

D2

Ve1

Ve2

(c)

(b)(a)

Ip

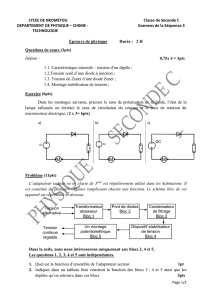

D1

R

V

Ie

D4

D3

D2

Ve Vs

D1

V

V

V

D2

D3

D4

I1

I2

I3

I4

Is

VDIDVsIsVeIe

VsIs

VDID

VRM ˆ

ID

< ID> IDef f

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

0 0.005 0.01 0.015 0.02

−20

−15

−10

−5

0

5

10

15

20

Vsmin

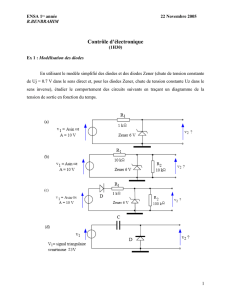

Ve(t) = Veef f .√2.sin(ω.t)

Veef f = 12v R = 15Ω ω= 2.π.F F = 50Hz

C= 47µF C = 470µF C = 4700µF

D

R

I

V

D

D

VsVe

Ic Is

C

t= 0

Ic(t)Is(t)ID(t)

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

1

/

18

100%