Annale 2009 - Annales-Exam

Architecture des Machines NFA004 TO-HTT - Première session 2008-2009

Le CNAM le 13 février 2009

MINISTERE DE L'ÉDUCATION NATIONALE

CONSERVATOIRE NATIONAL DES ARTS & MÉTIERS

Architecture des machines

NFA004

Première session TO - HTT

(Sur 15 points)

Tous documents et calculatrice autorisés

Durée : 2 heures

18h00 – 20h00

Amphi G Friedmann

Enseignant responsable : Joëlle Delacroix

1

Annales-exam.com

Architecture des Machines NFA004 TO-HTT - Première session 2008-2009

Merci de soigner votre copie

Bon courage.

I/ Représentation des informations (5,5 points)

Question 1 (2,75 points)

Donnez la représentation de + 754 et – 1352

a/ en considérant une représentation des nombres signés en complément à 2 sur 16 bits ;

b/ en considérant une représentation des nombres signés en valeur signée sur 16 bits.

Exprimez le résultat en base 8 dans chaque cas.

Question 2 (1,75 points)

On considère une représentation des nombres flottants en Simple Précision selon le format IEEE

754, soit 1 bit de signe, 8 bits d'exposant avec un excédent à 127 et 23 bits de mantisse. Quelle

est la valeur décimale du nombre flottant codé en interne par la chaîne (C4642A50)16

Question 3 (1 point)

Soit la chaîne suivante 1010101011010011

a/ Donnez sa valeur décimale en considérant qu'elle est la représentation d'un nombre signé

selon le format de la valeur signée.

b/ Donnez sa valeur décimale en considérant qu'elle est la représentation d'un nombre signé

selon le format du complément à 2.

II/ Entrées-sorties et langage d’assemblage (6 points)

On considère une machine pour laquelle l’adressage de l’unité d’échange gérant le clavier

s’effectue dans un espace d’adressage séparé. Le processeur dispose de registres banalisés de 4

octets.

Question 1 (1,5 points)

L’unité d’échange du clavier comporte un registre d’état et un registre de données, dont les

adresses sont respectivement nommées R_CLAVIER_ETAT et R_CLAVIER_DONNEE. Ces

registres sont de 4 octets chacun.

Cette unité d’échange signale au processeur qu’une donnée est disponible dans son registre de

donnée en envoyant une IRQ de numéro 2 au processeur.

Donnez le code de la routine d’interruption IRQ2 qui permet de lire le contenu du registre de

données de l’unité d’échange du clavier dans un registre banalisé R3 du processeur.

2

Annales-exam.com

Architecture des Machines NFA004 TO-HTT - Première session 2008-2009

Question 2 (4,5 points)

Soient la suite d'instructions d'un programme en assembleur et l'état de la mémoire centrale au

moment de l'exécution de ces instructions.

Le registre de base RB contient la valeur 40. Le registre R3 est chargé par la routine d’IRQ2 de la

question précédente. Le processeur manipule des entiers signés sur 32 bits selon le format du

complément à 2. Toutes les valeurs d’adresse ou de nombres sont données en base 10.

LOAD D R1 100

LOAD I R2 112

PUSH Rg1 R3

NEG Rg1 R3

TOUR : ADD Rg2 R1 R3

ADD Im R2 -1

JMPZ SUITE

JMP TOUR

SUITE : ADD Rg2 R1 R3

JMPN NEG

JMPP POS

NEG : PUSH Rg1 R1

STOP

POS : ADD B R1 60

PUSH Rg1 R1

PUSH Rg1 R2

STOP

100

104

108

112

116

120

adresse mot mémoire

(base 10, les mots font 4

octets)

RSP

150

154

158

162

164

16

3

1

0

4

6

6

a/ Donnez pour chaque instruction du programme, l’action réalisée. (2 points)

b/ A l’issue de l’exécution du programme, donnez la configuration de la pile dans chacun des

trois cas suivants. (2,5 points)

1/ le registre R3 est chargé avec la valeur 6 ;

2/ le registre R3 est chargé avec la valeur 2 ;

3/ le registre R3 est chargé avec la valeur 4.

III/ Micro instructions et cache (3,5 points)

Question 1 (2 points)

Soit une mémoire centrale de 2 Gigamots, composée de mots de 16 bits, le bit de poids faible de

l’adresse donnant la position d'un octet dans le mot.

3

Annales-exam.com

Architecture des Machines NFA004 TO-HTT - Première session 2008-2009

On désire réaliser une mémoire-cache pour améliorer les performances d'un processeur disposant

de cette mémoire centrale, en lui ajoutant un dispositif de mémoire cache travaillant par blocs de

8 mots de 16 bits et de capacité utile de 256 K-octets.

Quelle est la taille réelle de ce cache à correspondance directe ?

Question 2 (1,5 points)

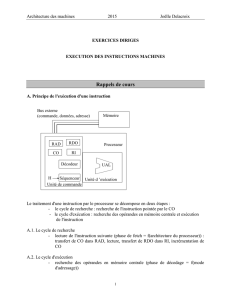

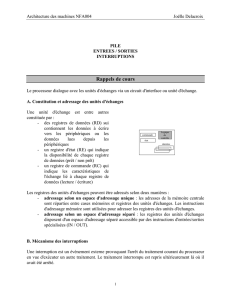

On considère l'architecture de processeur jointe. Les registres du processeur sont sur 32 bits. Les

portes à activer sont représentées par un rond sur la flèche.

Le format des microcommandes est :

- entrée du contenu d'un bus vers un registre : nombusnomregistreEn (exemple

AtamponAEn)

- sortie du contenu d'un registre vers un bus : nombusnomregistreSor (exemple

BCOSor)

- entrée sur une entrée de l'UAL@ : nombusentréeUAL@En ou

nomregistreentréeUAL@En (exemples RBUal@aEn, AUal@bEn)

- sortie des UAL : nombussortieUALSor et nombussortieUAL@Sor (exemple

BualsSor)

Le passage du bus A vers le bus B s'effectue en activant une opération Nop sur l'Unité

Arithmétique et Logique (UAL), ce qui a pour effet de copier le contenu du tampon A sur la

sortie de l'Ual. Ainsi pour passer le contenu du bus A au bus B, les étapes sont :

- mettre le contenu du bus A dans tampon A : AtamponAEn ;

- activer l’opération Nop : Nop ;

- sortir la sortie de l’Ual sur la bus B : BualsSor.

Les microcommandes LEC et ECR permettent la lecture et l’écriture de la mémoire centrale.

Pour incrémenter le compteur ordinal CO, vous utiliserez l’UAL@ en activant l’opération Inco.

Donnez la séquence de microcommandes correspondant à l'instruction NEG Rg1 R3 qui effectue

le calcul du complément à 2 du registre R3 et stocke le résultat dans R3.

°° °

re g i st r e s g é n éra u x

tamp on A tampon B

UAL

CO

R.I

R0 R15

RDO

RAD

b

u

s

m

é

m

o

i

r

e

P

S

W

bus B

bus A

RB

UA L @

Nop

Neg

Inco

add

ab

s

ab

s

4

Annales-exam.com

1

/

5

100%