Et maintenant : l`assembleur 80x86

Et maintenant :

l’assembleur 80x86

Architecture des ordinateurs – p. 1

Les registres (1)

Les registres sont des «variables» du

processeur, dont le nom est fixé.

Appartenant au CPU, leur utilisation est très

rapide (beaucoup plus que la mémoire

centrale).

Sur les 80x86, on en distingue plusieurs types :

Les registres généraux

Les registres d’index

Les registres de segment

Les registres MMX et SSE

...

Architecture des ordinateurs – p. 2

Les registres (2)

Nous reverrons chacun des registres dans leur

usage propre par la suite. La présentation

« détaillée » suivante n’a pour but que de vous

présenter les noms que vous allez rencontrer

très rapidement en TP.

Retenez cependant l’usage principal de

chacun de ces registres.

Architecture des ordinateurs – p. 3

Les registres (3)

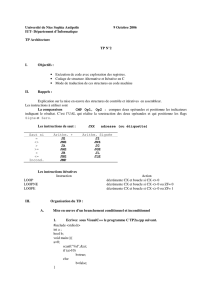

EAX (32 bits) AX (16 bits) Accumulateur

AH (8 bits) AL (8 bits)

EBX (32 bits) BX (16 bits) Base

BH (8 bits) BL (8 bits)

ECX (32 bits) CX (16 bits) Compteur

CH (8 bits) CL (8 bits)

EDX (32 bits) DX (16 bits) Données

DH (8 bits) DL (8 bits)

EDI (32 bits) Destination Index

ESI (32 bits) Source Index

ESP (32 bits) Pointeur de pile

EBP (32 bits) Pointeur de base

Architecture des ordinateurs – p. 4

Les registres (4)

Si EAX contient (en hexa) 0xA512E6FF (32 bits = 4 octets = 1

double-mot (dword)), alors :

AX contient 0xE6FF (16 bits = 2 octets = 1 mot (word))

AH contient 0xE6 (8 bits=1 octet (byte))

AL contient 0xFF (8 bits = 1 octets (byte))

Ce comportement est identique pour les registres EBX, ECX et

EDX. Il s’agit d’un héritage des premiers processeurs Intel 80x86,

qui fonctionnaient en 8 bits puis en 16 bits.

Certains processeurs Intel ou AMD récents (Intel Itanium, AMD

Opteron) fonctionnent en 64 bits, ainsi que les processeurs plus

anciens Sun UltraSparc, DEC Alpha, ...

Architecture des ordinateurs – p. 5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

1

/

86

100%