Contrôle périodique

Contrôle périodique — INF1600 —Hiver 2012 1/4

Contrôle périodique

INF1600 — Architecture des micro-ordinateurs

Département de génie informatique

École Polytechnique de Montréal

Hiver 2012

Enseigné par : François-Raymond Boyer (coordonnateur)

Giovanni Beltrame

Date : Jeudi 15 mars 2012

Durée : de 18h00 à 20h00

Documentation : Toute documentation raisonnable permise

Calculatrice : Aucune calculatrice permise

Format : 4 questions (13 sous questions) sur 4 pages

Total possible de 21 sur 20 points

Directives : Répondre dans le cahier d’examen.

Vous n’avez pas à remettre le questionnaire.

Contrôle périodique — INF1600 —Hiver 2012 2/4

Question 1 Architecture (9 points)

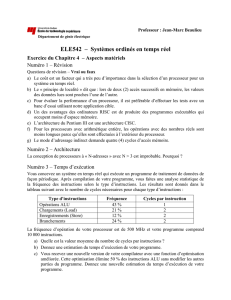

Pour permettre d’exécuter une plus grande partie des instructions de l’IA-32, nous avons ajouté H à

l’architecture du devoir 1 : (les fils de contrôles ne sont pas dessinés, pour la clarté)

Q

Q

SET

CLR

DIR

32

+

Q

Q

SET

CLR

DEIP

mux

A4

Mémoire1

Donnée

Adresse

IRá23..0ñ

UAL

Mémoire2

Donnée

Adresse

Registres

[0..7]

(soit eax,

ebx, …)

Q

QSET

CLR

D

T

IRá12..0ñ

C

IRá14..13ñ

mux

B

IRá17..15ñ

IRá20..18ñ

IRá23..21ñ

DE

F

0

1

2

0

1

Circuit de

contrôle IRá31..24ñ

lecture

écriture

X Y

G

mux

H

0

1

L’UAL permet entre autres les opérations suivantes (écrit comme « contrôlesortie de l’UAL ») :

0X : 1Y : 2X + Y : 3X Y : 4X << Y : 5X >> Y ; 6Y + 4 : 7Y 4 : …

Et les registres sont numérotés (numérotation différente de celle du devoir 1) :

eax:=R[0] : ebx:=R[1] : ecx:=R[2] : edx:=R[3] : esi:=R[4] : edi:=R[5] : ebp:=R[6] : esp:=R[7]

Soit l’instruction IA-32 « JMP *16(%eax,%ebx,8) » ( pour les sous-questions a), b), c) et e) );

a) [1 pt] Donnez le RTN abstrait pour cette instruction.

b) [1 pt] Indiquez comment pourrait être codée en langage machine, sur cette architecture, une

instruction qui fait cette opération. C’est-à-dire de donner la valeur, dans la base de votre choix,

pour chacun des champs de IR que vous pouvez.

c) [3 pts] Donnez le RTN concret effectuant cette opération, en supposant que IR contient bien

l’instruction b). Donnez le cas général, avec les IRá…ñ, pas le cas spécifique pour les

registres/constantes spécifiés. Effectuez-le en le moins de cycles possibles.

d) [2 pts] Indiquez les signaux de contrôle pour « A, B, C, D, E, F, G, H, UAL, écrireEIP, écrireIR,

écrireT, écrireRegistre » (les signaux « read/write » et « enable » de Mémoire2 étant liés de

manière logique avec F et G, et la Mémoire1 étant toujours active en lecture) pour chaque cycle,

pour le RTN concret « T 8 ; EIP edx + T : T edx + T ; ecx Mémoire2[T] :

IR Mémoire1[EIP] ; ebx T >> 3 », en supposant qu’au départ IR=0x004C0008 et qu’après

son écriture, IR contient : IRá12..0ñ=3 : IRá14..13ñ=0 : IRá17..15ñ=0 : IRá20..18ñ=0 :

IRá23..21ñ=1. (Le but est de vérifier que vous savez générer les signaux pour un RTN concret

quelconque; il ne correspond pas à une instruction qui a du sens)

e) [2 pts] L’architecture ne peut pas exécuter des branchements relatifs avec des opérandes (c.-à-d.

EIP = EIP + valeur dans un registre). Proposez comment modifier l’architecture, en essayant de

minimiser la taille des modifications, pour pouvoir exécuter ce genre d’instruction. Expliquez

clairement comment l’opération sera effectuée sur votre architecture modifiée.

Contrôle périodique — INF1600 —Hiver 2012 3/4

Question 2 Lecture d’assembleur (4,5 points)

Soit l’extrait de programme suivant, pour un processeur de la famille x86 (IA-32) :

.data

debut_data:

.equ c, b - a

a:

.int b

.byte 012, 16, 0x10, 0b100

b: .word -4

.balign 4

.byte 1

fin_data:

.text # Adresse à laquelle se trouve chaque

instruction :

main: mov 0x1003, %ebx # 0x2000

mov a, %ecx # 0x2006

mov (%ecx), %bl # 0x200C

mov $0x12345678, %eax # 0x200E

mov $0x100, %edx # 0x2013

mul %edx # 0x2008

mov $-2, %esi # 0x201A

mov b(%esi), %esi # 0x201F

mov $2, %edi # 0x2025

lea b-8(,%edi,2), %edi # 0x202A

mov $0b101010010,%eax # 0x2031

sub $0b10010100,%al # 0x2036

call ici # 0x2038

ici: pop %ebp # 0x203D

ret # 0x203E

# 0x203F

a) [1 pt] Donnez la valeur de chaque octet en mémoire à partir de l’adresse debut_data (incluse), jusqu’à

l’adresse fin_data (non incluse), en hexadécimal. Si debut_data vaut 0x1000, quelles sont les

valeurs associées à a, b, c et fin_data, dans la base de votre choix?

b) [2,5 pt] Donnez les valeurs de %ebx, %ecx, %edx, %esi, et %edi (dans la base de votre choix) après

l’exécution de la routine main (appelée en utilisant l’instruction « call main »).

c) [1 pt] Donner, sous forme binaire, le contenu du registre %eax suite à l’exécution de l’instruction de

soustraction, ainsi que la valeur des bits CF et OF du registre eflags. Montrez d’où proviennent

les bits CF et OF dans votre calcul et ce qu’ils signifient.

Contrôle périodique — INF1600 —Hiver 2012 4/4

Question 3 Écriture d’assembleur (3,5 points)

Soit le fichier C suivant :

float b;

int fun2(unsigned int x, float y);

int fun(unsigned int* ptr, unsigned int j, float d)

{

unsigned int res, i;

res = 0;

for(i = ptr[j+1]; i < j; ++i) {

res++;

b = b + d;

}

return fun2(res, b);

}

Traduire la sous-routine fun du C à l’assembleur; faites bien attention aux types des variables utilisées.

Indiquez à quoi sert chaque instruction assembleur, par rapport au code C. Votre programme devrait être

raisonnablement efficace (pas trop d’instructions).

Notez que l'instruction PUSH ne prends pas un registre à virgule flottante (%st(--)) comme opérande.

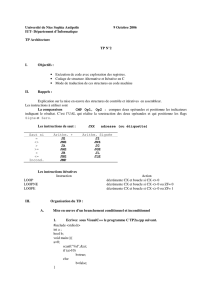

Question 4 Intro (4 points)

Donnez des réponses courtes et précises.

a) [1 pt] Quelle est la différence fondamentale dans la manière de transmettre les informations sur un bus

ATA (16-bits) et un bus PCIe x16 (16-bits) ?

b) [1 pt] À quoi sert l'état à haute impédance d'un buffer à trois états? Donnez un exemple de problème

possible en absence de cet état.

c) [1 pt] Sur un disque rigide standard (à une tête par surface), pourquoi le premier secteur d’un cylindre

n’est pas aligné avec le premier secteur du cylindre précédent? (Le premier secteur d’un

cylindre est celui duquel on doit lire les données en premier, pour faire une lecture séquentielle

des informations.)

d) [1 pt] Pour quelle(s) valeur(s) de A,B,C la sortie sera à Z (haute impédance)? (où +V vaut la valeur

logique 1, et la mise à la terre vaut la valeur logique 0) :

+V

Sortie

A

C

B

+V

1

/

4

100%