Architecture des ordinateurs Structure du cours

2006/2007 Licence Informatique L3 1-1

Cours du 29 septembre 2006

Architecture des ordinateurs

Cours (12x2h00) :

♦Frédéric Mallet - fmallet@unice.fr

TP (12x2h00 - 2 groupes) :

♦Jean-Pierre Lips - [email protected]

♦Christophe Delage –

http://deptinfo.unice.fr/~fmallet/archi

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-2

Structure du cours

♦

Performances : évolution et comparaison

♦

Codage de l’information

♦

Fonctions logiques et éléments mémoires

♦

Systèmes à microprocesseurs

♦

La famille Intel - 80x86

♦

Le PowerPC d’IBM

♦

Éléments avancés (parallélisme, mémoire, ...)

♦

Conception d'architectures numériques - VHDL

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-3

Facteurs d'Évolution des performances

♦

Technologie :

Tubes à vide (46-57), transistors (58-64), SSI-MSI (65-

71), LSI (72-77), VLSI(78-?)

♦

Densité : nombre de transistors sur une zone de

silicium ( < 0.1µm)

Loi de Moore : + 50% par an depuis 1980

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-4

Illustration de la loi de Moore

http://www.intel.com/research/silicon/mooreslaw.htm

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-5

♦

Technologie

♦

Densité

♦

Vitesse : rapidité des portes logiques et mémoires

augmente en moyenne de 13% par an

♦

Surface : taille physique du + grand circuit intégré

... mais aussi

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-6

Surface et wafer

30 cm de diamètre 1 circuit intégré

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-7

Comparaison de performances

♦

Performance = terme très vague

le plus souvent associé à la rapidité

plusieurs métriques pour décrire les systèmes et

sous-systèmes

♦

compromis avec la facilité de programmation

Architectures orthogonales (RISC)

• Faciles à programmer, mais moins optimisées

Architectures optimisées (DSP)

• Très optimisées, moins faciles à programmer

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-8

MIPS / FLOPS

♦

2 unités fréquemment utilisées :

Mips : Million d ’Instructions Par Seconde

Flops : FLoating-point Operations Per Second

♦

Problème

Suivant le système, on a un nombre différent

d ’instructions pour la même tâche

Compare 2 implémentations sur le même système

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-9

CPI/IPC

♦

CPI = nbre de cycles pour chaque instruction

♦

IPC = nbre d'instructions par cycle

CPI = 1/IPC

♦

Ces métriques ne donnent pas de temps

d'exécution mais sont très utiles en simulation

♦

On multiplie par la période d'horloge pour

obtenir un temps

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-10

Banc d'essai (benchmark)

♦

Série de programmes représentatifs d'une

famille d'applications donnée

♦

SPEC : Standard Performance Evaluation

Corporation - http://www.spec.org

SPEC CPU2000 = CINT2000 + CFP2000

serveur web, graphique, unités de stockage

Temps d'exécution total ≠MIPS ou IPC

Tous les constructeurs utilisent les mêmes tests

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-11

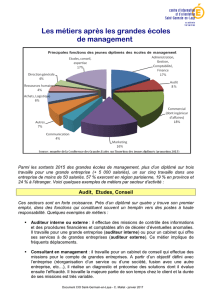

CINT2000

♦

Calculs intensifs sur les entiers

164.gzip Compression

175.vpr FPGA Placement et routage

176.gcc Compilateur C

181.mcf Optimisation combinatoire

186.crafty Echecs

197.parser Traitement de texte

252.eon Visualisation C++

253.perlbmk PERL

254.gap Interpréteur, théorie des groupes

255.vortex Base de données, OO

256.bzip2 Compression

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-12

Moyennes arithm

é

tiques et

géométriques

♦

Moyenne arithmétique de n entiers

Somme des entiers divisée par n

e.g. (4+2+4+82) / 4 = 23, (8+8+8+8)/4 = 8

♦

Moyenne géométrique de n entiers

Racine nième du produit des entiers

e.g.

Moins sensible aux valeurs accidentelles

16,782424

4

=×××

88888

4

=×××

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-13

Le monde du numérique

signal logique et mot

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-14

Numérique ou analogique ?

♦

Analogique :

Échelle continue de valeurs => sensible au bruit

♦

Numérique :

Échelle discrète de valeurs : binaire, ternaire, ... ?

BInary digiT = BIT (0 ou 1) : valeurs logiques

émetteur

+Vcc

0

V

sup

V

inf

1

0

récepteur

+Vcc

0

V

sup

V

inf

1

0

V

Ssup

> V

Esup

V

Sinf

< V

Einf

+Vcc

0

V

Ssup

V

Sinf

1

0

+Vcc

0

V

Esup

V

Einf

1

0

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-15

Mots de bits

♦

1 signal logique représente 2

1

valeurs : bit

♦

N signaux représentent 2

n

valeurs : mot

♦

8 signaux représentent 2

8

=256 valeurs : octet

♦

Codage binaire naturel : entiers non signés

bits ordonnés de 0 à n-1 (de droite à gauche)

Le i

ème

chiffre pèse 2

i

:

(e.g. 0b100111)

En décimal, le i

ème

chiffre pèse 10

i

:

• 1995 = 1.10

3

+9.10

2

+9.10

1

+5.10

0

∑

−

=

1

0

2

*

n

i

i

i

b

∑

−

=

1

0

10

*

n

i

i

i

b

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-16

Généralisation en base b

♦

Exemple : Base 2

N = an bn + an-1 bn-1 + ..... + a1 b1+ a0

b0

Poids fort Poids faible

1010 = 1.23 + 0.22 + 1.21 + 0.20

1010 = 10102

Indique la base

ai bi

Poids de ai

Rang de ai

ai = 0 ou 1 => bit

base

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-17

Numération Octale et Hexadécimale

♦

Octale : 8=2

3

symboles 0, 1, 2, 3 ... 7

♦

Hexadécimale : 16 symboles 0,1,2,3 ...9,A,B,C,D,E,F

Passage de la base 10 à la base 8 ou 16

• divisions successives par 8 ou 16

Passage de la base 2 à la base 8 ou 16

• décomposition en groupe de 3 ou 4 bits

• remplacement de chaque groupe par sa valeur dans la

nouvelle base

Exemples : 1011101,01101

2

1 011 101,011 010

Base 8 = 135,328

101 1101,0110 1000

Base 16 = 5D,6816

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-18

Partie fractionnaire (virgule fixe)

♦

(0,572)

10

= 5*10

-1

+7*10

-2

+ 2*10

-3

♦

(0,011)

2

= 0*2

-1

+1*2

-2

+ 1*2

-3

♦

(0,b

-1

b

-2

...b

-n

)

B

= b

-1

*B

-1

+ b

-2

*B

-2

+ ... + b

-n

*B

-n

où 0 ≤b

-i

< B, ∀i

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-19

Passage de la base 10 à la base 2

20 2

0 10 2

0 5 2

1 2 2

01 2

1 0

Bit poids faible

Bit poids fort

2010 = 101002

♦

Partie entière : divisions successives par 2

♦

Partie fractionnaire : multiplications successives par 2

0,375 * 2 = 0, 75

0,75 * 2 = 1, 5

0,5 * 2 = 1

0,37510 = 0.0112

20,37510 = 10100.0112

2006/2007 Architecture des Ordinateurs - Licence Informatique L3

Frédéric Mallet 1-20

Signe/valeur absolue

♦

Le signe a 2 valeurs possibles (+ ou - ) : 1 bit

Le bit de poids fort code le signe

les autres bits représentent la valeur absolue

e.g.

• 0b00001100 représente la valeur +12

• 0b10001100 représente la valeur -12

Avec n bits on représente les valeurs

• de – (2n-1-1) à +(2

n-1

-1)

♦

2 problèmes

Comment coder 0 ?

Circuits spéciaux pour les opérations arithmétiques (cf. TP)

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

1

/

23

100%