Architectures des ordinateurs

Architectures*des*ordinateurs*

*

1) organisation minimale d’un ordinateur

2) le processeur

3) la mémoire

4) le programme

5) les interfaces

Sommaire*

*

3*

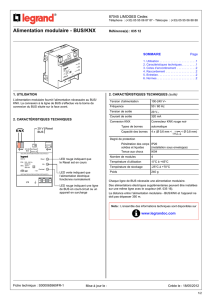

Génération horloge

Microprocesseur

Mémoire

RAM$

ROM

Décodage d’adresses

Interfaces périphériques

Initialisation

Bus$adresses

Bus$données

Lignes$de$

contrôle

ENVIRONNEMENT

organisation minimale d’un ordinateur

le système minimal

- le circuit d’horloge et circuit d’initialisation (reset)

- la mémoire principale

- le processeur ou CPU

- le décodeur d’adresses

- le bus d’adresse et bus de données

- le bus de contrôle

- les périphériques

5*

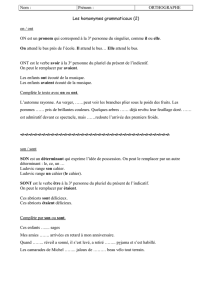

C4 10nF

/reset

sck

MISO

AT90S85 35

U6

AT90S8535

pb0-T0

1

pb1-T1

2

pb2-Ain0

3

pb3-Ain1

4

pb4-ss/

5

pb5-mos i

6

pb6-miso

7

pb7-sck

8

res et/

9

vcc

10

gnd

11

xtal2

12

xtal1

13

pd0-rxd

14

pd1-txd

15

pd2-int0

16

pd4-oc1b

18 pd3-int1

17

pd5-oc1a

19

pd6-icp

20 oc2-pd7 21

pc0 22

pc1 23

pc2 24

pc3 25

pc4 26

pc5 27

tosc1-pc6 28

tosc2-pc7 29

avcc 30

agnd 31

aref 32

adc7-pa7 33

adc6-pa6 34

adc5-pa5 35

adc4-pa4 36

adc3-pa3 37

adc2-pa2 38

adc1-pa1 39

adc0-pa0 40

Y1

4Meg

C1

22pF

C2

22pF

+5V

SW1

Reset BUTTON

R2 10k

D1

1N914

Exemple$de$circuits$de$reset$et$de$génération$d’horloge

circuit d’horloge et circuit de reset

Reset: activé tant que l’alimentation n’est pas stabilisée : réseaux RC

ou circuits spécialisés

Horloge (Quartz ou quartz + PLL): fixe le rythme d’exécution

des instructions

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

1

/

33

100%