Modules MAOA Projet 1 Cadre global du sujet

G= (V, A)a A

uv u a v P

(a1=u1u2, a2=u2u3, ..., al=ul−1ul)u1=ulP

W⊂V A(W)A

W G(W)=(W, A(W)

W

v∈V δ−(v)v δ−(v)

v d−(v) = |δ−(v)|d+(v) = |δ+(v)|

v

OiEi

Si

Ei

Vp={p1, ..., pn}Vo={o1, ..., om}

ojj∈ {1, ..., m}Ei

SiEi6=∅Si6=∅

PIN ⊂Vp

Vp\PIN |PIN |

V=Vp∪Vo

A oi∈Voi∈ {1, ..., m}

poip∈Eioip0

p0∈SiGC= (V, A)

p2PIN

p1o2o1

(o3, o1, o4, o8, o7, o5, o6)

o2o6

o2

PIN |PIN |= 9

o1

|PIN |= 7

G

Wo⊂VoH= (Wo∪Vp, A(Wo∪Vp))

m n M ≤n

oi|Ei| ≥ 1

|Si|>1|Ei|+|Si|< M

Ei|Ei|Si|Si|

EioioiSi

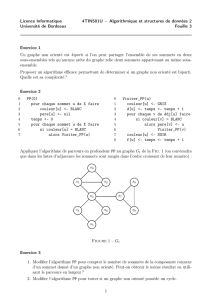

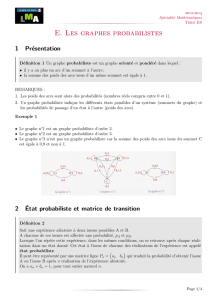

G= (V, A)V A

uv A u v G

P= (u0u1, u1u2, ..., uk−1uk)P k C

G u0=ukV(P)V(C)

W⊂V

A(W)W

(W, A(W)) W

(W, A(W)) G|W|

xi∀i∈V i

•

G= (V, A)u∈V

(PC)

Max X

u∈V

x(u)

u1= 1,

2≤ui≤n i 6= 1,

ui−uj+ 1 ≤n(2 −xi−xj)i6= 1, j 6= 1,

ui∈IR i,

0≤x(u)≤1∀u∈V

x(e)∀u∈V.

•

G= (V, A)u∈V

(PE)

Max X

u∈V

x(u)

6

6

1

/

6

100%