Diaporama de présentation de l`architeture

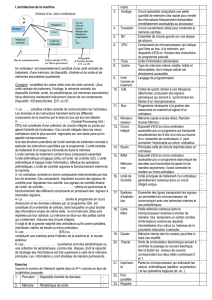

Les processeurs

Notion de langage informatique

Programme :

Ensemble d’instructions permettant

àun ordinateur d’exécuter une

suite d’opérations déterminées.

Analogie : Ensemble de trous sur la

bande perforée d’un orgue de

Barbarie.

Langage informatique

Approximation :

Langue écrite compréhensible

par le programmeur et

l’ordinateur

Programme

=

Logiciel

=

Software

=

Application

Langage machine

100010110100011011111100

000000110011010011111010

100010010100011011111110

x=a+b

80x86 Intel

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

1

/

25

100%