Système slow-control au LAPP Priorité n°1

Système slow-control au LAPP

Priorité n°1 : bien comprendre les limites

du système slow-control sécurité

–Pour la partie lecture (capteurs) -> pas de

problèmes fondamentaux

•Sérialisation des capteurs (One Wire)

•1 entrée par capteur directement connecté au FPGA ou

via un ADC sur la carte.

–Pour la partie actionneurs

•uniquement une consigne (autorisation ou basse

tension)

•Consigne + puissance sur les parties opératives.

–Refroidissement

–Motorisation

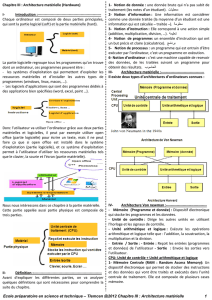

Plusieurs possibilités d’architecture

1 : Développement complet du système

(custom)

FPGA CPU

OS +

OPC UA

(serveur)

Alim

2 : Carte développée dans un châssis

Sans communication fond de panier.

–Choix châssis (Cpci, PCI, PXI etc…)

–Format 3U 6U ?

FPGA CPU

OS +

OPC UA

(serveur)

Alim

Avantage : modulaire

3 : Carte développée dans un châssis

avec un CPU central (comme HESS2)

(communication fond de panier)

FPGA PCI

Alim

CPU OS +

OPC UA

(serveur)

CPU

FPGA

4 : Système sur étagère (COTS)

ADC/DAC

CPU OS +

OPC UA

(serveur)

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

1

/

13

100%