Intermède mémoires

PERI Master ACSI cours 1 - 1

Gestion des Périphériques

Organisation

Enseignants

François PÊCHEUX (Cours, Groupe du vendredi

matin)

Mounir BENABDENBI (Groupe du lundi matin)

Déroulement

3 séances de TD

7 séances de TME

PERI Master ACSI cours 1 - 2

Gestion des Périphériques

Organisation

Modalités de Contrôle

Note de TP : /20

Note de contrôle écrit : /20

Note d’examen : /60

PERI Master ACSI cours 1 - 3

Gestion des Périphériques

Architecture du PC

Année 2006 - 2007

F. Pêcheux

PERI Master ACSI cours 1 - 4

Les cinq groupes principaux

Le processeur central

La mémoire de travail

La mémoire fixe

Les entrées

Les sorties contrôle

chemin de

données

Mémoire

Sorties

Entrées

Processeur

Ordinateur

PERI Master ACSI cours 1 - 5

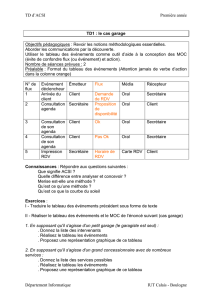

Modèle de système

Processeur

Mémoire

RAM

Carte graphique

Disque dur

Clavier

Imprimante

Carte réseau

Mémoire

fixe

Sortie

SortieEntrée Entrée/

Sortie

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%