Transparents

1

M. Taurigna, ,D. Charlet C. Paillé

Ethernet Interface

But de la R & D : Intégrer un interface Ethernet dans un FPGA avec le minimum de composant externes. Il

pourra être implanté sur les différentes cartes de tests du service ainsi que pour l'acquisition de données sur des cartes

front-end.

Support financier : LAL

Shedule du projet : Fin 2012

Moyen mis en œuvre : Carte évaluation ALTERA à base

1) de Cyclone III A3C25

2) SRATIX II EP2SGX90

3) STRATIX IV.

Objectif : Implémenter les fonctions Ethernet de base, nécessaire pour autoriser des transactions entre un ordinateur

et FPGA, sur un réseau local.

Architecture : Implémentation d'un processeur pour la gestion des différentes fonctions.

2

Ethernet : principes de base

Couche ISO

1) Physique : Transmission des donnés sous forme binaire (phy gestion hardware)

2) Liaison : Adresse physique MAC (Media Access control)

3) Réseau : Determine le parcours des données et l'adresse physique (protocole

IPV4,IPV6, ARP, ICMP....)

4) Transport Connexion bout a bout (UDP, TCP, …)

5) Session

6) Présentation

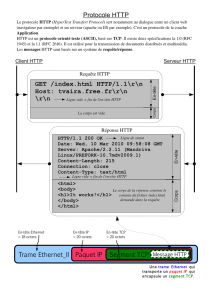

7) Application (FTP, HTTP, Telnet,....

Trame Ethernet

Longueur : 64 < nb octet < 1536 (taux de transfert maximum)

Max 64k => fragmentation.

Jumbo frame max 9k.

CRC non obligatoire (crc inclue dans le header en IPV4.

ETHERNET : Protocole de réseau local à commutation de paquets

3

Ethernet : Réseau fonction de base

Couche réseau

1) ARP : Address Resolution Protocol (traduction MAC adresse à l' adresse IPV4)

2) IPV4 (Internet Protocol IP)

3) ICMP : Internet controle message protocole (routage, relayage, controle de flux)

encapsuler dans un datagrame IP ex de cde Ping

IP datagramme

Encapsulation

4

Ethernet : Transport fonction de base

Couche transport

1) UDP :User Datagramme Protocol : Transmission simple entre 2 entités définis par

leur adresse IP (encapsuler dans un paquet IP,sans négociation => sans garantie de

livraison

2) TCP : Transmission Control Protocol : Inclus un certain nb de mécanismes qui vont

assurer l' intégrité du transfert des donnée. (ordonnancement des segments, contrôle

de flux, numéro de séquence et acquittement, gestion congestion,....)

Datagramme UDP Datagramme TCP

5

Ethernet : Réalisation Hardware 1

MAC

TSE PHY

Ethernet

Memory SGDMA

CPU

NIOS

Program

Memory

QDR/DDR

(Optionnelle)

SGMII

FPGA :

Stratix IV

Utilisateur

Marvell,NS,..

Internal transceiver

Resource : Alut s 9K

Register 9K

Memory : Ethernet 64kB

Program 226KB + xxxKB

(Interne ou externe )

Flash

6

6

7

7

8

8

9

9

10

10

1

/

10

100%