Mod`ele d`exécutif distribué temps réel pour SynDEx

ISSN 0249-6399

apport

de recherche

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

Mod`

ele d’ex´

ecutif distribu´

e temps r´

eel pour SynDEx

Thierry Grandpierre, Christophe Lavarenne, Yves Sorel

N ˚ 3476

Aoˆut 1998

TH`

EME 4

Mod`ele d’ex´ecutif distribu´e temps r´eel pour SynDEx

Thierry Grandpierre, Christophe Lavarenne, Yves Sorel

Th`eme 4 — Simulation et optimisation

de syst`emes complexes

Projet sosso

Rapport de recherche n˚ 3476 — Aoˆut 1998 — 70 pages

R´esum´e:

Ce document s’adresse aux concepteurs d’applications distribu´ees temps r´eel embarqu´ees, qui d´esirent op-

timiser l’implantation de leurs algorithmes de commande et de traitement du signal et des images sur des

architectures multiprocesseurs. Il s’adresse ensuite plus particuli`erement aux utilisateurs du logiciel SynDEx v4

de CAO niveau syst`eme, qui supporte la m´ethodologie “Ad´equation Algorithme Architecture”, d´evelopp´ee pour

am´eliorer la productivit´e de ces concepteurs.

Le but de ce document est d’abord de permettre au public vis´e de comprendre les tenants et aboutissants

de la m´ethodologie et de ses mod`eles, et plus particuli`erement les ex´ecutifs distribu´es g´en´er´es par le logiciel

SynDEx, optimis´es pour le temps r´eel et pour les architectures embarqu´ees multiprocesseur. Son but est ensuite

de permettre `a un public averti de porter le jeu de macros qui constituent le “noyau g´en´erique d’ex´ecutif SynDEx

v4”, pour obtenir un g´en´erateur d’ex´ecutif sp´ecifique `a un nouveau type de processeur.

Mots-cl´e: ex´ecutif, distribu´e, multiprocesseur, temps r´eel, embarqu´e, SynDEx, m´ethodologie Ad´equation

Algorithme Architecture

(Abstract: pto)

Unit´e de recherche INRIA Rocquencourt

Domaine de Voluceau, Rocquencourt,BP 105, 78153 LE CHESNAY Cedex (France)

T´el´ephone : 01 39 63 55 11 - International : +33 1 39 63 55 11

T´el´ecopie : (33) 01 39 63 53 30 - International : +33 1 39 63 53 30

Distributed Real Time Executive Model for SynDEx

Abstract:

This document is addressed to designers of distributed real time embedded applications in the domain of

signal and image processing, and control, who wish to optimize the implementation of their algorithms on

multiprocessor architectures. It is addressed more particularly to the users of the system-level CAD software

SynDEx v4, which supports the “Algorithm Architecture Adequation” methodology developed to improve the

designer’s productivity.

The purpose of this document is first to allow the targeted public to understand the issues and models of

the methodology, and more particularly the distributed executives generated by the SynDEx software, which

are optimized for real time and for embedded multiprocessor architectures. Its purpose is moreover to enable

experienced users to port the set of macros which constitute the “SynDEx v4 generic executive kernel”, in order

to obtain an executive generator specific to a new processor type.

Key-words: executive, distributed, multiprocessor, real time, embedded, SynDEx, Algorithm Architecture

Adequation methodology

Mod`ele d’ex´ecutif distribu´etempsr´eel pour SynDEx 3

Table des mati`eres

1 Introduction 4

1.1 Syst`emes r´eactifs temps r´eel embarqu´es ................................ 4

1.2 Architectures distribu´ees embarqu´ees.................................. 5

1.3 Implantation distribu´ee optimis´ee.................................... 6

1.3.1 Parall´elisation........................................... 6

1.3.2 Optimisation ........................................... 6

1.3.3 Minimisation de l’ex´ecutif.................................... 7

1.3.4 Choix de la granularit´e ..................................... 7

1.3.5 Caract´erisation et pr´edictiondeperformances......................... 8

1.3.6 G´en´eration d’ex´ecutifs...................................... 9

1.4 Synchronisation dans les architectures distribu´ees........................... 9

1.4.1 Synchronisation centralis´ee ................................... 9

1.4.2 Synchronisation distribu´ee.................................... 10

1.4.3 Synchronisation pour partage des s´equenceurs d’instructions . . . . . . . . . . . . . . . . . 10

2M´ethodologie Ad´equation Algorithme Architecture (AAA) 12

2.1 Mod`ele d’algorithme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.1.1 Mod`ele flot de contrˆole et flot de donn´ees ........................... 13

2.1.2 Prise en compte du temps, v´erifications,simulations ..................... 13

2.2 Mod`eled’architecture .......................................... 14

2.2.1 Mod`elemulticomposant ..................................... 14

2.2.2 Caract´erisationd’architecture.................................. 15

2.3 Mod`ele d’implantation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.1 Distribution et ordonnancement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.2 Contraintesetoptimisation ................................... 16

2.4 Heuristique d’ad´equation ........................................ 16

2.4.1 Principes ............................................. 16

2.4.2 Pr´evision de comportement temps r´eel............................. 17

2.5 G´en´eration d’ex´ecutifs distribu´es temps r´eel.............................. 17

2.6 LogicielSynDEx ............................................. 18

3Mod`ele d’ex´ecutif 19

3.1 Introduction................................................ 19

3.2 Structure du macrocode interm´ediaire ................................. 20

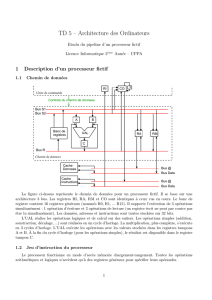

3.3 Structuredumacrocodepourchaqueprocesseur ........................... 21

3.4 Chargement arborescent des programmes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.5 Allocation m´emoire............................................ 22

3.6 S´equences de calcul et de communications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.7 Implantation des d´ependances de donn´ees ............................... 22

3.7.1 Communication et synchronisation par m´ediaRAM ..................... 23

3.7.2 Communication et synchronisation par m´ediaSAM...................... 24

RR n˚ 3476

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

1

/

74

100%