Etude et mise en oeuvre d`un Imageur CMOS APS avec

Conception d’un convertisseur

analogique/numérique pour des imageurs

CMOS embarqués

Doctorant : Pierre BISIAUX

Directeur de these : Philippe BENABES

11/06/2015

1

Journée des doctorants du Geeps

Plan

2

I. Introduction aux imageurs

1. Principe général

2. Technologie d’imageurs

II. Conversion analogique/numérique

III. Architecture

IV. Travaux futurs

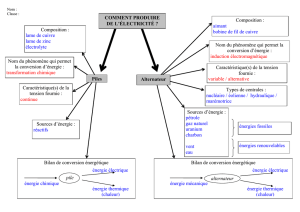

Principe général des imageurs

3

Système composé :

D’une matrice de pixels

Conversion lumière grandeur électrique analogique

De convertisseurs analogiques numériques (CAN)

Conversion grandeur électrique analogique mot numérique

D’un système d’adressage

Pixel CAN

Lumière

Grandeur électrique

analogique Mot numérique sur

N bits

Technologie d’imageurs

4

CCD : charge-coupled device

Imageurs de grande qualité

Facile à réaliser

Long temps d’intégration

Lecture sérialisée

CMOS

Résolution élevée (pixels)

Intégration monolithique

Technologie grand public

Lecture parallèle

Plan

5

I. Introduction aux imageurs

II. Conversion analogique/numérique

1. architecture des CAN

2. Système complet

3. Spécifications

III. Architecture

IV. Travaux futurs

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

1

/

20

100%