CAO de SYSTEMES SUR PUCE: composants virtuels

M. Robert: CAO de systèmes sur puce

GDR Nanoélectronique : les composants ultimes et leurs alternatives

CAO de SYSTEMES SUR PUCE:

composants virtuels, réutilisation et reconfiguration

Michel ROBERT, Membre de L'Institut Universitaire de France

LIRMM, UMR CNRS /Université Montpellier 2, 161, rue Ada, 34392 Montpellier Cedex 5

Mél:

L'évolution très rapide des technologies de

fabrication de circuits intégrés sur silicium (CMOS)

permet déjà de réaliser des systèmes numériques

complets intégrés sur une même puce: les SOC (pour

System On Chip). Les prévisions d'évolution faites par

la SIA (Semiconductor Industry Association) montrent

que le nombre de transistors par circuit va être multiplié

par un facteur 50 dans les 10 prochaines années. En

1998, un microprocesseur était composé d'environ 10

millions de transistors. En 2008, un circuit de référence

équivalent dont la surface ne sera que le double par

rapport à 98 (600 mm2) pourra être composé de près de

500 millions de transistors.: on prévoit ainsi d’atteindre

1 milliard de transistor sur une puce autour de 2010. Il

sera alors aisé (si les outils de CAO ont suivi

l'augmentation de la complexité) de concevoir des

systèmes parallèles, intégrer des contrôleurs de

périphériques ou des fonctions élaborées de manipulation

3D d'images tout en disposant d'une mémoire intégrée

donc à accès très rapide.

Ces systèmes hautement complexes doivent être

conçus de manière efficace car le temps d’arrivée du

produit sur le marché est un facteur crucial de réussite.

Ils doivent également être conçus et vérifiés de manière

sure car les coûts de fabrication sont tels qu’ils ne

tolèrent pas des tentatives multiples. Supposant une

conception efficace et une vérification/validation sure,

ces systèmes sur puce doivent tout de même être vérifiés

après fabrication car les technologies sous-microniques

actuelles ne peuvent toujours pas garantir un rendement

de 100%.

Qu’il s’agisse de conception ou de vérification

l’approche méthodologique fondamentale pour ces

systèmes est toujours la même du fait de la complexité

inhérente à ces systèmes. Dans une première phase, un

concept, sensé apporter une solution à un problème

posé, est mis en place. Dans une deuxième phase cette

solution est appliquée au niveau du système complexe à

travers un outil logiciel. A noter que le terme concept

peut désigner ici n’importe quel aspect de la conception

ou de la vérification: modèle de retard, modèle de

puissance, modèle de sensibilité aux radiations, modèle

de défaillances...

1-Outils de conception et de vérification

Devant les possibilités offertes par les technologies

de fabrication, les techniques de conception des systèmes

électroniques vont évoluer vers l'intégration de systèmes

de plus en plus complexes avec des durées d'obsolescence

de plus en plus courtes. Des blocs fonctionnels déjà

validés (y compris sur Silicium) appelés généralement

IP (pour Intellectual Property) devront être de plus en

plus utilisés. De ce fait, les outils classiques de

Conception Assistée par Ordinateur (CAO) dans les

domaines de la Microélectronique devront évoluer en

prenant de plus en plus en compte l'aspect système et le

recours au prototypage à des fins de validation. Les

classiques bibliothèques utilisées pour la conception des

Circuits Intégrés pour Applications Spécifiques (ASICs)

seront complétées, voire remplacées, par des bases de

données de composants virtuels dont la fonctionnalité

pourra correspondre à un coeur de processeur ou même à

un ordinateur complet avec sa mémoire et ses

entrées/sorties. Le concepteur d'ASICs a "manipulé" des

transistors pendant les années 80, des blocs fonctionnels

pendant les années 90; il assemble déjà, et il assemblera

de plus en plus des composants virtuels complexes ou

IPs pendant la prochaine décennie.

La conception réutilise; elle devient incrémentale et

flexible. A partir de blocs IPs, les concepteurs adapteront

rapidement le système à l'application visée. Dans les

années 80, à coté des outils graphiques (schématique,

dessin de masques, placement/routage), les concepteurs

de circuits intégrés disposaient de simulateurs électriques

au niveau transistor pour les fonctions analogiques et de

simulateurs au niveau porte pour les fonctions logiques.

A la fin des années 80, l'utilisation du langage VHDL

(comportemental et structurel) s'est généralisée. Ce

langage, initialement développé pour la modélisation et

la simulation, est également utilisé pour la description

comportementale ou RTL (transfert de registres) d'une

architecture logique pour la synthèse automatique Des

environnements de CAO permettent de vérifier la

M. Robert: CAO de systèmes sur puce

GDR Nanoélectronique : les composants ultimes et leurs alternatives

fonctionnalité du système à ce niveau d'abstraction par

des simulations de type flot de données. Ces outils sont

basés sur des modèles virtuels (codés en C). Ils

permettent également d'assembler et de co-simuler des

modèles virtuels décrits dans différents langages à des

niveaux d'abstraction différents.

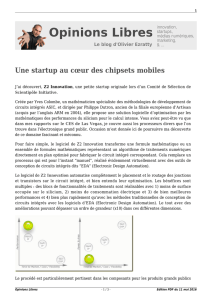

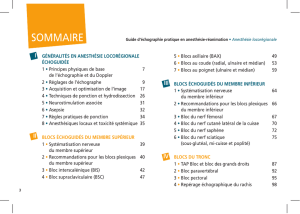

La figure représente le flot de conception d'un

système sur silicium. La réutilisation de blocs affecte le

flot de conception sous plusieurs aspects. Il convient de

distinguer plusieurs niveaux de blocs réutilisables ou IP:

les “ hard-cores ” sont des blocs entièrement conçus et

optimisés pour une technologie donnée, les “ soft-

cores ” sont des blocs définissant une architecture au

niveau RTL. Du point de vue de l'utilisateur de blocs

réutilisables, il est nécessaire de faire le choix des blocs

qui permettront d'implanter efficacement le plus grand

nombre de fonctionnalités du système à un coût

acceptable. Le flot n'est alors pas complètement

descendant puisqu'il sera nécessaire de capturer pour les

blocs choisis leur comportement, d'obtenir des modèles

de simulation, pour finalement intégrer ces blocs dans le

système. En revanche, du point de vue du fournisseur de

blocs réutilisables, la notion primordiale est celle de la

conception en vue de la réutilisation (“ Design For

Reuse ”). Ainsi, un bloc IP pourra être défini pour une

application donnée, puis optimisé pour une technologie

cible. Le flot est alors vraiment descendant: le

comportement du bloc est d'abord décrit, puis son

implantation est progressivement raffinée.

Les recherches actuelles en CAO de SOCs se situent

à différents niveaux: spécification, modélisation,

synthèse, vérification, test. On parle de technologie de la

conception (“ Design Technology ”), notion qui

recouvre les algorithmes, les outils logiciels et

matériels, ainsi que les méthodes de conception des

systèmes.

2-Circuits et systèmes

Deux techniques de réalisation des systèmes

électroniques se dégagent:

• matériel standard: réalisations basées sur des

composants programmables au niveau matériel

(FPGA) ou logiciel (processeurs). Cette technique

souple est adaptée à la fabrication de prototypes ou

de petites/moyennes séries, et est accessible à un

grand nombre d’utilisateurs. Les solutions

technologiques apportées par les circuits

programmables de type FPGA (Field Programmable

Gate Array) permettent actuellement l'intégration de

1 million de portes logiques équivalentes sur le

même circuit. Ces circuits suivront l'évolution

technologique décrite plus haut, et contribueront à

une standardisation du matériel: la personnalisation

des systèmes se fera ainsi de manière croissante au

niveau logiciel. La reconfiguration de système

permettra une redéfinition du circuit à tout moment.

Des processeurs reconfigurables autoriseront

l’adaptation des opérateurs matériels en temps réel

avec les besoins de l’algorithme en cours

d’exécution.

• matériel spécifique: réalisations basées sur la

conception de systèmes sur puce (SOC) spécifiques,

en utilisant des composants virtuels (IP). Cette

technique permet d’obtenir les meilleures

performances techniques (vitesse, puissance, surface),

mais compte tenu des coûts (moyens humains,

logiciels, coûts des prototypes,..etc) elle est réservée

à des fabrications en grandes séries (téléphones

portables par exemple).

L’architecture d’un système sur puce sera composée

autour des éléments suivants:

• matériel partiellement reconfigurable, avec des blocs

FPGA, et des interconnexions reconfigurables,

• architectures composées de multiprocesseurs

hétérogènes (micro-controleurs, processeurs de

traitement numérique du signal,...etc.) et de blocs

IPs divers,

• - mémoires,

• - logiciel embarqué (ou enfoui).

Ces circuits devront fonctionner dans des

environnements de communications complexes en

s’adaptant rapidement à tout type de standard.

La course à la miniaturisation est une caractéristique

essentielle des technologies CMOS. Dans ce domaine,

miniaturisation et donc intégration sont synonymes de

performances. On intègre toujours plus de composants

sur un même substrat de silicium pour obtenir des

systèmes qui fonctionnent à des fréquences plus élevées,

qui consomment moins, qui ont plus de capacité

mémoire ou de ressources de calcul, qui présentent un

coût ou un encombrement moindre… L’art du

concepteur consiste à gérer un compromis entre tous ces

paramètres.

Les technologies de fabrication sont limitées par les

propriétés des matériaux et les lois physiques. Les outils

et méthodes de CAO de circuits sont limitées par la prise

en compte de l’ensemble de ces paramètres dans des

domaines d’applications divers:

• gestion de la complexité, optimisation et vérification

des systèmes,

• modélisation des niveaux électriques et topologiques

(“layout”: dessin des masques technologiques,

interconnexions de cellules,…), où les modèles

M. Robert: CAO de systèmes sur puce

GDR Nanoélectronique : les composants ultimes et leurs alternatives

doivent être suffisamment précis et simple pour

permettre des simulations dans des temps

raisonnables.

Math./info….

…. Techno./Phys.

Figure 1

Spécifications :

- Algorithme

- Performances

Système

Flot de données

Architecture Système :

- Optimisation des mémoires

- Partition Matériel/Logiciel

Librairies

de blocs

matériels

réutilisables

Librairies

d'objets

logiciels

réutilisables

Conception pour

la réutilisation

Conception pour

la réutilisation

Architecture

Matérielle

Architecture

logicielle

Choix de blocs

Choix d'objets

Modèles

De simulation

Synthèse

Matérielle

Compilation

Logicielle

Prototype

Système sur

Silicium

1

/

3

100%