Système sur puce autour d`un processeur Plasma

Système sur puce autour d’un processeur Plasma

Camille Leroux

1 Objectif du TP

L’objectif de ce TP est de vous familiariser avec l’utilisation d’un système sur

puce. Nous nous focalisons sur le processeur Plasma qui est un processeur RISC

32-bit softcore (http://opencores.org/project,plasma). Une première partie

guidée permet de bien comprendre le flot de conception conjoint associé au proces-

seur plasma. A partir d’une application simple nous allons voir comment simuler

le système et comment faire interagir les parties logicielles et matérielles. Une fois

la plateforme prise en main, vous implémenterez une autre application sur la pla-

teforme puis vous devrez accélérer son exécution à l’aide des différentes techniques

d’optimisations (extension du jeu d’instruction, utilisation de coprocesseur, gestion

intelligente de la mémoire,...)

Figure 1 – Processeur Plasma.

1

2 Description du système

Local memory

64K Plasma CPU Cache

Controler uboot RAM UART

DMA

Engine

Coprocessor 1 Coprocessor 2 Coprocessor 3 Coprocessor 4PCIe_in PCIe_out

System Bus

code_bin.txt

pcie_in.txt pcie_out.txt

TESTBENCH

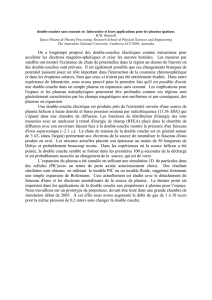

Figure 2 – Le SoC Plasma dans son environnement de simulation.

Dans la suite, nous distinguerons le processeur Plasma (Figure 1) et le SoC

Plasma (Figure 2) qui est le système incluant le processeur lui-même et les autres

composants (Mémoire, CoProcesseurs, PCI express, UART, etc).

2.1 Le SoC plasma dans son environnement de simulation

La Figure 2 (Plasma CPU + mémoire + ... + fichier binaire + test bench

vhdl) montre le SoC Plasma dans un environnement de simulation simple. Tout

le SoC est décrit en VHDL, un testbench permet de simuler le comportement du

système et de vérifier son fonctionnement sans avoir à l’implanter sur un FPGA.

Cet environnement de simulation permet de gagner beaucoup de temps lors de la

phase de conception.

En plus de la description matérielle du système, il est nécessaire de disposer du

programme à exécuter sur le processeur. Pour cela, nous allons utiliser un flot

de compilation MIPS qui permet de générer un fichier binaire code_bin.txt à

partir d’un programme C (Cf Figure 3). Ce fichier binaire est ensuite utilisé pour

initialiser le contenu de la mémoire de programme du Plasma. Cette initialisation

se fait de manière statique lors de l’analyse du fichier VHDL de la mémoire

programme.

2

2.2 Structure du répertoire de travail

Voici la structure de votre répertoire de travail. Vous devez vous familiariser

avec celui-ci afin de bien comprendre ce que vous faites.

soc_plasma/

SOFTWARE (fichiers source C)

mon_projet

Includes

mes_fonctions.h

Sources

main.c

shared/

boot.asm

no_os.c

plasma.h

plasmaCoprocessors.h

...

HARDWARE/ (description VHDL du SoC Plasma)

plasma_core/ (contient la description du Plasma)

vhdl/

...

custom/

SIMU/ (simulation du Soc Plasma)

bmp2txt.py

txt2bmp.py

code_bin.txt

code.txt

makefile

output.txt

pcie_in.txt

pcie_out.txt

tbench.vhd

test.axf

test.bin

SYNTHESIS (synthèse du SoC Plasma sur FPGA)

Description de quelques fichiers et repertoires importants :

—soc_plasma/ : Repertoire racine : contient tous les fichiers de description

(SW et HW) et de simulation

—C: contient les fichiers source C à exécuter sur le processeur Plasma

—plasmaCoprocessors.h fonction d’accès aux coproc

—main.c : fichier principal devant être compilé puis exécuté sur le Plasma

—SoPC_Design.h : définition du plan mémoire permettant l’acces aux FIFO

branchées sur le bus système

—boot.asm : code d’init du processeur exécuté avant le main (initialisation de

la pile)

3

—no_os.c : fonctions utiles d’affichage pour le debug

—plasma.h : plan mémoire du système

3 Tutorial

L’objectif de ce tutorial est de vous familiariser avec l’environnement de

développement et de simulation de la plateforme Plasma. Pour cela, nous allons

simuler l’exécution d’un traitement simple sur le processeur Plasma. Puis, nous

utiliserons différentes méthodes d’optimisations pour accélérer le traitement

effectué.

3.1 L’application à simuler/intégrer : Mise à la pleine échelle

Le but du traitement est de mettre une série d’échantillons à la pleine échelle.

Considérons une suite de 16 échantillons codés sur 8 bits (entiers non-signés) :

x[i]. Dans un premier temps, on calcule les valeurs minimum et maximum de la

séquence d’échantillons :

m=

15

min

i=0 (xi)

M=15

max

i=0 (xi)

Puis on met chaque échantillon à l’échelle en normalisant par le facteur β:

β=255

M−m

yi=β×(xi−m)

3.2 Co-Simulation de la mise à l’échelle

3.2.1 Compilation du fichier C pour le processeur Plasma (Software)

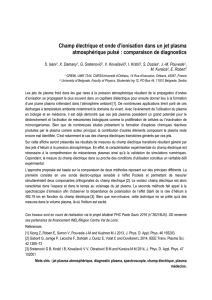

Le flot de compilation software est représenté sur la Figure 3. Le but est

d’obtenir un fichier texte (code_bin.txt) qui contient le code binaire prêt à

être exécuté par le processeur. Comme nous le verrons dans la suite, celui-ci sera

chargé dans la mémoire du processeur Plasma pour être exécuté.

Comme indiqué sur la Figure 3, nous allons utiliser le compilateur gcc-mips pour

générer le fichier binaire (test.axf), puis nous le convertirons en fichier texte à

l’aide d’un script fourni (convert_bin.exe).

La description en virgule fixe de l’algorithme de mise à l’échelle vous est fournie

dans le fichier main.c. Ouvrez ce fichier et décommentez la ligne :

scale_no_opt(data, pixel_nb);. Cette fonction est décrite dans le fichier

4

uboot.asm

GCC-ASM

uboot.o

no_os.c

GCC-MIPS

no_os.o

main.c

GCC-MIPS

main.o

GCC-LINKER

test.axf

convert_bin.exe

code_bin.txt

Figure 3 – Flot de compilation du SoC plasma.

soc_plasma/SOFTWARE/tuto_plasma/Includes/scale.h

Notez que des fonctions d’affichages sont utilisées pour afficher les résultats du

calcul.

Question : Nous allons exécuter un programme sur un processeur décrit en VHDL.

Comment est-il possible d’utiliser des fonctions d’affichages dans ces conditions ?

D’autre part, un accès au timer du SoC permet d’afficher une indication du nombre

de cycles d’horloges écoulés. Cela permet de profiler l’application en identifiant les

traitements qui prennent le plus de temps.

L’objectif du tutorial est de simuler l’exécution de ce programme sur le pro-

cesseur Plasma. Nous allons suivre le flot de simulation décrit sur la Figure 4.

Placez-vous dans le répertoire de simulation SIMU.

— Compilation du fichier boot.asm :

$ mips-elf-as -o boot.o ../SOFTWARE/shared/boot.asm

— Compilation du fichier uboot.asm :

$ mips-elf-as -o uboot.o ../SOFTWARE/shared/uboot.asm

— Compilation du fichier no_os.c :

$ mips-elf-gcc -O3 -Wall -c -s -funroll-loops -mips1 -

mtune=mips1 -msoft-float ../SOFTWARE/shared/no_os.c -o no_os.o

— Compilation des headers :

$ mips-elf-gcc -O3 -Wall -c -s -funroll-loops -mips1

-mtune=mips1 -msoft-float -DVHDL_SIMULATION ../SOFT

WARE/tuto_plasma/Includes/*.h

— Compilation du fichier main.c :

5

6

6

7

7

8

8

9

9

10

10

1

/

10

100%