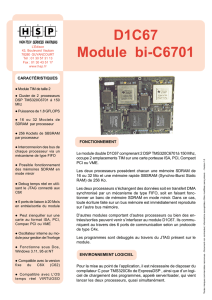

D1C44 Module bi-C44

D1C44

Module bi-C44

CARACTÉRISTIQUES

! Module TIM-40 de taille 1

! 2 processeurs DSP

TMS320C44 à 60 Mhz

! Puissance de 120 MFLOPS

! 0,5 à 2 Moctets de SRAM

0 WS sur les bus locaux et

globaux des processeurs

! Mémoire ROM contenant

les informations de configu-

ration des processeurs

! Debug temps réel en utili-

sant le JTAG connecté aux

C44

! 4 ports de liaison à 20

Mo/s par processeur

! Peut s’enquiller sur une

carte au format ISA, PCI,

compact PCI ou VME

! Oscillateur interne au mo-

dule pour gestion de l’horloge

! Fonctionne sous Dos,

Windows 3.11, 95 et NT

! Compatible avec L’OS

temps réel VIRTUOSO

JTAG

C44

n°1

1

2

4

5

C44

n°2

41

2

5

2

3

4

0

1

5

Oscillateur

bus local

SRAM

SRAM

bus

global

EPROM

Vers la carte porteuse

Vers la carte porteuse

SRAM

bus

global

bus local

SRAM

EPROM

L’Edison

43, Boulevard Vauban

78280 GUYANCOURT

Tél : 01 30 57 31 13

Fax : 01 30 43 51 17

www.hsp.fr

FONCTIONNEMENT

Le module double D1C44 comprenant 2 TMS320C44 à 60 Mhz occupe

un emplacement TIM-40 sur une carte porteuse ISA, PCI, compact PCI

ou VME.

Les deux processeurs possèdent chacun deux mémoires SRAM 0

WS allant jusqu’à 2 Mo : une sur leur bus local et une autre sur leur

bus global. Elles communiquent avec le processeur en mots de 32

bits.

Grâce aux informations contenues dans une mémoire ROM implan-

tée sur le module, les processeurs peuvent être initialisés sans avoir

besoin d’être reconfigurés par le programme utilisateur, à chaque re-

mise en route.

D’autres modules comportant d’autres processeurs ou bien des en-

trées/sorties peuvent venir s’interfacer au module D1C44. Ils commu-

niquent au travers des 4 ports de communication disponibles sur cha-

que TMS320C44.

Les programmes sont debuggés au travers du JTAG présent sur le

module.

ENVIRONNEMENT LOGICIEL

Pour la mise au point de l’application, il est nécessaire de disposer

d’un compilateur C pour TMS320C4x, ainsi qu’un logiciel de charge-

ment des programmes, appelé server/loader, qui vient lancer le 1er

processeur qui va à son tour lancer celui qui le suit, et ainsi de suite...

Toutes marques commerciales reconnues - Document non contractuel, informations succeptibles d'être modifiées sans préavis - Version 1.0

MODULES DISPONIBLES, EN FONCTION DES CONFIGURATIONS MÉMOIRES

! D1C44-0500 2 processeurs C44 avec 0,5 Mo de SRAM 0 WS sur le bus local et 0 Mo sur le bus global (pour chaque C44)

! D1C44-0505 2 processeurs C44 avec 0,5 Mo de SRAM 0 WS sur le bus local et 0,5 Mo sur le bus global (pour chaque C44)

! D1C44-0520 2 processeurs C44 avec 0,5 Mo de SRAM 0 WS sur le bus local et 2 Mo sur le bus global (pour chaque C44)

! D1C44-2020 2 processeurs C44 avec 2 Mo de SRAM 0 WS sur le bus local et 2 Mo sur le bus global (pour chaque C44)

Architecture interne d’un C4X

Port de comm. 0 *

Port de comm. 1

Port de comm. 2

Port de comm. 3 *

Port de comm.4

Port de comm. 5

"

"

"

"

"

"

"

"

"

"

"

"

"

"

"

"

"

"

Timer 1

Timer 0

Module JTAG

#### ####

Cache

Programme

Bloc 0

RAM

(4Ko)

ROM

(16Ko)

Bloc 1

RAM

(4Ko)

#

CPU

Virgule flottante et entier

ALU Multiplicateur

virgule flottante et entier

12 Registres

de précision étendus

Adresse Adresse

Gen.0 Gen.1

8 Registres auxiliaires

14 Registres de contrôle

#

Co-processeur

DMA

Voie 0

Voie1

Voie 2

Voie 3

Voie 4

Voie 5

$

"

$

"

%

%

Slot 4 Slot 3 Slot 2 Slot 1

Interface

PC

JTAG

ISA / PCI VME / COMPACT PCI

Slot 4

Slot 3 Slot 2

Slot 1

TMS320C40

10,7 cm

6,35 cm

CARTES PORTEUSES

Ports de

Communication

Adressage des

bus mémoires

Boîtier

C44 *

4

(1, 2, 4, 5)

24 bits

Plastique

TMS320C4X

Ports de Communication

Horloge et reset

Bus

global

JTAG

Bus local

Interruptions

et contrôle

1 2 4 5

1

/

2

100%