Electronique numeriq..

ANNEXE

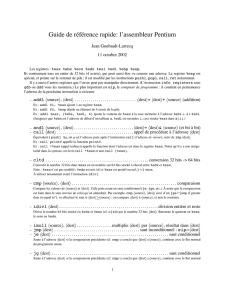

MODE D'ADRESSAGE / JEU D'INSTRUCTIONS du 80C196KC

TABLE DES MATIERES

1. INTRODUCTION ....................................................................................................................................................1

2. MODES D'ADRESSAGE.........................................................................................................................................2

2.1. mode d'adressage direct.........................................................................................................................2

2.2. mode d'adressage immédiat ...................................................................................................................3

2.3. mode d'adressage indexé .......................................................................................................................4

2.4. mode d'adressage étendu .......................................................................................................................6

2.5. mode d'adressage indirect......................................................................................................................7

2.6. mode d'adressage relatif.........................................................................................................................8

3. JEU D'INSTRUCTIONS ..........................................................................................................................................9

3.1. famille des instructions arithmétiques ...................................................................................................9

ADDITION........................................................................................................................................9

SOUSTRACTION .............................................................................................................................9

MULTIPLICATION..........................................................................................................................10

DIVISION .........................................................................................................................................11

CHANGEMENT DE SIGNE.............................................................................................................11

EXTENSION DE SIGNE..................................................................................................................11

COMPARAISON ..............................................................................................................................12

3.2. famille des instructions logiques ...........................................................................................................12

ET ......................................................................................................................................................12

OU .....................................................................................................................................................12

OU EXCLUSIF .................................................................................................................................12

PAS....................................................................................................................................................12

INCREMENTATION........................................................................................................................12

DECREMENTATION.......................................................................................................................13

MISE A ZERO ..................................................................................................................................13

MISE A ZERO OU UN DU BIT CARRY ........................................................................................13

MISE A ZERO DU BIT VT ..............................................................................................................13

DECREMENTATION ET BRANCHEMENT SI RESULTAT NON NUL......................................13

DECALAGE LOGIQUE ...................................................................................................................14

DECALAGE ARITHMETIQUE A DROITE ....................................................................................14

ECHANGE ........................................................................................................................................14

3.3. famille des instructions de branchement................................................................................................15

BRANCHEMENTS CONDITIONNELS ..........................................................................................15

BRANCHEMENTS INCONDITIONNELS......................................................................................15

3.4. famille des instructions de mouvement..................................................................................................16

CHARGEMENT................................................................................................................................16

RANGEMENT ..................................................................................................................................16

3.5. famille des instructions pour interruptions ............................................................................................16

VALIDATION DES INTERRUPTIONS ..........................................................................................16

INTERDICTION DES INTERRUPTIONS.......................................................................................16

RESET SOFT ....................................................................................................................................16

3.6. famille des instructions qui utilisent la pile ...........................................................................................17

APPELS/RETOUR SOUS PROGRAMME ......................................................................................17

EMPILAGE/DEPILAGE D'INFORMATIONS ................................................................................17

3.7. famille des instructions diverses............................................................................................................17

OPERATION NULLE.......................................................................................................................17

DEPLACEMENT DE BLOQUE DE DONNEES .............................................................................18

MODE FAIBLE CONSOMMATION...............................................................................................18

TEST MSB REEL .............................................................................................................................18

SAUT COMPLEXE ..........................................................................................................................18

Annexe page n° 1

1. INTRODUCTION

Les microcontrôleurs 16 bits d'INTEL de la famille MC96 ont une architecture registre à registre, c'est à dire,

qu'ils intègrent sur la même puce ( chip ), une zone de mémoire vive partagée comme suit :

♦De l'adresse 00H à 19H : se trouvent des fichiers à fonctions spéciales SFRs. Ils sont 26.

♦De l'adresse 1AH à 0FFH : se trouvent 230 registres libres.

Le 80C196KC possède, en plus des registres cités ci-dessus, une mémoire RAM de 256 octets

supplémentaires de l'adresse 100H à 1FFH. Ces mémoires peuvent être utilisées comme mémoire

temporaire.

Par suite, lorsque nous utilisons l'appellation registre, elle concernera une mémoire interne de l'adresse

comprise entre 00H et 0FFH.

Le micro-contrôleur étant capable d'exécuter des instructions, sur des opérandes 8 bits, sur des opérandes

16 bits ou sur des opérandes 32 bits, nous utiliserons les appellations suivantes:

♦breg: byte-register ( pour désigner un registre octet 8 bits lequel prend une adresse ).

♦wreg: word-register ( pour désigner un registre mot 16 bits lequel prend deux adresses ).

♦lreg: long-register ( pour désigner un registre long 32 bits lequel prend quatre adresses ).

Remarque 1: La zone registre peut donc être vue comme 256 byte-registers OU 128 word-registers OU 64

long-registers.

Remarque 2: Un wreg d'adresse 20H occupe la même place que les 2 breg d'adresse 20H et 21H, un lreg

d'adresse 20H occupe la même place que les 2 wreg d'adresse 20H et 22H ou encore que les 4 breg

d'adresse 20H, 21H, 22H, 23H.

Quelques abréviations utilisées

Base Définit un registre word ( Wreg ) dans lequel se trouve l'adresse de base.

bit_n° bit number Numéro de bit.

breg byte_register Désigne des registres à 8 bits ( byte ).

Dest destination Etiquette ou adresse du registre destination

lreg long_register Désigne des registres à 32 bits ( double word ).

Mnem mnémonique Mnémonique de l'instruction ( code opératoire )

PC program counter Compteur de programme

Src source Etiquette ou adresse mémoire source ( code opérande ).

Src1 source registre Etiquette ou adresse du registre source 1 ( 00H à 0FFH ).

wreg word_register Désigne des registres à 16 bits ( word ).

Valeur valeur immédiate Définit le mode d'adressage immédiat

Saut adresse de branchement Définit l'adresse ou l'étiquette de branchement en cas de saut

Annexe page n° 2

2. MODES D'ADRESSAGE

Le jeu d'instruction du 80C196KC peut être exprimé par 6 modes d'adressage différents.

2.1. mode d'adressage direct

Ce mode permet le traitement d'une donnée située à l'intérieur de la zone registre ( de 00H à 0FFH ).

♦Une adresse est définie sur 8 bits ( partie haute implicitement à 00H ), il est donc économique en

nombre d'octets de programme.

♦Il traite des données en mémoire interne, le temps d'exécution d'une instruction donnée est donc

plus court qu'avec un autre mode.

♦Les références mémoires sont limitées à 256 octets.

Les trois formes rencontrées avec ce mode sont:

♦Mnem Dest ou Src1 ( un opérande, direct ).

♦Mnem Dest,Src 1 ( deux opérandes, direct ).

♦Mnem Dest,Src1,Src ( trois opérandes, direct ).

ou:

♦Mnem est le mnémonique de l'instruction ( code opératoire ).

♦Dest est l'adresse registre destination ( 00H à FFH ) ( code opérande ).

♦Src1 est l'adresse registre source 1 ( 00H à FFH ) ( code opérande ).

♦Src est l'adresse mémoire source ( 00H à FFH ou externe ) ( code opérande ).

Remarque:

Certaines instructions peuvent aussi bien travailler sur des octets ( bytes 8) que sur des mots ( words 16 ) ou

sur des longs mots ( long words 32 ). Pour la distinction, un mnémonique se terminant par la lettre B précise

que les registres opérandes concernés par l'instruction sont des octets ( Bytes ). Un mnémonique se

terminant sans lettre indique que les registres opérandes concernés par l'instruction sont des mots ( words ).

Un mnémonique se terminant par la lettre L indique que les registres opérandes concernés par l'instruction

sont des mots longs ( Long words ).

Exemples:

INCB 20H ; incrémente le registre octet d'adresse 20H

20H

+ 00000001 =

20H

INC 20H ; incrémente le registre mot d'adresse 21H ( partie haute )/20H ( partie basse )

20H

+ 00000000 00000001 =

21H 20H21H

INCL 20H ; incrémente le registre long mot d'adresse 23H/22H/21H/20H

22H

+ 00000000 00000000 00000000 00000001 =

23H 20H21H

22H23H 20H21H

LDB 40H,20H ; charge le registre octet d'adresse 20H dans le registre octet d'adresse 40H

40H 20H

Annexe page n° 3

ADD 40H,20H,08H ; ajoute le registre mot d'adresse 21H/20H au registre mot d'adresse

; 09H/08H et range le résultat aux adresses 41H/40H

20H21H

08H09H

40H41H

+

=

Attention:

Lorsque vous travaillez sur des registres mots ( 16 bits ), vous devez spécifier une adresse paire.

Lorsque vous travaillez sur des registres longs ( 32 bits ), vous devez spécifier une adresse divisible par 4.

2.2. mode d'adressage immédiat

Ce mode permet d'affecter une valeur fixée dans le programme à une mémoire destinataire qui est

nécessairement un registre ( RAM interne de 00H à 0FFH ).

Les deux formes d'instruction rencontrées avec ce mode sont:

♦Mnem Dest,#valeur

♦Mnem Dest,Src1,#valeur

où:

valeur représente un nombre et non une adresse.

Remarque:

Le symbole # signifie à l'assembleur ASM96 ( programme qui traduit votre code source, écriture

mnémonique non exécutable par le micro-contrôleur, en code objet, écriture hexadécimale exécutable par le

micro-contrôleur ) que l'expression qui suit n'indique pas une adresse mais une donnée utilisée par

l'instruction.

Il ne peut y avoir qu'un seul opérande immédiat par instruction. Il est spécifié complètement à droite de

l'instruction; Dest et Src1 étant des registres ( RAM interne de 00H à 0FFH ).

Exemples:

LDB 31H,#0FAH ; charge le breg d'adresse 31H avec la valeur immédiate FAH

31H

11111010 ( FAH )

ADD 30H,20H,#1F5AH ; ajoute au wreg d'adresse 21H/20H la valeur 1F5AH et range le

; résultat dans le wreg d'adresse 31H/30H

20H21H

30H31H

+

=

00011111 01011010 ( 1F5AH)

MULU 40H,#8000H ; multiplie en non signé une valeur immédiate sur 16 bits ( pour l'exemple

; 32768 en décimal ) par le wreg d'adresse 41H, 40H et range le résultat

; dans le lreg d'adresse 43H, 42H, 41H, 40H

40H41H

42H43H

x

=

8000H

40H41H

CONSTANTE EQU 3AH ; l'instruction charge la valeur 3AH dans le breg

Annexe page n° 4

LDB 3AH,#CONSTANTE ; d'adresse 3AH

3AH

00111010 ( 3AH )

Remarque:

La directive EQU est interprétée par l'assembleur ASM96 comme suit:

Lorsqu'il assemble votre code source à chaque fois qu'il rencontrera dans le programme l'étiquette

CONSTANTE, il la remplacera par la valeur 3AH.

Nous aurions également pu écrire :

REGISTRE EQU 3AH

CONSTANTE EQU 3AH

LDB REGISTRE,#CONSTANTE

ou encore:

LDB 3AH,#3AH.

L'intérêt de la directive EQU est grand. Elle autorise dans votre code source, l'écriture d'instructions faisant

référence à des étiquettes, plutôt qu'à une suite de symboles hexadécimaux. Si ces étiquettes sont

judicieusement choisies par le programmeur, l'effet mnémotechnique est certain.

2.3. mode d'adressage indexé

L'adressage immédiat impose une valeur fixe à un registre. Il est des applications où le même registre doit

pouvoir être chargé par une valeur inconnue au moment de l'assemblage. Cela signifie que c'est le

programme lui-même qui, en cours d'exécution définira finalement la valeur à charger dans un registre. Ce

mode d'adressage ne définit pas une valeur à charger dans un registre par le micro-contrôleur, mais plutôt

une adresse mémoire où le micro-contrôleur ira chercher la valeur à charger.

Le mode indexé pour lequel on ne spécifie plus un opérande mais l'adresse d'un opérande, répond à ce

besoin. Deux autres modes qui sont l'étendu et l'indirect assurent également cette fonction. Mais le mode

indexé se distingue par le fait qu'il est bien adapté à la gestion de tableaux de valeurs.

Les deux formes rencontrées sont:

♦Mnem Dest,offset[base]

♦Mnem Dest,Src1,offset[base]

où:

♦base est un wreg dont le contenu est utilisé par le micro-contrôleur pour former l'adresse de

base de l'opérande.

♦offset est un nombre signé court ( -128 à + 127 ) donc sur 8 bits

♦offset est un nombre signé long ( -32768 à + 32767 ) donc sur 16 bits.

On parle alors d'indexé court ou d'indexé long. Les deux variantes se distinguent d'un octet en + ou en - et

d'un temps de cycle en + ou en -.

Remarque:

Les crochets précisent à l'assembleur que le mode indexé est requis. Suivant la valeur de l'offset,

l'assembleur choisira entre l'indexé court ou long. Finalement, l'adresse d'un opérande en mode indexé est

calculée comme suit par le micro-contrôleur:

adresse opérande = valeur de base + offset

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

1

/

22

100%