Introduction

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Chap. 1. Généralités sur le parallélisme

Les trois dimensions du parallélisme :

1. Le contrôle du parallélisme

2. Le type de mémoire et son accès

3. Granularité du travail

La complexité d’un algorithme parallèle

M. KRAJECKI 1 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Introduction

De nombreux problèmes nécessitent de plus en plus de ressources pour

être résolus

– en informatique : ordonnancement de la production...

– sciences de la terre : météo, pétrole

– applications militaires : simulation d’explosion nucléaire

– biologie / chimie : ADN, simulation moléculaire

La taille mémoire nécessaire est, elle aussi, de plus en plus importante

Pour ces applications et malgré la loi de Moore, l’utilisation du parallélisme

reste la seule solution possible

M. KRAJECKI 2 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Les trois dimensions du parallélisme

Machine séquentielle : il existe une distinction très forte entre le modèle

d’exécution et le modèle de programmation

Modèle d’exécution : machine de von Neumann

Les modèles de programmation sont nombreux : algorithmique classique,

programmation logique et fonctionnelle, programmation orientée objets...

Permet l’écriture de programmes efficaces et indépendants de la machine

cible

Cette distinction n’existe pas en parallélisme

M. KRAJECKI 3 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

1. Le contrôle du parallélisme

Les modèles SIMD et MIMD : historiquement la première classification

introduite par M. J. Flynn (1966)

– SIMD pour Single Instruction Multiple Data : le contrôle est centralisé sur

un seul processeur, les autres processeurs sont synchronisés entre

chaque instruction du même algorithme qu’ils exécutent;

– MIMD pour Multiple Instruction Multiple Data : le contrôle est réparti sur

tous les processeurs et la synchronisation, lorsqu’elle est nécessaire, est

réalisée par communication. Chaque processeur peut exécuter un

algorithme différent;

– SPMD pour Simple Program Multiple Data : un seul programme est

dupliqué sur l’ensemble des processeurs. Les processeurs sont

synchronisés par bloc d’instructions.

M. KRAJECKI 4 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Le modèle BSP

Le modèle BSP (Bulk Synchronous Parallel) a été proposé en 1990 par L. G.

Valiant.

C’est à la fois :

– un modèle d’exécution (comme la machine de von Neumann)

– un modèle de programmation pour le parallélisme.

M. KRAJECKI 5 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Le modèle d’exécution BSP

BSP est caractérisé par les propriétés suivantes :

– le système est composé d’un ensemble de processeurs qui exécutent des

programmes qui peuvent être différents;

– le système dispose d’un réseau de communication permettant des

communications point à point entre n’importe quelle paire de processeurs;

– il existe un mécanisme de synchronisation efficace pour un sous

ensemble ou pour tous les processeurs.

M. KRAJECKI 6 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Le modèle d’exécution BSP

Les performances obtenues par une machine BSP sont déterminées à l’aide

de 4 paramètres :

– le nombre de processeurs, la puissance de chaque processeur

– le coût de synchronisation et celui de communication.

Le nombre de processeurs ainsi que leur puissance ont évidemment une

influence directe sur les performances globales du système.

Si une étape est une instruction de calcul de base (une opération en virgule

flottante), la puissance de chaque processeur mesurée en nombre d’étapes

réalisées par seconde.

M. KRAJECKI 7 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Le modèle d’exécution BSP

Les capacités du réseau d’interconnexion jouent également un rôle

prépondérant.

On mesure le coût d’une synchronisation en nombre d’étapes : nombre

d’opérations qu’aurait pu réaliser un processeur pendant le temps

nécessaire à la synchronisation.

Mesure du coût d’une communication en nombre d’étapes par mot machine.

Si le coût d’une communication est de 5 étapes par mot machine, et qu’un

processeur envoie un message dont la longueur est de 1 mot, il est bloqué

pendant 5 étapes.

M. KRAJECKI 8 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

Le modèle de programmation BSP

Le modèle de programmation BSP s’appuie sur la notion de super étape

(superstep).

– Un programme BSP est constitué d’un certain nombre de super étapes.

– Entre chaque étape, il y a synchronisation des processeurs et échange de

messages.

– Une super étape est composée de plusieurs étapes qui s’appliquent à des

données locales.

– Les communications sont autorisées et non bloquantes. La terminaison

de chaque communication intervient au plus tard à la barrière de

synchronisation qui termine la super étape courante.

L’approche BSP permet d’écrire un programme indépendant de la machine

cible : pourra être exécutée sur un réseau de stations de travail comme sur

une machine parallèle.

M. KRAJECKI 9 Maîtrise Informatique

SDP 2 Chap. 1 – Généralités sur le parallélisme

'

&

$

%

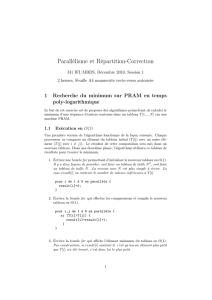

2. Le type de mémoire et son accès

Ce critère spécifie les caractéristiques de la mémoire et du système de

communication entre les processeurs.

Ces caractéristiques sont essentielles dans la définition d’une mesure de

complexité et d’efficacité d’un algorithme parallèle.

Une mémoire peut être partagée par l’ensemble des processeurs. Les

processeurs communiquent par l’intermédiaire de cette mémoire. Le modèle

associé est nommé PRAM pour Parallel Random Access Memory

M. KRAJECKI 10 Maîtrise Informatique

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

1

/

23

100%