ChapII bascules et automates.rtf

- II.1 -

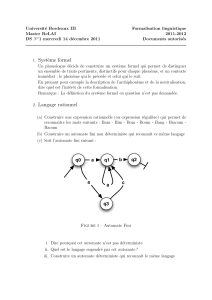

CHAPITRE II :

CIRCUITS SEQUENTIELS ET SYNTHESE D'AUTOMATES

INTRODUCTION

Un circuit séquentielest un circuit dont la sortie dépend de la séquence d'entrées appliquées

depuis la mise en route du circuit :ce circuit mémorise une information. La valeur de

l'information mémorisée forme l'état du circuit ;le support de cette information est les

variables d'états. Ces variables étant binaires, un circuit séquentiel ànvariables d'état peut

prendre 2n états.

Nous n'étudierons ici que les circuits séquentiels synchrones :les changements de valeur de

chacune des variables d'état sont synchronisés par un signal ;quand ce signal n'est pas actif,

l'état ne peut pas être modifié.

Après avoir présenté l'élément de base des circuits séquentiels :les bascules, et leur utilisation

pour réaliser des registres (§1), le modèle d'automate synchrone sera présenté (§2), ainsi que

les méthodes de synthèse d'automates (§3).

1. CIRCUITS SEQUENTIELS DE BASE : BASCULES ET REGISTRES

1.1. DEFINITION

Une bascule est un circuit séquentiel élémentaire, capable de mémoriser une variable d'état et

- II.2 -

donc qui peut prendre 2états (état 0et état 1). Il existe différents types de bascules, qui

peuvent être classés par :

-leurs entrées de valeur,

-l'interprétation de leur(s) entrée(s) d'activation,

-les entrées d'initialisation dont elles disposent.

1.2. BASCULE D

Une bascule D(pour Delay) synchrone est un circuit à2états, qui aune entrée de valeur D,

une entrée d'activation Act, et 2 sorties y (état de la bascule) et .

La figure II-1 définit les entrées et sorties d'une bascule D, ainsi que son tableau de

fonctionnement.

D

Act

y

y

a) schéma symbolique d'une bascule D

y t : valeur courante de l'état

y t+?t : valeur suivante de l'état

Act D yt+?t

non * yt

oui 0 0

oui 1 1

b) fonctionnement

Figure II-1 : bascule D

Tant qu'il n'y apas activation de la bascule (Act :non), la bascule garde son état antérieur,

quelle que soit la valeur de l'entrée D. Quand la bascule est activée (Act :oui), l'état de la

bascule prend la valeur de l'entrée D:une bascule Dpermet de mémoriser une valeur entre

deux activations.

La bascule Dest la plus utilisée, en particulier pour réaliser des registres, mais il existe d'autres

bascules avec des entrées de valeurs différentes.

1.3. BASCULES JK, RS, ...

Les bascules JK, RS et T sont définies ci-dessous (figures II-2 à II-4).

- II.3 -

Act

y

y

a) schéma symbolique d'une bascule RS

Act R S yt+?t

non * * yt

oui 0 0 yt

oui 0 1 1

oui 1 0 0

oui 1 1 ???

b) fonctionnement

R

S

Figure II – 2 : bascule RS

Act

y

y

a) schéma symbolique d'une bascule JK

Act J K yt+?t

non * * yt

oui 0 0 yt

oui 0 1 0

oui 1 0 1

oui 1 1 yt

b) fonctionnement

J

K

Figure II-3 : bascule JK

T

Act

y

y

a) schéma symbolique d'une bascule T

Act T y t+?t

non * yt

oui 0 yt

oui 1 yt

b) fonctionnement

Figure II-4 : bascule T

Une bascule Dpeut être réalisée àpartir d'une bascule RS (avec S=Det Rcomplémentaire)

ou d'une bascule JK (avec J=Det Kcomplémentaire). Une bascule Tpeut être réalisée à

partir d'une bascule JK (avec J et K = T).

1.4. FONCTIONS D'ACTIVATIONS DES BASCULES

On distingue trois types de bascules d'après la fonction d'activation (l'interprétation de l'entrée

Act).

- II.4 -

1.4.A.BASCULES DE TYPE VERROU (LATCH)

Il s'agit de bascules sensibles à la valeur de l'entrée Act :

-verrou sensible au niveau haut : la bascule est activée dès que (et tant que) Act = 1,

-verrou sensible au niveau bas : la bascule est activée dès que (et tant que) Act = 0,

ce qui veut dire que quand la bascule est activée, son état est égal à la valeur de l'entrée D : un

verrou est "transparent" quand il est activé.

Le fonctionnement temporel d'un verrou Dsensible au niveau haut est indiqué àl'aide d'un

chronogramme donné dans la figure II-5 :la figure II-5 a) illustre le fonctionnement de type

verrou, tandis que la figure II-5 b) met en évidence les retards associés au fonctionnement (en

fait, c'est plus complexe :les retards sont différents suivant que l'état passe de 0à1 ou de 1à

0 ; de plus, les retards sont différents pour la sortie y et la sortie .

Act

D

y ?

a) verrou sensible au niveau haut

?? ??

? t2? t1

Act

D

y

b) retards de positionnement de y

par rapport à Act ( ? t1) et D (? t2)

Figure II-5 : fonctionnement temporel d'un verrou D

Si l'entrée Dchange "au moment où" l'entrée d'activation Act passe de 1à0(pour un verrou

sensible au niveau haut), l'état de la bascule après la fin de l'activation est indéterminé :on ne

sait pas si la nouvelle valeur de l'entrée aété mémorisée ou non. Des intervalles de temps t1

(temps de positionnement, tset-up)et t2 (temps de maintien, thold)définissent l'intervalle de

temps où D doit être stable autour du passge de Act de 1 à 0.

1.4.B.BASCULES SENSIBLES AU FRONT (EDGE-TRIGGERED FLIP-FLOPS)

Il s'agit de bascules sensibles aux changements de valeurs de l'entrée d'activation Act :

-bascule sensible au front montant : la bascule est activée quand Act passe de 0 à 1,

-bascule sensible au front descendant : la bascule est activée quand Act passe de 1 à 0,

ce qui veut dire qu'une telle bascule ne peut changer d'état qu'à des instants bien précis :la

(les) entrée(s) de valeur sont échantillonnées aux fronts de l'entrée d'activation.

- II.5 -

Act

D

y ? ??

? t

Act

D

y

a) bascule sensible au front montant

? ?

t1 t2

b) l'entrée D doit être stable autour

du front montant de Act

Figure II-6 : fonctionnement temporel d'une bascule D sensible au front

La figure II-6 illustre le fonctionnement temporel d'une bascule Dsensible au front montant :il

faut que Dsoit stable t1 avant le front de Act (temps de positionnement, set-up time) et t2

après le front (temps de maintien, hold-time). La sortie varie ∆taprès le front de l'horloge. A

noter :ce retard est différent suivant le sens de variation ;passage de 0à1: tpLH,passage de

1 à 0 : tpHL.

Au lieu d'utiliser la notation "état àt+∆t", on peut se contenter de définir le fonctionnement

d'une bascule sensible au front en termes de l'état àt + 1 en fonction de l'état et des entrées à

t, car les fronts d'activation des bascules permettent une discrétisation du temps.

1.4.C.UTILISATION DES DIFFERENTS TYPES DE BASCULES

Supposons qu'on veuille concevoir un circuit à2états, qui complémente son état àchaque

activation (séquence d'états 0101010.....). Il semble logique d'utiliser le montage de la figure

II-7 :

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

1

/

40

100%