Introduction aux architectures et programmes parallèles Accélération

1

Introduction aux architectures et

programmes parallèles

Daniel Etiemble

de@lri fr

de@lri

.

fr

Accélération

• Accélération (p processeurs) =

• Pour un problème de taille fixe (entrées fixées),

Performance (p processeurs)

Performance (1 processeur)

performance = 1/temps

• Accélération à problème fixé

– (p processeurs) = Temps (1 processeur)

Temps (p processeurs)

IFIPS-2

Calcul parallèle D. Etiemble 2

2

Amdahl et Gustafson

S: Temps séquentiel

P: Temps parallélisable Application extensibleApplication fixe

() SP

Acc n P

Sn

.

() SaP

Acc n SP

Amdahl Gustafson

P = a*n

Ts = S+P = fs + (1

fs)

IFIPS-2

Calcul parallèle D. Etiemble 3

() 1/

ns

A

cc n f

Ts

=

S+P

=

fs

+

(1

-

fs)

Tp = S+P/n = fs +(1-fs)/n Ts = S+P = fs + n (1-fs)

Tp = S+P/n = fs +(1-fs)

() 1

s

s

f

E

nf

n

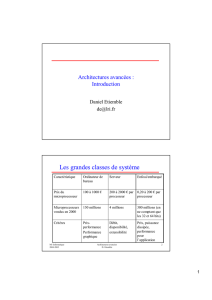

Classification de Flynn

• Flot d’instructions x Flot de données

– Single Instruction Single Data (SISD)

– Single Instruction Multiple Data (SIMD)

– Multiple Instruction Single Data

– Multiple Instruction Multiple Data (MIMD)

• “Tout est MIMD” !

IFIPS-2

Calcul parallèle D. Etiemble 4

3

SIMD

• Modèle d’exécution

–CM2

– Maspar

Contrôleur

PE PE PEML ML ML

Lancement instructions

• Modèle obsolète pour machines parallèles

– Processeurs spécifiques différents des CPU standards

– Lancement des instructions incompatible avec les fréquences

d’horloge des microprocesseurs modernes

Shiti èh itti litti

Réseau d’interconnexion

IFIPS-2

Calcul parallèle D. Etiemble 5

–

S

ync

h

ron

i

sa

ti

on apr

è

s c

h

aque

i

ns

t

ruc

ti

on :

l

es

i

ns

t

ruc

ti

ons

conditionnelles sont synchronisées

• SPMD

• Extensions SIMD dans les microprocesseurs

Version SPMD du SIMD

• Modèle d’exécution

CPU CPU CPUML ML ML

– Chaque CPU exécute le même code.

– Les CPU sont synchronisés par des barrières avant les transferts

de données.

• Clusters de PCs

–PC

Réseau d’interconnexion

IFIPS-2

Calcul parallèle D. Etiemble 6

–Ethernet

4

Organisation mémoire du MIMD

Mémoire centralisée Espace d’adressage unique Accès mémoire uniforme

Mémoire

Mémoire @Max

Mémoire

+

Mémoire distribuée Plusieurs espaces d’adressage Accès mémoire non uniforme

PE PE

Réseau

PE

Réseau

PE PE PE

@0

@Max @Max @Max

PE PE

12 3

6

912 3

6

9

Mémoire

Mé i

Mémoire Mémoire Mémoire

Opposé

Complexité

IFIPS-2

Calcul parallèle D. Etiemble 7

PE PE PE

Mémoire

Mémoire

Mémoire

PE PE PE

@0 @0 @0

PE PE

12 3

6

912 3

6

9

Mé

mo

i

re

-

Classification mémoire (MIMD)

Mémoire

Mé i é

Mé i di ib é

Mé

mo

i

re partag

é

e

Mé

mo

i

re

di

str

ib

u

é

e

SMP ccNUMA MMP Hybrid Clusters

P1

Ch

Pn

PE

PE

Réseau

PE

IFIPS-2

Calcul parallèle D. Etiemble 8

Composants d’E/S

Mémoire

Cache

C

ac

h

e

Modèle mémoire SMP

Bus

PE

PE

PE

Mémoire

Mémoire

Mémoire

5

Multi-thread et multiprocesseurs

Processeur

logique 1 Processeur

logique 2 Processeur

physique 1 Processeur

physique 2

Unités fonctionnelles

Etat archit.

(registres) Etat archit.

(registres)

Caches

Unités

fonctionnelles

Etat archit.

(registres) Etat archit.

(registres)

Caches

Unités

fonctionnelles

Caches

IFIPS-2

Calcul parallèle D. Etiemble 9

Mémoire principale Mémoire principale

Multiprocesseurs et multi-cœurs

CPU State

Cache

Execution

unit

CPU State

Cache

Execution

unit

unit

Multiprocesseur

Cache

unit

CPU State

Cache

Execution

unit

CPU State

Cache

Execution

unit

IFIPS-2

Calcul parallèle D. Etiemble 10

D. Etiemble 10

Multi-cœurs

CPU State

Execution

unit

CPU State

Cache

Execution

unit

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%