Cours n°1

Cours d’info2 : microcontrôleur

«!mid-range!» pic16fxxx

Eric Nativel

IUT Nîmes - GEII – S2

Année universitaire 2014 – 2015

processeur mémoire carte d’extension

écran

clavier, souris

stockage de masse

usb

série

parallèle

ethernet

Bus de données

Bus d’adresse

Bus de contrôle

->uC pic

Processeur

•CPU : Central Unit Processor == unité de traitement de données

•== «!cerveau!» de tout système informatique

•gère et contrôle les opérations arithmétiques et logiques des

processus informatiques

•Ne comprend que le langage binaire == suite de codes binaires

uniques pour 1 type de processeur donné

–Architecture CISC : jeu d’instructions puissantes non limités, temps

d’exécution variable

–Architecture RISC : jeu d’instructions réduits simple, temps d’exécution

garanti et optimisé

•Algorithme codé en assembleur premier langage informatique :

–Assembleur correspondance mnémonique vers code binaire

Ex: LD 0x12,w

– bas niveau -> langage C, langage évolué

Ex : printf(‘‘coucou‘‘);

retour

Contenu d’un CPU

•Une UAL pour effectuer des opérations arithmétiques et

logiques.

•Un registre d'instruction associé à un décodeur

permettant de décomposer et d'organiser l'exécution de

l'instruction.

•Un certain nombre de registres internes, pour stocker

temporairement des données ou les bits de conditions.

•Un système de gestion d'adresses, permettant la

localisation des informations, qu'elles soient données ou

instructions.

•Un ensemble de Bus, permettant de véhiculer soit des

données, Bus de données, soit des adresses, Bus

d'adresse, soit des informations permettant de contrôler

ces transferts, Bus de contrôle.

Mémoires

•Mémoire morte (Read Only Memory): garde

le contenu en absence d’alimentation (non

volatile), vitesse d’accès lente

–ROM, PROM (vraiment «!Read Only!»), EPROM,

EEPROM, UVPROM, flash

•Mémoire vive (Random Access Memory) :

perd le contenu de la mémoire en absence

d’alimentation (volatile), vitesse d’accès

rapide

–RAM, DRAM, SRAM, MRAM (non volatile)

retour

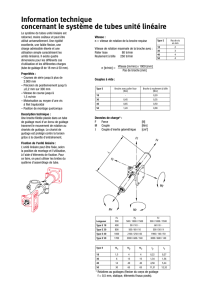

Bus

•Bus d’adresse : permet de sélectionner un

composant selon son adresse sur le

système

•Bus de contrôle : permet de contrôler ces

transferts

•Bus de données : véhicule les données

entre les différents composants du

système

retour

Microcontrôleur / Microprocesseur

•Microcontrôleur = processeur + mémoires

+ périphériques (module d’interface)

Microcontrôleur : pic16f877

Microcontrôleur : pic16f877

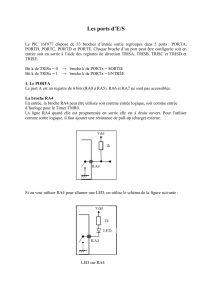

structure pic16f877

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

1

/

15

100%