Document

Chapitre 2

Du siliciure au transistor à grille TOSI

Les siliciures ont été largement étudiés depuis la fin des années 70’s. La large variété des

composés et la complexité de leurs transitions de phase ont motivé des efforts continus dans le

domaine des études fondamentales de ces matériaux. Aujourd’hui, quelques siliciures occupent une

place stratégique dans l’industrie microélectronique, et plus particulièrement le siliciure de nickel

Néanmoins, les mécanismes de formation des siliciures restent très complexes. Aussi, nous verrons

dans une première partie la formation des siliciures métalliques à travers l’exemple du siliciure de

nickel. Nous nous intéresserons alors aux raisons qui ont motivées son implémentation. Puis nous

présenterons le module de siliciuration et l’état de l’art de la grille totalement siliciurée.

61

Chapitre 2 Du siliciure au transistor à grille TOSI________________________________________61

1.1 Formation des siliciures ______________________________________________________65

1.1.1 Réaction limitée par la nucléation___________________________________________67

1.1.1.1 Théorie classique de la nucléation ____________________________________68

1.1.1.2 Formation contrôlée par la nucléation _________________________________69

1.1.2 Réaction limitée par la diffusion____________________________________________70

1.1.2.1 La croissance linéaire parabolique (Loi de Deal & Grove): Exemple de la

croissance d’une unique phase MxSiy________________________________________70

1.1.2.2 Cas de la croissance simultanée de deux phases (ou plus)__________________72

1.1.2.3 Principaux paramètres et caractéristiques ______________________________73

1.1.3 Croissance séquentielle et absence de certaines phases __________________________74

1.2 Vers le siliciure de nickel pour les technologies CMOS_____________________________75

1.2.1 Limitations du CoSi2_____________________________________________________76

1.2.1.1 Augmentation de la résistance dans les petites dimensions_________________76

1.2.1.2 Consommation de silicium problématique pour les jonctions fines et les substrats

SOI__________ ________________________________________________________77

1.2.1.3 Incompatibilité du siliciure de cobalt avec les substrats SiGe _______________77

1.2.2 Avantages du NiSi ______________________________________________________78

1.2.2.1 Réduction du budget thermique______________________________________78

1.2.2.2 Une résistivité faible pour une consommation réduite de silicium ___________79

1.2.2.3 Réduction du bridging et de la formation de voids _______________________79

1.2.2.4 Formation d’une phase peu résistive possible sur substrat SiGe _____________80

1.2.3 Challenges du NiSi ______________________________________________________81

1.2.3.1 Formation des phases du système Ni-Si _______________________________81

1.2.3.2 Découvertes récentes sur la séquence de phase du système Ni-Si____________83

1.2.3.3 Diffusion du nickel________________________________________________85

1.2.3.4 Dégradation du NiSi à haute température: NiSi et NiSi2___________________86

1.2.3.5 Contraintes induites par le siliciure de nickel ___________________________88

1.3 Module de siliciuration nickel standard _________________________________________89

1.3.1 Nettoyage de la surface à siliciurer __________________________________________89

1.3.2 Le dépôt de nickel et d’une couche d’encapsulation_____________________________89

1.3.3 Premier recuit de siliciuration (RTA1)_______________________________________90

1.3.4 Le retrait sélectif du métal n’ayant pas réagi __________________________________91

1.3.5 Deuxième recuit de siliciuration (RTA2)______________________________________91

1.4 La grille métallique totalement siliciurée ________________________________________91

1.4.1 Principaux siliciures pour les applications TOSI _______________________________92

1.4.2 Intégration de la grille TOSI _______________________________________________93

1.4.3 Ajustement du travail de sortie effectif_______________________________________93

1.4.3.1 Modulation par ségrégation de dopants ________________________________94

1.4.3.2 Modulation par formation d’alliages à base de nickel _____________________95

62

Chapitre 2 : Du siliciure au transistor à grille totalement siliciurée

1.4.3.3 Modulation par contrôle de la phase formée ____________________________96

1.4.4 Théories sur la modulation du travail de sortie et le Fermi pinning _________________98

1.4.4.1 Le concept de travail de sortie _______________________________________98

1.4.4.2 Modulation du travail de sortie des grilles TOSI________________________100

1.4.4.3 Introduction des diélectriques high-k et «Fermi level pinning»_____________102

1.5 Conclusions _______________________________________________________________109

Bibliographie _____________________________________________________________________111

63

64

Chapitre 2 : Du siliciure au transistor à grille totalement siliciurée

Chapitre 2

Du siliciure au transistor à grille totalement siliciuré

1.1 Formation des siliciures

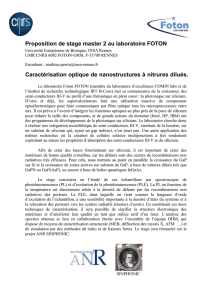

Ayant des propriétés de conduction voisines de celles des métaux, les siliciures ont été

largement étudiés. La grande variété des composés et la complexité de leurs transitions de phase ont

motivé des efforts continus. Sur la Figure II. 1 sont répertoriés la plupart des éléments pouvant se

combiner avec le silicium pour former des siliciures:

IA VIII

H4Si II

A

IIIB IVB

V

B

V

IB

V

IIB

Li22Si5

Li15Si4

Li21Si8

Li2Si

B6Si

B4Si

B3Si

Csi N4Si3Osi

O2Si F4Si

NaSi

NaSi2Mg2Si IIIA IVA VA VIA VIIA VIIIA IB IIB AlSi Si PSi

PSi2S2Si

Ssi Cl4Si

KSi

KSi6Ca2Si

CaSi

CaSi2

Sc5Si3

ScSi

Sc2Si3

Sc3Si5

Ti5Si3

Ti5Si4

TiSi

TiSi2 (C49)

TiSi2 (C54)

V3Si

V5Si3

V6Si5

VSi2

Cr3Si

Cr5Si3

CrSi

CrSi2

Mn6Si

Mn9Si2

Mn3Si

Mn5Si2

MnSi

Mn15Si26

Mn27Si47

Mn11Si19

Fe3Si

Fe2Si

Fe5Si3

FeSi

FeSi2

Co3Si

Co2Si

CoSi

CoSi2

Ni3Si

Ni31Si12

Ni2Si

Ni3Si2

NiSi

NiSi2

Cu5Si

Cu15Si4

Cu3Si

As2Si

AsSi SeSi

Se2Si Br4Si

Rb2Si

RbSi

RbSi6

RbSi8

SrSi

SrSi2Y5Si4

Y5Si3

YSi

Y3Si5

Zr2Si

Zr5Si3

Zr3Si2

ZrSi

ZrSi2

Nb3Si

Nb5Si3

NbSi2

Mo3Si

Mo5Si3

MoSi2

Tc4Si

Tc5Si3

TcSi

TcSi2

Ru2Si

Ru5Si3

Ru4Si3

RuSi

Ru2Si3

Rh2Si

Rh5Si3

Rh20Si13

RhSi

Rh4Si5

Rh3Si4

Pd5Si

Pd9Si2

Pd4Si

Pd3Si

Pd2Si

PdSi

Pd4Si20

Te3Si2

Te2Si

TeSi

I4Si

CsSi

CsSi3BaSi

BaSi2La5Si3

La5Si2

La3Si2 (*)

LaSi

LaSi2

Hf2Si

Hf5Si2

Hf5Si3

Hf3Si2

Hf5Si4

HfSi

HfSi2

Ta3Si

Ta2Si

Ta5Si3

TaSi2

W5Si3

WSi2Re5Si3

ReSi

ReSi2

OsSi

Os2Si3

OsSi1,8

OsSi2

Ir3Si

Ir2Si

Ir4Si5

Ir3Si4

IrSi1,75

IrSi3

Pt3Si

Pt12Si5

Pt2Si

Pt6Si5

PtSi

(**)

(*) Ce3Si2

Ce5Si3

CeSi

CeSi2

Pr3Si2

PrSi3

PrSi

PrSi2

Nd5Si3

NdSi

NdSi2

Sm5Si3

SmSi

SmSi2

EuSi

EuSi2Gd5Si3

GdSi

GdSi2

Tb5Si3

TbSi

TbSi2

Dy5Si3

DySi

DySi2

Ho5Si3

HoSi

HoSi2

Er5Si3

ErSi

ErSi2

Tm5Si3

TmSi

TmSi2

Yb5Si3

YbSi

YbSi2

Lu5Si3

LuSi

LuSi2

(**)

Th3Si2

ThSi

Th3Si5

ThSi2

U3Si2

Usi

U2Si3

USi2

USi3

NpSi3

NpSi2Pu5Si3

Pu3Si2

Pu2Si3

PuSi

PuSi2

AmSi

AmSi2CmSi

Cm2Si3

CmSi2

Métaux de transition

Terres rares

IA VIII

H4Si II

A

IIIB IVB

V

B

V

IB

V

IIB

Li22Si5

Li15Si4

Li21Si8

Li2Si

B6Si

B4Si

B3Si

Csi N4Si3Osi

O2Si F4Si

NaSi

NaSi2Mg2Si IIIA IVA VA VIA VIIA VIIIA IB IIB AlSi Si PSi

PSi2S2Si

Ssi Cl4Si

KSi

KSi6Ca2Si

CaSi

CaSi2

Sc5Si3

ScSi

Sc2Si3

Sc3Si5

Ti5Si3

Ti5Si4

TiSi

TiSi2 (C49)

TiSi2 (C54)

V3Si

V5Si3

V6Si5

VSi2

Cr3Si

Cr5Si3

CrSi

CrSi2

Mn6Si

Mn9Si2

Mn3Si

Mn5Si2

MnSi

Mn15Si26

Mn27Si47

Mn11Si19

Fe3Si

Fe2Si

Fe5Si3

FeSi

FeSi2

Co3Si

Co2Si

CoSi

CoSi2

Ni3Si

Ni31Si12

Ni2Si

Ni3Si2

NiSi

NiSi2

Cu5Si

Cu15Si4

Cu3Si

As2Si

AsSi SeSi

Se2Si Br4Si

Rb2Si

RbSi

RbSi6

RbSi8

SrSi

SrSi2Y5Si4

Y5Si3

YSi

Y3Si5

Zr2Si

Zr5Si3

Zr3Si2

ZrSi

ZrSi2

Nb3Si

Nb5Si3

NbSi2

Mo3Si

Mo5Si3

MoSi2

Tc4Si

Tc5Si3

TcSi

TcSi2

Ru2Si

Ru5Si3

Ru4Si3

RuSi

Ru2Si3

Rh2Si

Rh5Si3

Rh20Si13

RhSi

Rh4Si5

Rh3Si4

Pd5Si

Pd9Si2

Pd4Si

Pd3Si

Pd2Si

PdSi

Pd4Si20

Te3Si2

Te2Si

TeSi

I4Si

CsSi

CsSi3BaSi

BaSi2La5Si3

La5Si2

La3Si2 (*)

LaSi

LaSi2

Hf2Si

Hf5Si2

Hf5Si3

Hf3Si2

Hf5Si4

HfSi

HfSi2

Ta3Si

Ta2Si

Ta5Si3

TaSi2

W5Si3

WSi2Re5Si3

ReSi

ReSi2

OsSi

Os2Si3

OsSi1,8

OsSi2

Ir3Si

Ir2Si

Ir4Si5

Ir3Si4

IrSi1,75

IrSi3

Pt3Si

Pt12Si5

Pt2Si

Pt6Si5

PtSi

(**)

(*) Ce3Si2

Ce5Si3

CeSi

CeSi2

Pr3Si2

PrSi3

PrSi

PrSi2

Nd5Si3

NdSi

NdSi2

Sm5Si3

SmSi

SmSi2

EuSi

EuSi2Gd5Si3

GdSi

GdSi2

Tb5Si3

TbSi

TbSi2

Dy5Si3

DySi

DySi2

Ho5Si3

HoSi

HoSi2

Er5Si3

ErSi

ErSi2

Tm5Si3

TmSi

TmSi2

Yb5Si3

YbSi

YbSi2

Lu5Si3

LuSi

LuSi2

(**)

Th3Si2

ThSi

Th3Si5

ThSi2

U3Si2

Usi

U2Si3

USi2

USi3

NpSi3

NpSi2Pu5Si3

Pu3Si2

Pu2Si3

PuSi

PuSi2

AmSi

AmSi2CmSi

Cm2Si3

CmSi2

Métaux de transition

Terres rares

Figure II. 1:Principaux siliciures pouvant être formés à partir des éléments de la classification périodique [Maex’95].

65

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

1

/

66

100%