Annexe fiche 4 : Introduction aux Entrées/Sorties

!Polytech Marseille/Dépt Informatique A3– 2016/2017! !TP Interface Matériel Logiciel!

1/4

Annexe fiche 4 : Introduction aux Entrées/Sorties

Léon Mugwaneza

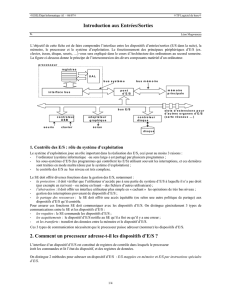

L’objectif de cette annexe est de faire comprendre l’interface entre les dispositifs d’entrées/sorties1 (E/S dans la

suite), la mémoire, le processeur et le système d’exploitation (aussi nommé SE dans la suite). Le fonctionnement

des principaux périphériques d’E/S (ex. clavier, écran, disque, souris, …) vous sera expliqué dans le cours

d’Architecture des ordinateurs au second semestre. La figure 1 ci-dessous donne le principe de l’interconnexion

des divers composants matériels d’un ordinateur.

Figure 1 : Interconnexion des composants matériels d’un ordinateur. Les dispositifs d’entrées/sorties sont

contrôlés par des processeurs spécialisés (on parle de contrôleurs ou adaptateurs d’E/S). Les contrôleurs d’E/S sont

connectés à un bus d’E/S lui même connecté à la mémoire et au processeur à travers un pont d’E/S.

1. Contrôle des E/S : rôle du système d’exploitation

Le système d’exploitation joue un rôle important dans la réalisation des E/S, ceci pour au moins 3 raisons :

- l’ordinateur (système informatique -au sens large-) est partagé par plusieurs programmes ;

- les sous-systèmes d’E/S (les programmes qui contrôlent les E/S) utilisent souvent les interruptions, et ces

dernières sont traitées en mode maître (donc par le système d’exploitation) ;

- le contrôle des E/S au bas niveau est très complexe.

Le SE doit offrir diverses fonctions dans la gestion des E/S, notamment :

- la protection : il doit vérifier que l’utilisateur n’accède pas à une partie du système d’E/S à laquelle il n’a pas

droit (par exemple en écrivant – ou même en lisant – des fichiers d’autres utilisateurs) ;

- l’abstraction : il doit offrir un interface utilisateur plus simple en « cachant » les opérations de très bas

niveau ;

- la gestion des interruptions provenant de dispositifs d’E/S ;

- le partage des ressources : le SE doit offrir un accès équitable (ou selon une autre politique de partage) aux

dispositifs d’E/S qu’il contrôle.

Pour assurer ces fonctions, le SE doit pouvoir communiquer avec les dispositifs d’E/S. On distingue

généralement 3 types de communications entre le SE et les dispositifs d’E/S :

- les requêtes : le SE commande les dispositifs d’E/S ;

- les acquittements : le dispositif d’E/S notifie au SE qu’il a fini ou qu’il y a une erreur ;

- et les transferts : transfert des données entre la mémoire (ou le processeur) et le dispositif d’E/S.

Ces 3 types de communication nécessitent que le processeur puisse adresser (nommer) les dispositifs d’E/S.

2. Comment un processeur adresse-t-il les dispositifs d’E/S ?

L’interface d’un dispositif d’E/S est constitué de registres de contrôle (dans lesquels le processeur écrit les

commandes et lit l’état du dispositif) et de registres de données. On distingue 2 méthodes pour adresser un

dispositif d’E/S : Entrées/Sorties mappées en mémoire et Entrées/Sorties par instructions spéciales d’E/S.

1 Aussi appelés périphériques d’entrées/sorties

mémoire

principale

pont

d‘E/S

interface bus

UAL

registres

processeur

bus système

bus mémoire

controleur

disque

adaptateur

graphique

controleur

USB

souris

clavier

écran

disque

bus E/S

slots d‘extensions pour

d‘autres organes d‘E/S

(carte réseaux …)

!Polytech Marseille/Dépt Informatique A3– 2016/2017! fiche E/S – TP4 !TP Interface Matériel Logiciel!

2/4

2.1. E/S mappées en mémoire

Le dispositif d’E/S est dans l’espace d’adressage mémoire (cf. figure 2 ci-dessous). L’écriture ou la lecture des

registres du dispositif d’E/S sont faites avec les instructions d’accès à la mémoire. Tous les systèmes peuvent

utiliser les entrées sorties mappées en mémoire, certains processeurs (ex. MIPS, Motorola) n’offrent que cette

alternative.

Figure 2 : E/S mappées en mémoire

Le simulateur SPIM simule un terminal mappé en mémoire (deux dispositifs d’E/S) :

- entrées à partir du clavier (receiver) : 2 registres ;

- sorties sur l’écran (transmitter) : 2 registres.

La figure 3 ci-dessous montre les adresses affectées au terminal SPIM (les 4 mots aux adresses 0xffff0000,

0xffff0004, 0xffff0008, et 0xffff000c) :

Figure 3 : E/S mappées en mémoire du simulateur SPIM

La signification des registres du terminal SPIM est la suivante :

Bit de poids faibles du registre de contrôle (0) : Ready

- Receiver : Ready = 1 signifie que le caractère dans le registre de données est prêt et n’a pas encore été lu ;

Ready passe de 1 à 0 quand le registre de données est lu.

- Transmitter : Ready = 1 signifie que le transmitter est prêt à accepter un nouveau caractère ;

Ready = 0 signifie que le transmitter est encore occupé à écrire le dernier caractère.

Bit 1 du registre de contrôle : I.E. (voir 4.2 : Fonctionnement des E/S par interruptions – l’exemple de SPIM).

Octet de poids faibles du registre de données :

- Receiver : dernier caractère tapé au clavier (lecture seule).

- Transmitter : l’octet écrit dans ce registre est “affiché” au terminal (écriture seule). Lorsque ce registre est écrit,

le bit Ready du Transmitter passe à 0 pendant un temps suffisamment long pour que le caractère soit écrit à

l’écran, puis repasse à 1.

2.2. E/S par instructions spéciales d’E/S

Le jeu d’instructions définit des instructions dédiées aux opérations d’E/S (ex. instructions in et out des

processeurs INTEL). Dans ce dernier cas, il y a donc deux espaces d’adressage : un espace d’adressage mémoire

et un espace d’adressage E/S (cf figure 4). On notera que dans un système où le processeur offre des instructions

d’E/S, on peut évidemment utiliser des E/S mappées en mémoire.

Received

Byte

Receiver

Data

0xffff0004

Unused

(00...00)

(IE)

Receiver Control

0xffff0000

Ready

(I.E.)

Unused

(00...00)

Transmitted

Byte

Transmitter Control

0xffff0008

Transmitter

Data

0xffff000c

Ready

(I.E.)

Unused

(00...00)

Unused

cntrl reg

.

data

reg

.

0xFFFFFFFF

0xFFFF0000

@

M

E

M

O

I

R

E

0

!Polytech Marseille/Dépt Informatique A3– 2016/2017! fiche E/S – TP4 !TP Interface Matériel Logiciel!

3/4

Figure 4 : E/S par instructions spéciales d’E/S

3. Comment protège-t-on les E/S ?

Les opérations d’E/S doivent être protégées. Dans le cas des E/S mappées en mémoire, les adresses

correspondant aux dispositifs d’E/S sont protégées par le mécanisme de gestion mémoire. Elles sont allouées

dans la partie de l’espace d’adressage réservée au système d’exploitation.

Dans le cas des E/S par instructions spéciales, les instructions d’E/S sont des instructions privilégiées qui ne

peuvent être exécutées qu’en mode maître.

4. Comment le dispositif d’E/S notifie-t-il au processeur qu’il est prêt ?

On distingue deux façons de faire :

- E/S par polling (scrutation) : le processeur « consulte » le registre de contrôle du dispositif d’E/S « tout le

temps » pour voir si le dispositif est prêt ;

- E/S par interruptions : le dispositif d’E/S a un mode de fonctionnement dans lequel il interrompt le

processeur quand il a terminé une opération d’E/S.

4.1. E/S par polling : exemple du terminal SPIM

Pour lire un caractère du clavier et le ranger dans $v0, on utilise (par exemple) la séquence suivante :

li $t0, 0xffff0000 # Adresse du registre de contrôle dans $t0

# Attendre que le bit ready soit à 1

Waitloop: lw $t1, 0($t0) #control

andi $t1, $t1, 0x0001

beq $t1, $0, Waitloop

# ready = 1 : on peut lire dans le registre de données

lw $v0, 4($t0) #data

Pour écrire à l’écran le caractère dans $a0, la séquence suivante peut être utilisée :

li $t0, 0xffff0000

# Attendre que le bit ready soit à 1

Waitloop: lw $t1, 8($t0) #control

andi $t1, $t1,0x0001

beq $t1, $0, Waitloop

# ready = 1 : on peut écrire dans le registre de données

sw $a0, 12($t0) #data

cntrl reg.

data reg.

0

0xFFFFFFFF

@ E/S

0

0xFFFFFFFF

@ Mémoire

Mémoire

cntrl reg.

data reg.

!Polytech Marseille/Dépt Informatique A3– 2016/2017! fiche E/S – TP4 !TP Interface Matériel Logiciel!

4/4

4.2 Fonctionnement des E/S par interruptions.

La figure 5 rappelle le principe du contrôle des E/S par interruptions. Le programme utilisateur est interrompu

par le dispositif d’E/S (1), l’interruption est prise en compte par le processeur en sauvegardant un contexte

minimal et en allant exécuter le traitant d’exceptions en mode maître interruptions masquées (2 et 3), le traitant

d’exceptions détermine le service demandé et réalise le transfert (4) avant de revenir au programme interrompu

(5).

Figure 5 : Contrôle des E/S par interruption (le principe)

E/S par interruptions : exemple du terminal SPIM

Le Bit I.E. (Interrupt Enable) du registre de contrôle permet de configurer le dispositif d’E/S dans un mode de

fonctionnement par interruptions. Si le bit I.E a la valeur 1, une interruption est générée à chaque fois que le

bit Ready passe de 0 à 1.

Le clavier (receiver) interrompt le processeur sur le niveau 0. L’écran (transmitter) interrompt le processeur sur

le niveau 1.

Mémoire

(1) interruption

d’E/S

(2) sauvegarder le contexte

add ...

sub ...

and ...

or ...

programme

utilisateur

lw …

sw …

…

jr …

traitant d’IT

(3) aller exécuter

le traitant d’IT

(4) réaliser le

transfert

(5) Retour au

Prg. utilisateur

1

/

4

100%