Evaluation de la robustesse de circuits intégrés vis-à

N°d'ordre : 02ISAL0044 Année 2002

Thèse

Evaluation de la robustesse de circuits

intégrés vis-à-vis des décharges

électrostatiques

Présentée devant

L’Institut National des Sciences Appliquées de Lyon

Pour obtenir

Le grade de docteur

Formation doctorale : Dispositifs de l’Electronique Intégrée

École doctorale : Electronique, Electrotechnique et Automatique

Par

Agnès GUILHAUME

(Ingénieur)

Soutenue le 20 Septembre 2002 devant la Commission d’examen

Jury MM.

M. BAFLEUR Directeur de recherche Rapporteur

J-P. CHANTE Professeur

Y. DANTO Professeur Rapporteur

P. GALY Professeur assistant

M. LEMITI Maître de conférences

I. LOMBAËRT-VALOT Chef de service

Thèse préparée dans le service Composants Electroniques et Optoélectroniques du

Centre Commun de Recherches du groupe EADS France

Le réel n’est jamais « ce qu’on pourrait croire »

mais il est toujours ce qu’on aurait dû penser.

Gaston Bachelard

5HPHUFLHPHQWV

Le travail présenté dans ce mémoire a été réalisé au Centre Commun de Recher-

ches (CCR) du groupe EADS, en collaboration avec l’INSA de Lyon et le Pôle

Universitaire Léonard de Vinci (Paris-La-Défense), dans le cadre d’une convention

avec l’ADERA (Association pour le Développement de l’Enseignement et des Re-

cherches auprès des universités, des centres de recherches et des entreprises

d’Aquitaine).

A l’issue de cette thèse, je souhaite remercier Monsieur M. Lecoq pour m’avoir

accueillie dans le département « Techniques de base physique et mathématiques »

du CCR. Je tiens également à témoigner toute ma reconnaissance à Madame

I. Lombaërt-Valot, responsable du service « Composants électroniques et opto-

électroniques » pour les encouragements, le suivi et la confiance qu’elle m’a ac-

cordés au cours de ces trois années et des trois années de stage précédentes.

Je remercie sincèrement Monsieur B. Foucher pour m’avoir proposé ce sujet et

pour m’avoir encadrée dans ce travail. Par ses compétences, ses grandes qualités

humaines et ses précieux conseils, il a rendu ce travail particulièrement intéressant.

Sans les discussions que nous avons eues, cette étude n’aurait pu aboutir.

Je témoigne toute ma reconnaissance à Monsieur JP. Chante, professeur à l’INSA

de Lyon, pour avoir accepté de diriger cette thèse. Je remercie également Monsieur

P. Galy, chargé de recherche et professeur assistant au Pôle Universitaire Léonard

de Vinci, d’avoir co-dirigé ces travaux avec tant d’intérêt et de disponibilité. La

clarté de leurs analyses et leurs qualités scientifiques m’ont permis de progresser.

Qu’ils trouvent ici le témoignage de ma profonde reconnaissance.

J’adresse également mes remerciements aux personnes qui ont accepté de partici-

per à mon jury de thèse : à Madame M. Bafleur, directeur de recherche au LAAS

de Toulouse et à Monsieur Y. Danto, professeur à l’IXL de Bordeaux, qui en qua-

lité de rapporteurs, ont jugé mon travail et porté une grande attention à la relecture

de ce mémoire, ainsi qu’à Monsieur M. Lemiti, maître de conférence à L’INSA de

Lyon.

Ce travail a été réalisé en étroite collaboration avec la société STMicroelectronics.

Je tiens à remercier Monsieur P. Salomé, Mademoiselle C. Richier et les membres

de leurs équipes. Ils ont rendu ces échanges possibles et m’ont fait part de leur ex-

périence de fabricants dans le domaine des ESD. Ces semaines passées sur les sites

de Crolles et du Polygone ont été très enrichissantes.

De nombreux travaux de mesures et de simulations ont aussi été réalisés en colla-

boration avec Philips Composants à Caen. Je dois beaucoup à Monsieur S. Bardy,

Monsieur F. Blanc et à Monsieur S. Dufrenne pour leur accueil, leurs conseils et

pour la confiance qu’ils m’ont accordée pendant ces trois années.

Je tiens à remercier Monsieur Guerveno et Monsieur Caignard du service Expertise

et Technologie Composant de la société MBDA pour leurs observations EMMI.

J’en profite également pour témoigner, à l’équipe du service « Composants électro-

niques et optoélectroniques », ma profonde sympathie : en particulier à Madame C.

Munier, qui m’a accueillie au cours de mes premiers stages au CCR et qui a ac-

cepté de relire mon manuscrit et à Agnès, Alix, Alain, Christophe, Faresse, Gregor,

Guillaume, « Maître » Hieu, Jean-Pierre, Julien, Laëtitia, Olivier, Patrick, Régis,

Vincent et aux nombreux stagiaires. Certains d’entre eux sont déjà partis vers

d’autres horizons. Pour d’autres, cette année sera décisive, aussi, je leur adresse

mes encouragements.

Enfin, c’est avec beaucoup d’émotion que je remercie mes parents, mes frères et

sœurs, Nicolas et tous mes amis pour le soutien et la confiance qu’ils m’ont tou-

jours accordés.

6RPPDLUH

1

3

6

12

15

1.1 Introduction. 16

1.2 Modèles de décharges 16

1.2.1 Tests en qualification 17

1.2.2 Tests d’aide à la conception 21

1.2.3 Discussion 24

1.3 Phénomènes physiques et modes de défaillances associés aux ESD 25

1.3.1 Effets parasites du boîtier 25

1.3.2 Réponse d’un transistor MOS à une décharge électrostatique 26

1.3.3 Modes de défaillances et techniques d’analyses 28

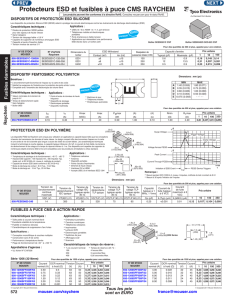

1.4 Protection des composants électroniques contre les décharges électrostatiques 32

1.4.1 Protection des circuits intégrés 32

1.4.2 Structures de protection 34

1.4.3 Procédés technologiques. 36

1.5 Conclusions 39

41

2.1 Introduction 42

2.2 Procédés de fabrication 43

2.2.1 Simulation des principales étapes technologiques 43

2.2.2 Calibrage des résultats 43

2.2.3 Discussions 44

2.3 Comportement physique 45

2.3.1 Formalisme et équations locales 45

2.3.2 Résolution numérique 51

2.3.3 Simulation du test TLP 55

2.3.4 Simulation du test HBM 59

2.3.5 Simulation du test CDM 60

2.3.6 Discussions 66

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

141

141

142

142

143

143

144

144

145

145

146

146

147

147

148

148

149

149

150

150

151

151

152

152

153

153

154

154

155

155

156

156

157

157

158

158

159

159

160

160

161

161

162

162

163

163

164

164

165

165

166

166

1

/

166

100%