Université Montpellier II

Université Montpellier II

SODINI MODICOM 1 Page 1 21/11/2007

MODICOM 1

Cette plaquette montre comment un signal peut être échantillonné, transmis comme une suite d’échantillons, puis

reconstitué à l’aide de filtres passe-bas.

I) Le bloc de logique de commande d’échantillonnage (« Sampling control logic ») :

Il fabrique une commande d’échantillonnage à différentes fréquences (2, 4, 8, 16, 32 kHz) et d’ouvertures

réglables (10% à 90%).

Il comprend un compteur BCD d’horloge réglable d’un facteur 10 par rapport à la fréquence d’échantillonnage

désirée. Cette horloge est obtenue à la sortie d’un multiplexeur (5 vers 1). Le compteur est suivi d’un

comparateur sur 4 bits qui permet de faire varier l’ouverture de l’échantillonneur.

Manipulation :

Observer le chronogramme du compteur BCD à l’aide de l’analyseur logique : broches 14 (horloge), 20, 19, 18,

17. (La broche (pin) 20 est le poids faible du compteur). A l’aide des curseurs faire apparaître la période du

compteur.

Faire une copie d’écran.

En vous plaçant sur la commutation de l’état 7 à 8 (par exemple) et en augmentant la base de temps, montrer que

les changements d’état ne sont pas tout à fait synchrones ce qui induit des « glitch » au moment de la

comparaison.

Le chiffre à comparer est fixé par le bouton « duty cycle selector ». Si par exemple, il est fixé à 3, les broches 24

à 21 sont : 3

124

123

022

021

=

=

=

=

=

pin

pin

pin

pin

. Le comparateur est câblé pour que le chiffre du compteur soit <3

compteur 7 8 9 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 5 6

comparateur 0 0 0 1 1 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0

Pour supprimer les « glitchs », on fait passer le signal de la broche 25 (pin25) par une bascule D « Latch » qui

déclenche sur le front opposé à celui de l’horloge du compteur.

Faire une copie d’écran de l’analyseur logique comportant l’horloge (pin 14) la sortie du compteur (broches 20 à

17), la sortie du comparateur (pin 25) et la sortie Q du « latch » (pin 26).

II Le bloc d’échantillonnage :

Le signal que l’on vient de fabriquer (pin 29) sert de commande à un interrupteur à transistors Mos qui est suivi

de 2 ampli-ops montés en suiveurs dont l’un possède une capacité à l’entrée qui empêche le retour à 0

(« Sampling/hold output »).

Manipulation :

Période compteur

30%

Pin 25

glitch

fH

Université Montpellier II

SODINI MODICOM 1 Page 2 21/11/2007

En utilisant la sinusoïde fabriquée par la plaquette, avec une horloge à 40 kHz et un rapport cyclique à 50%, faire

une copie d’écran de la sinusoïde d’entrée et des sinusoïdes échantillonnées.

Si la fréquence de l’horloge du compteur est de 40 kHz, quelle est la fréquence d’échantillonnage ?

Si maintenant on utilise une sinusoïde à 1kHz fabriquée par un générateur basses fréquences (bouton « sampling

control » sur la position « internal », injectez la sinusoïde du GBF sur l’entrée « Analog Input »), on constate

que la trace sur l’oscilloscope n’est plus stable.

Il est pratiquement impossible de fabriquer une sinusoïde qui a strictement la même fréquence f que celle

fabriquée par la plaquette : fff

∆

+

=

'.

On peut écrire :

[

]

)(2sin)22sin()'2sin( tftftfttf

ϕ

π

π

π

π

+

=

∆

+

=

Il apparaît donc une phase qui dépend du temps φ(t) et qui n’est nulle que si ∆f = 0.

III Le bloc de reconstitution des signaux :

Les filtres passe-bas permettent de reconstituer le signal.

Manipulation :

On analysera les spectres du signal reconstitué à l’aide de l’analyseur de spectre.

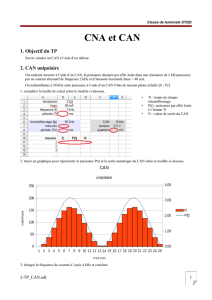

A) Cas de l’échantillonnage naturel (« sample output » via un filtre passe-bas).

On se placera dans les conditions suivantes : fréquence d’échantillonnage Féch à 4 kHz, rapport cyclique à 50%.

La sinusoïde (pin 30), la commande de l’échantillonnage (pin 29) et la sinusoïde échantillonnée (pin 33)

visualisées sur l’oscilloscope ont l’allure des courbes a, b et c. La courbe (c) est le résultat de la multiplication

dans l’espace des temps des courbes (a) et (b).

Commande

(pin 29)

Dans le domaine des fréquences (à vérifier avec l’analyseur de spectre), la sinusoïde a pour spectre la courbe

(d) :

Si f est exprimé en kHz :

)1f(

2

1

)1f(

2

1

)f(M −δ++δ=

1

-1 2 1

m(t)

t ms

0

(a)

Tech

xP(t)

2

t ms

0

1

(b)

d

xnat(t)

t ms

1 2

0

(c)

Université Montpellier II

SODINI MODICOM 1 Page 3 21/11/2007

Spectre de la commande (broche 29) : Un train d’impulsions de fréquence f, d’amplitude A et de durée d centrée

sur l’origine des temps, a pour coefficients de Fourier :

)(sin

)sin( nfd

T

Ad

nfd

nfd

T

Ad

Ccn ==

π

π

Cette relation s’écrit avec A=1, d/T = 0,5 et f = 1/T = 1/2d = 4 kHz :

2

/

)2/sin(

2

1

)2/(sin

2

1

π

π

n

n

nC cn ==

D’où le spectre : )n4f(C)f(X

n

nP ∑

∞

−∞= −δ= n exprime des kHz.

=

=

=π

=

0nsi2/1

pairnsi0

impairnsi/n

Cn

Le rapport cyclique 0,5 supprime dans le spectre les raies paires ce qui simplifie les spectres obtenus.

Le spectre de la sinusoïde échantillonnée (courbe f) est le résultat de la convolution (à vérifier avec l’analyseur

de spectre) :

−δ∗

−δ++δ=∗= ∑

∞

−∞=n

nPnat )n4f(C)1f(

2

1

)1f(

2

1

)f(X)f(M)f(X

1/2δ

(f + 1)

1/2

|M(f)|

-12 -8 -4 0 4 8 12 16 20 24 f Khz

(d)

1/

π

1/2

)(sin

2

1fd

c

|XP(f)|

-12 -8 -4 0 4 8 12 16 20 24 f Khz

(e)

Université Montpellier II

SODINI MODICOM 1 Page 4 21/11/2007

En utilisant : )1n4f()n4f()1f(

−

−

δ

=

−

δ

∗

−

δ

)1n4f()n4f()1f(

+

−

δ

=

−

δ

∗

+

δ

[ ]

∑

∞

−∞= +−δ+−−δ=

n

nnat )1n4f()1n4f(

2

1

C)f(X

Le spectre de la sinusoïde après filtrage est donné par la courbe (h). On vérifiera que les raies à 3 et 5 kHz sont

affectées par la bande passante des filtres (2ème et 4ème ordre).

La sinusoïde après filtrage (visualisée sur l’oscilloscope) a pour spectre non seulement la raie fondamentale à

1 kHz mais 2 raies parasites à 3 et 5 kHz (figure g).

Si on double la fréquence d’échantillonnage f = 8 kHz, le spectre de la sinusoïde échantillonnée devient :

Le spectre de la sinusoïde échantillonnée après filtrage est donné par la courbe (i). On vérifiera que seule la raie

fondamentale reste, les raies à 7 et 9 kHz ont quasiment disparues.

Conclusions ?

1/2

π

1/4

)(sin

4

1fd

c

|Xnat(f)|

-12 -8 -4 0 4 8 12 16 20 24 f Khz

(f)

|Xfiltré(f)|

-12 -8 -4 0 4 8 12 16 20 24 f Khz

(g)

Fondamental

Bande passante du filtre

1/2

π

1/4

)(sin

4

1fd

c

|Xnat(f)|

-12 -8 -4 0 4 8 12 16 20 24 f Khz

(h)

Université Montpellier II

SODINI MODICOM 1 Page 5 21/11/2007

B) Cas de l’échantillonnage bloqué (« sample/hold output » via un filtre passe-bas).

On se placera dans les conditions suivantes : fréquence d’échantillonnage Féch à 4 kHz, rapport cyclique à 50%.

Les différents spectres obtenus ont été étudiés en cours.

|Xfiltré(f)|

-12 -8 -4 0 4 8 12 16 20 24 f Khz

(i)

Fondamental

Bande passante du filtre

1

/

5

100%