Caches et mémoire virtuelle

1

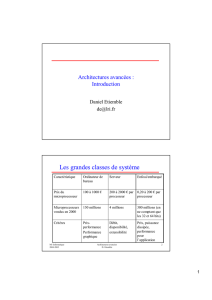

Architectures des ordinateurs

Caches et mémoire virtuelle

Daniel Etiemble

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

2

Capacité mémoire

1K

10K

100K

1M

10M

100M

1978 1981 1984 1987 1990 1993 1996

DRAM

SRAM

(bits)

Date d’apparition

X 4 tous les trois ans

LB LB

LM

Q Q

Point mémoire SRAM

(6 transistors)

Point mémoire DRAM

(1,5 transistors)

≈0.5 T

Surface SRAM/DRAM = 4

Coût bit SRAM/DRAM = 10

2

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

3

Caractéristiques temporelles des DRAM

année

1980 1983 1986 1989 1992

50

100

150

200

250

Temps de cycle

Temps d’accès ligne

lent

rapide

Temps d’accès colonne

64 Ko 256 Ko 1 Mo 4 Mo 16 Mo

ns

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

4

Le “gap” des performances mémoire

1

10

100

1000

10000

80

82

84

86

88

90

92

94

96

98

2000

CPU

DRAM

Croissance besoins CPU : 50 à 60%/an

Décroissance latence DRAM : 8 à 10%/an

3

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

5

Evolution des hiérarchies mémoire

(1985-2000)

CPU L1

cache MM

System bus

a)

CPU

+

L1 caches MM

L2

cache

System bus

b) System bus

L2

cache

Superscalar

CPU

+

L1 caches

Special bus

MM

d)

MM

L2

cache

Superscalar

CPU

+

L1 caches

c)

System bus

System bus

Superscalar

CPU

+

L1 caches

Special bus

MM

RDRAM

e)

L2 CACHE

Pentium Pro

Pentium

PentiumII

Pentium 4

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

6

Principe des caches

• Fondés sur le principe de localité

• Mémoires de taille et vitesse différentes

• Organisation

– Découpage en lignes (blocs)

– Mécanisme de correspondance

• Placement des lignes dans le cache

• Détection succès ou échec

– Gestion de la cohérence

CPU

Cache Mémoire principale

Ligne

4

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

7

Principe de localité

• Localité spatiale

– Si on accède à une case mémoire, on accédera à une case

proche

• Localité temporelle

– si on accède à une case mémoire, on y accédera

probablement très bientôt (ou dans très longtemps ou

jamais !)

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

8

Mécanismes de correspondance

01234567 01234567

0 1 2 3

01234567

ADRESSE LIGNE

Mémoire principale

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

OU PLACER UNE LIGNE DE LA MP DANS LE CACHE ?

Correspondance directe Totalement associatif Associatif deux voies

5

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

9

Correspondance directe

= ?

Bits de

contrôle

5

ETIQUETTE INDEX Adresse Octet

dans le Bloc

j

ETIQUETTE

i/NB

0

NB - 1

OUI : Succès

NON :

Echec

J (cache) = i (MP) mod NB, avec NB = nombre de lignes du cache

L3 Informatique - IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

10

Associativité totale

Bits de

contrôle

5

ETIQUETTE Adresse Octet

dans le Bloc

j

ETIQUETTE

0

NB - 1

=

=

=

NB

comparaisons

1 égalité = Succès

0 égalité = Echec

Ligne i(MP) dans n’importe quelle ligne j du cache.

Etiquette = i, et NB comparateurs pour détecter succès ou échec

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

1

/

26

100%