Introduction

1

Architecture des ordinateurs

Introduction

Daniel Etiemble

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

2

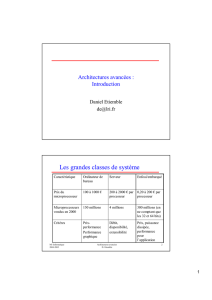

Les grandes classes de système

Prix, puissance

dissipée,

performance

pour

l’application

Débit,

disponibilité,

extensibilité

Prix-

performance

Performance

graphique

Critères

300 millions (en

ne comptant que

les 32 et 64 bits)

4 millions150 millionsMicroprocesseurs

vendus en 2000

0,20 à 200 €par

processeur

200 à 2000 €par

processeur

100 à 1000 €Prix du

microprocesseur

Enfoui/embarquéServeurOrdinateur de

bureau

Caractéristique

2

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

3

Ventes des microprocesseurs

(fin du siècle dernier ☺)

• Processeurs enfouis/embarqués

– 4 bits : 2 milliards

– 8 bits : 4,7 milliards

– 16 bits : 700 millions

– 32 bits : 400 millions

• DSP (traitement du signal)

– 600 millions

• Généralistes classiques

– 150 millions

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

4

Les applications

• Usage général

• Calcul Scientifique

•

•GRAPHIQUE

GRAPHIQUE

• Traitement du signal

•

•JAVA

JAVA

• BD

• WEB

• Enfoui et embarqué

3

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

5

PERFORMANCE

• Nombre d’instructions

– Jeu d’instructions et compilateur

• CPI

– Microarchitecture

• T

c

– Technologie CMOS et Microarchitecture

Nombre de cycles/Instruction

Temps de cycle

NI

IPC * F

T

exécution

= NI * CPI * T

c

=

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

6

DES EXPONENTIELLES

CPU

0% 10% 20% 30% 40% 50% 60%

Fréquence d'horloge (MOS)

Performance avant 1986

Performance après 1987

Evolution/an

MICROPROCESSEURS

2x/1,5an

4

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

7

DES EXPONENTIELLES

MEMOIRES

0% 20% 40% 60%

Capacité

Latence

DISK DRAM

2x/1,5an

0,5/10 ans

Evolution/an

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

8

’70 ’73 ’76 ’79 ’82 ’85 ’88 ’91 ’94 '97 2000

’70 ’73 ’76 ’79 ’82 ’85 ’88 ’91 ’94 '97 2000

Transistors

Transistors

Per Die

Per Die

10

10

8

8

10

10

7

7

10

10

6

6

10

10

5

5

10

10

4

4

10

10

3

3

10

10

2

2

10

10

1

1

10

10

0

0

1K

1K

4K

4K 16K

16K

64K

64K

256K

256K

1M

1M

16M

16M

4M

4M

64M

64M

4004

4004 8080

8080

8086

8086

80286

80286 i386

i386™

™

i486

i486™

™Pentium

Pentium

®

®

Memory

Memory

Microprocessor

Microprocessor

Source: Intel

Source: Intel

Pentium

Pentium

®

®

II

II

Moore’s Law

Pentium

Pentium

®

®

III

III

256M

256M

Pentium

Pentium

®

®

Pro

Pro

5

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

9

LES DIFFERENTIELS

1

10

100

1000

10000

80

82

84

86

88

90

92

94

96

98

2000

CPU

Mémoire

Complexité croissante de la hiérarchie mémoire

IFIPS2

2007-08

Architecture des ordinateurs

D. Etiemble

10

Densité de puissance

Watts/cm

2

1

10

100

1000

1.5µ

1.5µ1.5µ

1.5µ 1µ

1µ1µ

1µ 0.7µ

0.7µ0.7µ

0.7µ 0.5µ

0.5µ0.5µ

0.5µ 0.35µ

0.35µ0.35µ

0.35µ 0.25µ

0.25µ0.25µ

0.25µ 0.18µ

0.18µ0.18µ

0.18µ 0.13µ

0.13µ0.13µ

0.13µ 0.1µ

0.1µ0.1µ

0.1µ 0.07µ

0.07µ0.07µ

0.07µ

i386

i386

i486

i486

Pentium

Pentium®

®

Pentium

Pentium®

®Pro

Pro

Pentium

Pentium®

®II

II

Pentium

Pentium®

®III

III

Hot plate

Hot plate

Nuclear Reactor

Nuclear

Nuclear Reactor

Reactor

*

* “

“New Microarchitecture Challenges in the Coming Generations of CM

New Microarchitecture Challenges in the Coming Generations of CMOS Process Technologies

OS Process Technologies”

”–

–

Fred Pollack, Intel Corp. Micro32 conference key note

Fred Pollack, Intel Corp. Micro32 conference key note -

-1999.

1999.

Pentium

Pentium®

®4

4

Rocket

Nozzle

6

6

7

7

8

8

9

9

10

10

11

11

12

12

1

/

12

100%