Techniques de Test pour les Convertisseurs Analogiques/Numériques

Projet, ELE 6306 (Test de systèmes électroniques)

Techniques de Test pour les Convertisseurs

Analogiques/Numériques

I.Benamrane, M. Hamine,

École Polytechnique de Montréal - Département de Génie Électrique – AUT2004

Résumé

Ce projet présente des techniques de test proposées dans la

littérature, pour tester les circuits analogiques et mixtes, en

particulier les convertisseurs analogiques/numériques; parmi ces

techniques il y’a quelques-unes basées sur le test industriel

(externe), d’autres utilisant des structures d’autotest intégré

(BIST). Ce travail tient compte aussi d’une technique de

génération de rampe linéaire, en utilisant l’auto-calibration dans

le but de générer un signal analogique précis à l’intérieur du

circuit à tester.

1. Introduction

De nos jours, les circuits intégrés (CI) utilisés en industrie sont

généralement mixtes, c'est-à-dire composés d’une partie

analogique et une autre numérique. L’élément charnière entre ces

deux parties est le convertisseur Analogique/Numérique (CAN).

L’évaluation de ces circuits analogiques et mixtes passe alors

obligatoirement par le test de ce convertisseur, ce qui peut être

une tâche très difficile. Le problème principale provient du fait

que la plus part des circuits mixtes sont testés en mode

fonctionnel. Cela nécessite des ressources de test externes

extrêmement coûteuses, ce qui le rend à la fois très cher et très

compliqué à réaliser. Pour contourner cette difficulté, des

solutions attractives consistent à développer des structures de

tests intégrés BIST (built in self test), dans lesquelles la

génération de signaux de tests et l’analyse des résultats sont

performés à l’intérieur du circuit.

Dans la deuxième partie de ce travail, on élabore les techniques

du test industriel des CAN qui d’habitude se font à l’externe et se

basent généralement sur une analyse fonctionnelles de ses

paramètres. Ces paramètres se divisent en deux groupes. :

• Paramètres statiques tels que l’erreur de gain, l’erreur

d’offset et la non-linéarité différentielle et intégrale. Ces

paramètres sont généralement analysés en utilisant la

technique du test par histogramme.

• Paramètres dynamiques tels que le rapport signal sur

bruit plus distorsion (SINAD : signal-to-noise and

distortion ratio), la dynamique de codage (SFDR :

Spurious-free Dynamique Range) ou le taux de

distorsion harmoniques (THD), le jitter et le taux de

distorsion par intermodulation (IMD). Ces paramètres

sont généralement évalués en utilisant une analyse

spectrale basée sur une transformée de fourrier rapide

FFT.

Par la suite, des techniques de test interne seront introduites. Ces

techniques se divisent en deux catégories :

• Test intégré nécessitant des ressources matérielles tels

que Bist avec CNA, HBIST et MADBIST.

• Test intégré ne nécessitant pas de ressources matérielles

tels que BIST utilisant la technique du LSB et la

technique OBIST.

Finalement, on conclura notre travail par un exemple de

génération de signaux linéaires de test intégrés, soit un

générateur de rampe linéaire.

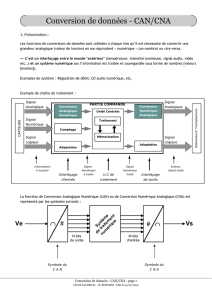

2. Test industriel des CAN

Pour les convertisseurs analogiques/numériques, comme pour la

plus part des circuits analogiques et mixtes, le test se fait

généralement selon l’approche fonctionnelle. Ce type de test sert

seulement à vérifier certaines fonctionnalités du circuit et non

pas la détection de présence de défauts au niveau de la structure

du circuit. Le test fonctionnel s’avère très fiable mais peut être

très long et très coûteux à réaliser. En industrie deux types de

tests sont couramment utilisés pour tester ces convertisseurs.

2.1 Test par analyse spectrale

Le principe est d’envoyer un signal sinusoïdal sur l’entrée du

CAN, appliquer une transformée de fourrier rapide (FFT : Fast

Fourrier Transform) sur une longueur T finie et analyser la

réponse du circuit dans le domaine fréquentiel. Ainsi, on pourra

évaluer les distorsions et bruits introduits par la quantification.

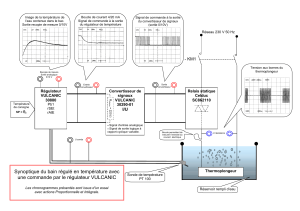

L’opération d’échantillonnage s’effectue comme le montre la

figure (1).

Figure 1. Analyse fréquentielle d’une sinusoïde

Il existe deux techniques d’analyse spectrale :

• technique "single tone",

• technique "dual tone".

2.1.1 Technique ‘single tone’

Cette technique présentée dans [4], consiste à appliquer une

sinusoïde de fréquence pure à l’entrée du convertisseur et l’on

analyse dans le spectre les différentes composantes

fréquentielles. La figure 2 donne un exemple de spectre obtenu

pour un signal d'entrée sinusoïdal pur.

Figure 2. Analyse spectrale ‘single tone’

Cette technique permet d’obtenir le rapport signal sur bruit avec

distorsion SINAD, le taux de distorsion harmonique THD, la

dynamique de codage SFDR et le jitter du convertisseur testé.

2.1.2 Technique ‘dual tone’

Lorsque le signal d’entrée n’est pas une sinusoïde pure, mais une

somme linéaire de plusieurs sinusoïdes de fréquence F1 et F2, on

parle alors d’analyse dual-tone. Cette technique permet de mettre

en évidence tous les phénomènes d’inter-modulation générés par

la conversion de ce signal composite. La figure 3 représente un

exemple de spectre obtenu avec la technique "dual tone".

Figure 3. Analyse spectrale ‘dual tone’

Nous pouvons observer la présence de raies aux fréquences i.F1

+ j.F2 (i et j entiers) qui s'ajoutent aux harmoniques des

composantes du signal d’entrée aux fréquences k1.F1 et k2.F2

(k1 et k2 entier) : ce sont les raies d'inter-modulation. Avec cette

technique de test "dual tone", il est donc possible de déterminer

le taux de distorsion par inter-modulation IMD.

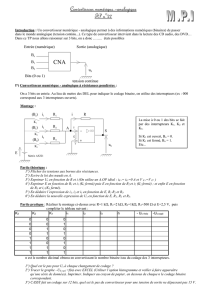

2.2 Test par Histogramme

Cette technique externe proposée dans [3] et [4] est considérée la

plus populaire pour tester les CAN. Elle est basée sur une

analyse statistique de combien de fois un code numérique

apparaît à la sortie du CAN afin de déterminer les paramètres

caractéristiques du CAN. Pour cela, on applique un signal

analogique à l’entrée du convertisseur et on enregistre la

fréquence d’apparition des codes à la sortie du CAN. Ces

échantillons enregistrés forment ce qu’on appelle un

histogramme pour être comparé à un histogramme de référence.

Les résultats des comparaison sont procédés afin de déterminer

les paramètres du CAN tel que, l’erreur du gain, l’erreur d’offset,

la non-linéarité différentielle et intégrale ainsi que les codes

manquants. Le signal à l’entrée du CAN peut être en général

sinusoïdale ou linéaire (rampe ou triangulaire) La figure 4

illustre l’histogramme obtenu en utilisant un signal triangulaire et

sinusoïdal pour un CAN idéal.

Figure 4. Test par histogramme

Généralement, on utilise soit un signal sinusoïdal ou triangulaire

pour former notre histogramme. La technique par histogramme

linéaire (triangulaire), s’avère plus intéressante en terme

d’économie de mémoire pour enregistrer l’histogramme idéal.

L’histogramme au complet peut être représenté avec seulement

deux équations, une correspondante à la valeur idéale des codes

du milieu et l’autre correspondante à la valeur idéale des codes

extrêmes. Un autre désavantage de l’histogramme sinusoïdal est

que ce dernier est plus compliqué à exploiter due à la distribution

non uniforme causé par le signal d’entrée. Quand au signal

triangulaire, chaque code doit démontrer une densité égale. À

cause de sa densité uniforme, il sera facile d’extraire des

expressions simples pour les paramètres du CAN. Les détails sur

ces calculs sont donnés ci-dessous :

• Erreur d’offset : l’offset en (LSB) est proportionnel à la

différence entre la valeurs des deux codes extrêmes.

• Erreur du gain : le gain en (LSB) est simplement donné

par le ratio entre la valeur mesurée du code du milieu et

la valeur idéale.

avec :

• Erreur DNL : La non linéarité différentielle en (LSB)

d’un code i donné est donnée par la différence relative

entre la valeur mesurée et idéale.

• INL : La non linéarité intégrale en (LSB) d’un code i

donné est exprimée comme une somme cumulative de

tous les codes précédents.

Le schéma du test par histogramme est donné à la figure 5

Figure 5. Test par histogramme

Inconvénients:

Les deux techniques de test présentées précédemment se font à

l’extérieur du circuit sous test (DUT), ce qui nécessitent du

matériel de test sophistiqué et coûteux en même temps, ce qui a

poussé d’aller chercher de nouvelles techniques de test pour

réduire le coût soit l’intégration du circuit de test sur la même

puce que le circuit à tester. Il s’agit donc du test intégré (BIST).

Ce dernier est généralement composé de générateur de signal de

test ou de stimulus et d’analyseur de signature. Dans ce qui suit,

quelques techniques du test intégré seront présentées.

3. Techniques de test intégré des CAN

Dans une structure BIST, il faut tenir compte de la surface du

BIST et celle du circuit à tester. Pour cela, les études ont classé

deux structures de test intégré soient : des structures dépendantes

de ressources matérielles initiales (CNA, DSP, ...) et d’autres ne

nécessitant pas de ressources matérielles.

3.1 Test intégré nécessitant des ressources

matérielles initiales

3.1.1 Technique BIST avec CNA

Cette technique proposée en [2] et [3], nécessite un CNA pour

tester le CAN, elle est basée sur la définition d’une marge

obtenue par plusieurs simulations dans le but de définir les deux

histogrammes pour la valeur maximale et la valeur minimale de

la dispersion des paramètres du CAN, la différence des deux

histogrammes définit la marge maximale (gabarit) comme

illustré à la figure 6.

Figure 6. Construction du gabarit de test

Le gabarit construit permet d’évaluer tout histogramme à la

sortie du CAN à tester qui peut être bon si son histogramme est

inclus dans le gabarit, sinon il est considéré défectueux.

3.1.2 Technique HBIST (Hybrid Built-In Self

Test)

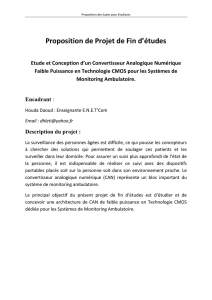

La figure 7 montre cette technique proposée en [5], [6] et [7],

elle est basée sur une structure BIST avec CNA et un processus

de traitement numérique (DSP) pour les circuits mixtes. La

figure 8 illustre la méthode de test qui est similaire à celle du

BIST numérique pour l’analyse de la signature. Les vecteurs de

test sont générés par un registre (LFSR) pseudo-aléatoire (test

structurel) et sont appliqués à l’entrée du CNA pour les convertir

en un signal analogique. Ce dernier s’applique ensuite à l’entrée

du CAN à tester. L’unité ‘DSP’ analyse et compare en même

temps la signature générée à la sortie du CAN avec celle en

mémoire. Le DSP est configuré de façon qu’il contienne les

paramètres attendus du CAN sous test.

Figure 7. Circuit de test typique

Figure 8. Structure HBIST

3.1.3 Technique MADBIST (Mixed Analog-

Digital Built-In Self-Test)

Cette technique proposée en [7], est basée sur la structure HBIST

développée avec (CAN Σ-∆ et CNA Σ-∆), soit un ajout d’un

générateur de sinus numérique et un modulateur pour générer un

signal analogique sinusoïdal précis. Les premières étapes du

diagramme de test sont réservées pour vérifier les éléments du

circuit MADBIST:

• 1ere étape, on teste seulement le convertisseur CAN tout en

en fermant la boucle à l’aide d’un multiplexeur comme le

montre la figure 9. Le signal, provenu du générateur

d’oscillation, est modulé en PDM (Pulse Density

Modulated), et est appliqué directement à l’entrée du CAN,

le bruit est éliminé par le filtre anti-repliement (AAF) tout

en gardant à la sortie du filtre un signal sinusoïdal précis

excitant l’entrée du CAN. La sortie numérique du

convertisseur CAN sera traitée par le DSP tout en séparant

le signal du bruit à l’aide d’un filtre numérique.

Figure 9. Test de ADC (AAF : Filtre anti-repliement)

• 2e étape : après le test du CAN, on vérifie le convertisseur

N/A en passant la boucle par le filtre de lissage par

l’intermédiaire du multiplexeur comme le montre la figure

10. L’entrée du CNA est attaquée par le signal provenu de

l’unité de DSP, et sa sortie est envoyée directement vers le

convertisseur A/N Le DSP caractérise le CNA et même le

filtre de lissage tout en séparant le bruit du signal grâce à

son filtre numérique (FIR, IIR, ...).

Figure10. Test du CNA

• Étape suivante: Après le test du CNA, c’est l’étape de test

du circuit externe (DUT) connecté entre l'entrée et la sortie

du MADBIST, ce test est montré par la figure 11. Le test

réalisé est fonctionnel puisqu’il dépend des paramètres du

circuit sous test, soient le rapport signal sur bruit, le taux de

distorsion et le gain.

Figure 11. Test du DUT (structure MADBIST)

Les paramètres rapport signal sur bruit, gain et taux de distorsion

(harmonique, par inter-modulation) du CAN peuvent être évalués

au niveau DSP.

Inconvénients:

Les éléments ajoutés de la structure MADBIST demandent une

surface peu grande.

Le test ne vérifie pas tous les paramètres du circuit sous test

(offset, NLI, NLD) pour le CAN.

3.2 Test intégré ne nécessitant pas des

ressources matérielles initiales

3.2.1 Technique BIST utilisant la technique du

bit LSB

Cette technique proposée en [1] utilise les propriétés du bit du

poids faible pour déterminer les paramètres du convertisseur. Le

principe est de générer une rampe linéaire à l’entrée du

convertisseur et mesurer l’intervalle de temps entre chaque

commutation du bit de poids faible (LSB). Pour évaluer ces

intervalles, on utilise un compteur qui est incrémenté sur chaque

transition du bit LSB, à la prochaine transition la valeur du

compteur est comparée à la valeur idéale obtenue avec un

convertisseur parfait. La différence de ces deux valeurs donne les

valeurs du NLD et NLI. Ces valeurs seront comparées avec les

valeurs max et min données dans les spécifications du

convertisseur. Cela permet de juger si le convertisseur respecte

bien les spécifications. La figure 12 montre le diagramme du test

pour cette technique.

Figure 12. Test des non-linéarités

3.2.2 Technique OBIST

Cette technique de test proposée dans [8] peut être appliqué à

n’importe quel circuit analogique et mixte selon l’approche

structurelle ou fonctionnelle. Elle consiste à forcer le circuit sous

test à osciller. La fréquence d’oscillation qui est reliée aux

paramètres structurels et fonctionnels du circuit est évaluée. La

déviation de cette fréquence d’oscillation par rapport à la valeur

nominale indique le circuit fautif. Cette méthode a été appliquée

avec succès sur un grand nombre de circuit analogiques et mixte

parmi eux le convertisseur analogique/numérique et a démontré

sa capacité de détection de fautes catastrophique ainsi que

paramétriques. Ainsi, la technique OBIST introduit le CAN dans

une boucle et le force à osciller autour de codes prédéterminés.

La fréquence d’oscillation des deux bits les moins significatifs du

CAN sous test permet de déterminer les paramètres importants

du circuit tel que, le temps de conversion, les non-linéarités

différentielles et intégrales. La figure13 montre la structure de

test basé sur l’approche de boucle. Cette structure est composée

d'un bloc numérique, de deux générateurs de courant, d'un

interrupteur et d'une capacité de charge. Le bloc numérique

commande l'interrupteur pour charger la capacité avec un courant

i ou – i et fournir au convertisseur un signal triangulaire dont la

fréquence dépend des caractéristiques fonctionnelles à évaluer.

Figure 13. Test basé sur l’oscillation du CAN

On vient de voir quelques techniques du test intégré qu’on

utilise pour tester les convertisseurs A/N. Il existe encore

d’autres techniques, sauf qu’on s’est limité à introduire les

plus utilisées en industrie. Le grand défi reste à savoir

comment générer un signal de test à l’intérieur du circuit à

tester. C’est ce qu’on va voir dans la prochaine section.

3.3 Génération internes de signaux de tests

Les techniques de génération de stimuli et d’analyse de signature

internes sont plus complexes et nécessitent des circuits

spécifiques. Généralement les générateurs de stimuli

comprennent: - Des oscillateurs programmables (générateurs

numériques). - Des registres pour génération pseudo-aléatoire

suivis des CNA.

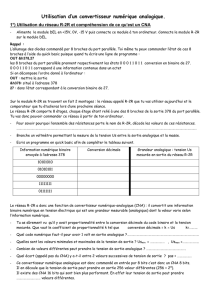

On se limite d’étudier les générateurs de rampe linéaire pour

tester les CAN par histogramme. Deux contraintes devront être

strictement respectées en terme de qualité du signale, soient :

l’amplitude et la précision de la pente qui causent des erreurs de

gain et non-linéarité dont les figures 14 et 15 illustrent

l’histogramme mesuré en présence de ces erreurs.

Figure 14. Erreur due à l’amplitude

Figure 15. Erreur due à la précision de la pente

Le principe de génération de pente linéaire (rampe) peut se faire

soit par intégration d’une tension constante ou par charge et

décharge de capacitance. La 2e idée paraît la bonne puisqu’une

capacité a besoin uniquement d’une source de courant pour être

chargée et déchargée. Alors que la méthode d’intégration de

tension constante, nécessite un Ampli-OP, ce qui est très

demandant en terme de surface. La figure 16 montre le principe

de base pour la charge et décharge de capacitance. La pente est

proportionnelle au temps et est déterminée par l’équation (1) ; la

charge et la décharge de C sont commandées par les interrupteurs

S1 et S2, donc ils déterminent la durée et la pente de la rampe.

(1)

Figure 16. Circuit de charge et décharge linéaire de C

La précision de la pente dépend de la variation du courant Ic et

l’amplitude dépend de la durée T. Le circuit de courant Ic

proposé en [4] est basé de miroir de courant avec excursion

maximale. Or, la linéarité et l’amplitude de la rampe générée ne

peuvent être satisfaites lors de la variation du courant Ic, la figure

17 illustre cette problématique.

Figure 17. La pente de la rampe

La solution proposée est d’ajouter un circuit de compensation

(auto-calibration) qui permet la comparaison des deux tensions et

l’ajustement de la tension Vfinale par le contrôle de Ic comme le

montre la figure 18.

Figure 18. Circuit de compensation

Deux solutions ont été proposées en [4], l’asservissement

numérique et analogique, la 1ère, basée sur un CNA et un

compteur/décompteur, est illustrée par la figure 19, son

diagramme fonctionnel est décrit à la figure 20.

Figure 19. Circuit de compensation

Figure 20. Diagramme fonctionnel

La tension de contrôle Vctr augmente par le comptage jusqu’à ce

que la sortie Vout soit égale à la valeur attendue Vref, en ce

moment là, Vctr oscille autour d’une valeur égale à (+- LSB)

pour asservir la sortie autour de Vref.

Inconvénients:

Les éléments à rajouter (CNA et Compteur), demandent plus de

surface. Une solution est proposée pour réduire la surface est

d’utiliser un CNA cyclique (série) et un compteur/décompteur

classique tel que montré à la figure 21.

6

6

1

/

6

100%