Circuits Logiques Personalisés

CIRCUITS LOGIQUES PERSONALISÉSCIRCUITS LOGIQUES PERSONALISÉS

PIAU J.P. LTR DORIAN Sommaire page 1 / 14

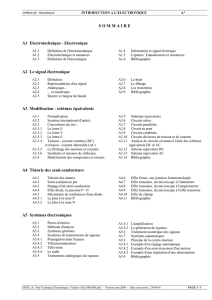

Table des matières

I. Présentation :.........................................................................................................................................................................2

I.1. Généralités :...................................................................................................................................................................2

I.2. Les familles d'ASIC :.....................................................................................................................................................2

II. asic précaractérisés :............................................................................................................................................................ 2

III. asic prédiffusés masquables :.............................................................................................................................................3

III.1. Gate array :..................................................................................................................................................................3

III.2. Réseaux compactés - mers de portes - :.......................................................................................................................3

III.3. Réseaux structurés :.....................................................................................................................................................3

IV. asic prédiffusés programmables :.......................................................................................................................................3

IV.1. Les PROM : ................................................................................................................................................................4

IV.1.1. Les différentes familles :......................................................................................................................................4

IV.1.2. ROM programmables par masque :......................................................................................................................4

IV.1.3. Les PROM à fusibles : .........................................................................................................................................4

IV.1.4. Les UVPROM ou EPROM :................................................................................................................................ 5

IV.1.5. Les OTPROM :....................................................................................................................................................6

IV.1.6. Les EEPROM ou E2PROM :............................................................................................................................... 6

IV.1.7. Les Flash EPROM : .............................................................................................................................................6

IV.2. Les PLD :....................................................................................................................................................................6

IV.2.1. Les différentes familles :......................................................................................................................................6

IV.2.2. Les PAL bipolaires :.............................................................................................................................................7

IV.2.2.1. Notions de base :........................................................................................................................................... 7

IV.2.2.2. Conventions de notation :..............................................................................................................................7

IV.2.2.3. Représentation simplifiée de la structure d'un PAL :....................................................................................8

IV.2.2.4. Les entrées / sorties des PAL : ...................................................................................................................... 9

IV.2.2.5. Le décodage des références :.........................................................................................................................9

IV.2.2.6. Exemple de PAL Combinatoire : le 16 L 8 :...............................................................................................10

IV.2.2.7. Exemple de PAL à registre : le 16 R 8 :...................................................................................................... 11

IV.2.2.8. Les PAL versatiles ou VPAL :....................................................................................................................12

IV.2.2.9. Technologie des PAL bipolaires :...............................................................................................................12

IV.2.3. Les PAL CMOS et GAL :..................................................................................................................................12

IV.2.3.1. Notions de base :......................................................................................................................................... 12

IV.2.3.2. Le GAL 22V10 : ......................................................................................................................................... 12

CIRCUITS LOGIQUES PERSONALISÉSCIRCUITS LOGIQUES PERSONALISÉS

PIAU J.P. LTR DORIAN ASICs page 2 / 14

CIRCUITS LOGIQUES PERSONNALISÉS.

I. PRÉSENTATION :

I.1. Généralités :

La réalisation pratique d’un opérateur logique complexe en logique câblée consiste à utiliser des composants intégrés

disponibles sur le marché. Le problème consiste à optimiser le choix des composants par rapport à des critères de coût, de

performance, du nombre de composants, de la complexité des connexions.

La notion de circuit intégré personnalisé à la demande de l’utilisateur est récente ( 1980 ) et constitue certainement

l’évolution la plus importante de l’électronique depuis l’apparition du microprocesseur dans les années 1970. Les circuits intégrés

à la demande, ou ASIC : Application Specific Integrated Circuits, permettent d’intégrer, sur une surface réduite de semi-

conducteur ( 30 à 40 mm² ), tout ou partie des fonctions complexes propres à un équipement électronique et, ainsi de remplacer

plusieurs circuits.

Quels sont les bénéfices que l’on peut tirer des ASIC par rapport à la solution classique (association de circuits standards)?

Essentiellement une réduction du coût global du système grâce à:

- la diminution du temps de conception obtenue grâce à la CAO;

- la diminution du nombre de circuits intégré nécessaires à la réalisation d’une application résultant de l’optimisation

de l’intégration des fonctions sur la puce;

- la diminution du stock de composants due à des circuits « universels »;

- l’augmentation de la fiabilité;

- une meilleure protection de la propriété industrielle du produit;

Comme cette réduction de coût s’accompagne d’une amélioration des performances, en particulier de la vitesse, que

demander de plus?

Il ne faut pas oublier toutefois que la conception des ASIC passe nécessairement par l’utilisation de moyens de CAO. Tout ce petit

monde n’existerait pas sans les progrès de l’informatique.

I.2. Les familles d'ASIC :

ASIC

Prédiffusés Précaractérisés

Prédiffusés

programmables

( PLD, FPGA )

Prédiffusés

masquables

( Gate Array )

La plupart de ces circuits existent en TLL, CMOS, ECL ou AsGa.

II. ASIC PRÉCARACTÉRISÉS :

Les réseaux précaractérisés font appel à toutes les étapes de fabrication des circuits intégrés: de la diffusion à la

métallisation. Ils sont obtenus par assemblage de fonctions prédéfinies et précaractérisées électriquement par le fabricant de semi-

conducteur. Ces fonctions, fixes ou paramétrables, sont extraites d’une bibliothèque qui est en quelque sorte un catalogue logiciel

dans lequel le client tire les composants qui vont constituer son circuit.

L’étape de conception consiste d’abord à définir l’ensemble des fonctionnalités du circuit afin de juger de sa faisabilité. Il

faut ensuite saisir le schéma logique du circuit. Le concepteur utilise un éditeur de schéma hiérarchisé en liaison avec une

bibliothèque de cellules fournies par le fondeur dans une technologie déterminée. Le simulateur permet ensuite de tester les

fonctionnalités et de détecter les erreurs ou les problèmes de timing. La définition des entrées/sorties sur le boîtier est ensuite faite.

Le résultat des travaux de conception du circuit est la fabrication des masques nécessaires à la réalisation de la puce ( une dizaine

de masques en général ).

Les composants réalisables sont:

- des cellules standards (standards cells ): gamme de circuits pouvant aller du simple transistor aux portes, bascules,

compteurs…

- des mégacellules (mega cells ): ALU, microprocesseur…

- des cellules compilées ( compiled cells ): ROM, RAM, PLD…

CIRCUITS LOGIQUES PERSONALISÉSCIRCUITS LOGIQUES PERSONALISÉS

PIAU J.P. LTR DORIAN ASICs page 3 / 14

III. ASIC PRÉDIFFUSÉS MASQUABLES :

Les réseaux prédiffusés sont des matrices de fonctions logiques déjà diffusées (préparées ) dans le substrat mais non

interconnectées. C’est l’interconnexion des portes qui va personnaliser le circuit en fonction de l’application visée. La réalisation

des interconnexions correspond à l’élaboration par le constructeur des derniers masques nécessaires à la fabrication du circuit.

III.1. Gate array :

Dans le domaine logique, les circuits les plus utilisés sont les réseaux de portes (gate array). Ils sont constitués d’une

matrice de portes à deux entrées placées en colonnes et séparées par des chemins d’interconnexions. En périphérie sont réparties

les blocs d’entrées/sorties. Toutes ces cellules sont interconnectées par 2 ou 3 couches de métallisation.

Caractéristiques essentielles des gate array ( valables en 1990 ... ) :

- nombre de portes équivalents allant jusqu’à 20000 dont au moins 80% effectivement utilisées. Mais ce

pourcentage diminue avec la complexité du problème ;

- le nombre de portes est fonction du nombre de couches de métallisation données par le fabricant et le coût

fonction du nombre de masques nécessaires ;

- existent en TTL, CMOS, ECL, AsGa et même en BiCMOS ;

- temps de propagation élémentaires de quelques 100ps à quelques ns ( fréquence d’horloge de 50MHz à 1GHz )

et des puissances dissipées de 1 à 15W selon les technologies ;

- le routage est effectué par le fabricant de semi-conducteur ou par des ingénieurs ayant accès aux bases de

données du fabricant.

III.2. Réseaux compactés - mers de portes - :

Ce sont des réseaux de portes pour lesquels il n’existe pas de canaux de routage spécialisés, le routage se faisant au-dessus

des portes élémentaires. L’intérêt de cette solution est de permettre d’augmenter le nombre de portes existant sur la puce, la

surface réservée aux chemins d’interconnexions étant ici utilisée par les portes.

III.3. Réseaux structurés :

Ce sont des réseaux de portes prédiffusés auxquels sont associés des fonctions précaractérisées standards: ROM, RAM,

ALU… Ce type de réseau est bien adapté aux applications microinformatiques haut de gamme: traitement du signal, processeur

graphique… C’est une solution intermédiaire avec la solution circuit précaractérisé complet. Elle présente un coût de

développement moins élevé que celui des précaractérisé.

IV. ASIC PRÉDIFFUSÉS PROGRAMMABLES :

Les réseaux logiques programmables sont des circuits intégrés complètements achevés et disponibles sur catalogues. Ils

doivent être personnalisés par l’utilisateur final qui programme les interconnexions entre les différents sous ensembles, inclus dans

le circuit, à l’aide d’un outil de développement associé à un programmateur de circuits. Ils permettent de résoudre la plupart des

problèmes de logique combinatoire ou séquentielle réalisés jusqu’alors par l’association de circuits 74xxnnn biens connus.

La structure classique des PLD (Programmable Logique Device) comporte une partie combinatoire composée de deux

zones de portes ET et OU, une partie séquentielle composée de bascules (D, JK ), et des portes d’interfaçage entrées/sorties figées.

Tout ou partie de ces éléments sont reliés par des fusibles qui sont laissés intacts (liaison présente) ou détruits (pas de liaison)

selon les besoins.

Ces réseaux permettent typiquement de remplacer 4 à 10 circuits intégrés logiques de moyenne complexité. Ils peuvent

êtres utilisés pour remplacer plus de 90% des circuits logiques classiques et ceci avec une vingtaine de références distinctes.

De nouvelles générations de PLD présentant une structure plus modulaire et des blocs d’entrées/sorties plus élaborés,

permettent actuellement d’augmenter encore les possibilités de remplacement.

On peut distinguer deux grandes familles de circuits logiques programmables :

• les mémoires mortes programmables ou PROM : Programmable Read Only Memory, ou encore mémoire

programmable à lecture seule ;

• les circuits logiques programmables ou PLD ;

On distingue pour chacune de ces deux familles, d’autres familles en fonction de différents critères qui sont :

• la nature du fusible ( PLD, PROM, EPLD, EPROM, EEPLD, EEPROM ) ;

• la technologie de réalisation bipolaire (TTL, ECL ) à fusible métalliques ou MOS ( C ou HCMOS) ;

• l’architecture interne du réseau ( ET/OU, modulaire à OLMC, ... ).

CIRCUITS LOGIQUES PERSONALISÉSCIRCUITS LOGIQUES PERSONALISÉS

PIAU J.P. LTR DORIAN Les PROM page 4 / 14

IV.1. Les PROM :

IV.1.1. Les différentes familles :

Elles sont résumées dans le schéma suivant :

Mémoires mortes

PROM

programmables

par l'utilisateur

ROM

programmables

par masque

OTPROM ou EPROM

programmables

une seule fois

EPROM ou PROM

effaçables

PROM

à fusibles

EPROM flash

effaçable

électriquement

EEPROM ou E2PROM

PROM effaçables

électriquement

UVPROM ou PROM

effaçables

aux UV

IV.1.2. ROM programmables par masque :

Les ROM ( Read Only Memory ) ne sont programmées que lors de leur fabrication par action directe sur le masque de

gravure du circuit intégré. Elles sont réservées à des productions en grande série et ne peuvent en aucun cas être programmées

directement par l’utilisateur.

IV.1.3. Les PROM à fusibles :

La zone mémoire d’une PROM ( Programmable Read Only Memory ) à fusible est constituée d’une matrice de fils croisés.

À chaque intersection, une diode en série avec un fusible établissent la liaison entre deux fils. Chaque intersection correspond à un

bit de mémoire. La matrice contient 2N lignes et 8 colonnes ( si mémoire de 8bits...).

Vcc

A0

A1

An

n fils

d'adresse 2

lignes

n

Logique

de

décodage

d'adresse

D0 D1 D2 D3

fusible

Principe des PROM à fusible :

Exemple d'une mémoire 4bits

fusible intact : Donnée = 0

fusible détruit : Donnée = 1

La programmation consiste à griller les fusibles appropriés selon la donnée à mémoriser ( 0 ou 1 ). La programmation est

irréversible. Les diodes sont réalisées soit par des transistors bipolaires soit par des transistors MOS. Les fusibles sont réalisés soit

en diminuant la section de la métallisation des interconnexions lors de la dernière étape de réalisation du circuit, soit par dépôt de

silicium polycristallin à la place de la métallisation d’interconnexion. Dans les deux cas la programmation se fait en appliquant

une impulsion de tension provoquant un courant d’amplitude et de durée permettant la fusion du fusible.

CIRCUITS LOGIQUES PERSONALISÉSCIRCUITS LOGIQUES PERSONALISÉS

PIAU J.P. LTR DORIAN Les PROM page 5 / 14

IV.1.4. Les UVPROM ou EPROM :

Dans les UVPROM ou EPROM ( Erasable Programmable Read Only Memory ), le point mémoire est constitué par un

transistor MOS particulier : le SAMOS ( Stacked gate Avalanche injection Metal Oxyd Semiconductor ). C’est un transistor MOS

à « grille flottante ». Ce transistor à deux mode de fonctionnement :

• en utilisation normale, en polarisant Vgs et Vds positivement, on observe le mode de fonctionnement

classique ;

• par contre, en polarisant très fortement le drain par rapport à la source, l’énergie apportée au niveau du canal

est telle que certains électrons traversent la couche d’isolant, et s’accumulent sur la grille flottante. Après

suppression de cette forte polarisation, les électrons accumulés sur la grille flottante demeurent emprisonnés.

Le premier mode de fonctionnement correspond au fonctionnement normal ou non programmé ; le second mode de

fonctionnement correspondant au mode programmé.

De ce fait, lorsqu’un transistor SAMOS a été préalablement programmé, et qu’on le polarise avec des valeurs de Vgs et

Vds correspondant au mode fonctionnement classique, les charges négatives accumulées sur la grille flottante créent une barrière

de potentiel trop élevée entre la grille et la source pour que le transistor soit passant. Pour le rendre passant, il faudrait appliquer

des valeurs de Vgs plus importantes.

ID

VGS

VT1 VT2

Vc

Grille non

Chargée Grille

Chargée

G

S

ID

V

GS

Si le potentiel de la ligne de sélection est choisi

à une valeur égale à Vc pour le niveau haut :

• Transistor non programmé : transistor

passant ;

• Transistor programmé : transistor bloqué.

Inversement, pour effacer la programmation du transistor SAMOS, on applique un rayonnement ultraviolet, qui, par effet

photoélectrique, apporte l’énergie suffisante aux électrons piégés dans la grille flottante pour se libérer.

La structure d’un point mémoire est donc :

Vcc

Ligne de

sélection

Ligne de bit

Transistor SAMOS

• Transistor non programmé :

Ligne de sélection à l’état bas à ligne de bit à l’état haut ;

Ligne de sélection à l’état haut à ligne de bit à l’état bas ;

• Transistor programmé :

Ligne de sélection à l’état bas à ligne de bit à l’état haut.

Ligne de sélection à l’état haut à ligne de bit à l’état haut.

La programmation de la mémoire EPROM consiste donc à

programmer chaque transistor SAMOS de la matrice pour

lequel la donnée lue doit être au niveau haut.

L’effacement ne peut pas être partiel, et concerne donc la totalité de la mémoire. A cet effet, une fenêtre en quartz,

transparente aux ultraviolets est prévue sur le boîtier. Le temps de programmation est relativement rapide (le programmateur

d’EPROM applique des tensions de 21 ou 12,5 Volts, selon les modèles, pendant une dizaine de ms à chaque transistor à

programmer), alors que le temps d’effacement ( exposition aux UV) est relativement long (10mn à 20 mn selon la puissance de la

source d’UV)

.

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

1

/

14

100%