Cours Circuits Intégrés Analogiques - 2009/2010 Basic

Cours Circuits Intégrés Analogiques

- 2009/2010

Basic

OpAmp Design

26/02/2010

1

Polytech’Montpellier – ERII 4

M2 EEA – Systèmes Microélectroniques

Circuits Intégrés Analogiques

Chapitre III

Amplificateur Opérationnel CMOS élémentaire

Pascal Nouet – Janvier 2010

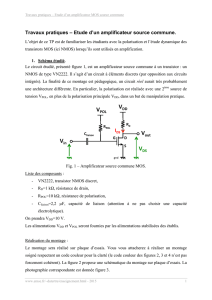

Introduction

• Amplification de tensions différentielles

– Caractéristiques de la tension d’entrée :

• tension et plage de mode commun,

• offset,

– Gain différentiel, gain de mode commun

– Réjection du bruit d’alimentation

• Fonctionnement en boucle fermée

– Système rebouclé : Stabilité, Gain élevé

• Fonctionnement en boucle ouverte (≠OPAMP)

– Gain fini, Gain de mode commun, offset

2

Introduction

Av2 1

Etage

différentiel

d’entrée

2ème étage

de gain Etage de

sortie

AV1

+

-

Ccmp

−

+

−

+

−=

−=

+=

VVv

v

V

V

v

V

V

in

in

mc

in

mc

2

2

in

v

out

v

A

V

⋅

=

V+ V-

Ibias1

Vdd Vdd

Ibias2

Vout

Ibias3

Vdd

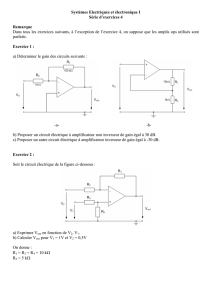

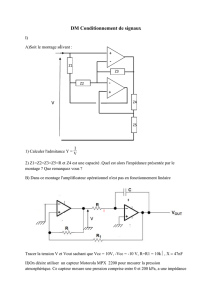

3Plan

• Introduction

• Etage différentiel d’entrée

– Paire différentielle CMOS

– Charge active

– Gain en tension

– Polarisation et mode commun

– Choix de la source de courant

– Dimensionnement

• Amplificateur à deux étages

• Etage de sortie

4

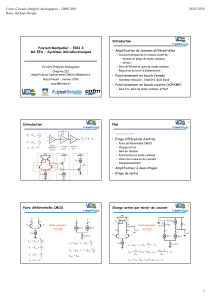

Paire différentielle CMOS

V+ V-

Ibias

T1T2

Id1 Id2

2

21 bias

dd

I

II ==

−

+

−

+

−=

−=

+=

VVv

v

V

V

v

V

V

in

in

mc

in

mc

2

2

Modèle petit-signal

2

1

222

111

2

2

m

m

in

mmd

in

mmd

gg

v

gvgi

v

gvgi

=

⋅−=⋅=

⋅=⋅=

−

+

gm2.v-

gm1.v+

id2

id1

Rout(Ibias)

5Charge active par miroir de courant

V+ V-

Ibias

T1T2

Id1 Id2

Vdd

T3T4

Vout

Id4 Modèle petit-signal

2

3

14

444

3

1

4

2111

2

d

m

dm

gsmd

m

d

gs

d

in

mmd

i

gig

vgi

g

i

v

i

v

gvgi

−≅

⋅

=⋅=⇒=

−=⋅=⋅=

+

rout

(

)

in

out

m

d

d

out

out

v

r

g

i

i

r

v

⋅

⋅

=

−

⋅

=

1

2

4

gm2.v-

gm1.v+

id2

id1

Vout

1/gm3

gm4.vgs4

id4

vgs4

Rout(Ibias)

6

Cours Circuits Intégrés Analogiques

- 2009/2010

Basic

OpAmp Design

26/02/2010

2

Gain en tension : calcul de rout

gm2.v-

gm1.v+

ix2 Vx

1/gm3

gm4.vgs4

Vgs4

rds4

rds1 rds2

ix1ix3

44

3

2

1

4

321

/1

gsm

m

ds

ds

x

ds

x

xxxx

vg

grr

v

r

v

iiii ⋅−

++

+=++=

244343

3

2

4

avec

xgsmxmm

m

x

gs

ivgigg

g

i

v=⋅−=

⇒

=−=

2

4

3

2

1

4

321

/1

2

ds

x

ds

x

m

ds

ds

x

ds

x

xxxx

r

v

r

v

grr

v

r

v

iiii +≅

++

⋅+=++=

4

2

//

ds

ds

out

r

r

r

=

V+ V-

Ibias

T1T2

Id1 Id2

Vdd

T3T4

Vout

Id4

7Gain en tension : influence des

dimensions

V+ V-

Ibias

T1T2

Vdd

T3T4

Vout

VB

VA

4

2

1

1

ds

ds

m

outm

in

out

gg g

rg

v

v+

=⋅=

22,1

2,1

2,1

2

eff

bias

eff

ds

m

V

I

V

I

g=⋅=

2

1

2

2

2bias

ndsn

ds

ds

I

I

r

g

λλ

=≅=

2

1

4

4

4bias

pdsp

ds

ds

I

I

r

g

λλ

=≅=

242

1

)(

2

effpndsds

m

in

out

Vgg

g

v

v

⋅+

=

+

=⇒

λλ

8

2

2

2

2

22

2

)(

2

2L

W

I

Cµ

v

v

W

L

Cµ I

V

dspn

oxn

in

out

oxn

ds

eff

⋅+

=⇒=

λλ

*

Gain en tension : prise en compte du

2nd étage de gain

V+ V-

Ibias

T1T2

Id1 Id2

Vdd

T3T4

Id4

pC

Z

in

e

1

=

Av2 1

4

2

1

ds

ds

out

gg

r+

=

out

in

out

out

eoutout

r

pCrr

ZrZ ≤

+

== 1

//

in

dsds

c

effpn

v

dsds

in

dsds

m

outm

in

out

v

C

gg

f

V

dcA

p

gg C

gg

g

Zg

v

v

A

⋅

+

=⇒

⋅+

=⇒

+

+

⋅

+

=⋅==

πλλ

2)( 2

)(

1

1

42

2

1

42

42

1

11

9Polarisation et Mode commun

• Tous les transistors sont saturés

• Absence de signal

V+ V-

Ibias

T1T2

Vdd

T3T4

Vout

VB

VA

2,1min,

min,2,1

efftnAmc

AefftnmcA

VVVV

V

V

V

V

V

++>⇒

>

−

−

=

min,

2,1

4,3

AA

effAB

tpeffddB

V

V

VV

V

VVV

V

>>− −−=

tntpeffddmc

tnmcBeffAB

VVVVV

V

V

V

V

V

V

+−−<⇒

−

>

⇒

>

−

4,3

2,1

0

=

−

=

⇒

=

=

−+−+

V

V

v

V

V

V

in

mc

10

Choix de la source de courant

• La qualité de l’amplificateur

dépend de la qualité de la source

de courant

– Courant indépendant de Vdd (influence

sur le gain en tension)

– Le courant doit être constant sur

toute la plage de MC

Grande résistance de sortie

– Source de courant saturée pour

une faible tension de sortie

(valeur minimale du Mode Commun)

V+ V-

Ibias1

Vdd

Vout

11

2

2

2

)(

2

L

W

I

Cµ

v

v

dspn

oxn

in

out

⋅+

=

λλ

2,1min, efftnAmc

VVVV ++>

2,1efftnmcA

VVVV −−=

VA

Effet du courant de polarisation sur

le gain

12

V+ V-

Ibias1

Vdd

Vout

)(VV

out

)(VVVv

in −+

−=

↑

1

bias

I

Cours Circuits Intégrés Analogiques

- 2009/2010

Basic

OpAmp Design

26/02/2010

3

0

50

100

150

200

250

300

0,00E+00 2,00E-05 4,00E-05 6,00E-05 8,00E-05 1,00E-04 1,20E-04

Effet du courant de polarisation sur

le gain

13

V+ V-

Ibias1

Vdd

Vout

in

out

v

v

)(

1

AI

bias

Effet de la résistance interne de la

source de courant sur le gain

14

↑

out

R

)(VV

out

)(VVVv

in −+

−=

V+ V-

Ibias1

Vdd

Vout

VA

Rout

Effet de la résistance interne de la

source de courant sur le gain

15

0

50

100

150

200

250

1,00E+03 1,00 E+04 1,00E+0 5 1,00E+06 1,00E+07

in

out

v

v

)(Ω

out

R

V+ V-

Ibias1

Vdd

Vout

VA

Rout

Choix de la source de courant

• Rappel

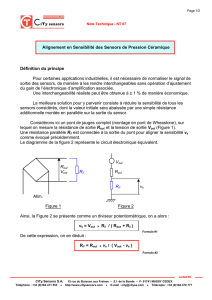

Sensibilité à

Vdd

Résistance de

sortie

Plage de

fonctionnement

Miroir simple ±12% 673kΩ> 0,5V

indépendante de Vdd ±1,5% 533kΩ> 0,35V

indépendante de Vdd +

Cascode

±0,4% 250MΩ> 0,8V

indépendante de Vdd +

Cascode large excursion

±2,9% 16,5MΩ> 0,35V

16

Choix de la source de courant

V+ V-

Ibias

T1T2

Vdd

T3T4

Vout

T8

T7

Ibias

T5

T6

T9

R

Ibias/10

Dimensionnement ?

Gain statique

Courant Ibias

Performances dynamiques

Gain du 2nd étage

17 Dimensionnement

• Exemple avec Ibias7 et Av1(dc)

• Dimensionnement de T3et T4

– Influence sur le niveau haut du mode commun et sur

le gain du second étage compromis avec surface

V+ V-

Ibias

T1T2

Vdd

T3T4

Vout

T7

Ibias7

Vbias

p

n

λ

λ

22,12,1

2,1

2,1

1

.

.2

effoxn

ds

eff

VC

I

L

W

V⋅=⇒⇒

µ

242

1

1

)( 2

)(

effpndsds

m

v

Vgg g

dcA ⋅+

−=

+

−=

λλ

18

24,34,3

4,3

4,3

1

.

.2

effoxp

ds

eff

VC

I

L

W

V⋅=⇒⇒

µ

Cours Circuits Intégrés Analogiques

- 2009/2010

Basic

OpAmp Design

26/02/2010

4

Plan

• Introduction

• Etage différentiel d’entrée

• Amplificateur à deux étages

– Principe

– Dimensionnement

– Gain en basse fréquence

– Calcul du premier pôle

– Simulations

– Analyse de la réponse en fréquence

• Etage de sortie

19 Amplificateur à deux étages :

principe

V+ V-

Ibias

T1T2

Vdd

T3T4

Vout

T8

T7

Ibias

T5

T6

T9

R

Ibias/10

T12

T13

Ibias

Vout

V- V+

20

Amplificateur à deux étages :

principe

Dimensionnement & polarisation statique

Simulation (op, dc) et étude petit signal Gain BF

Simulation (ac) stabilité

2

13

12

12

2

out

ds

ds

m

v

ggg

g

A++

−=

V- V+

Ibias

T1T2

Vdd

T3T4

Vout

T8

T7

Ibias

T5

T6

T9

R

Ibias/10

T12

T13

Ibias

Vout

p

gg C

gg g

A

ds

ds

in

dsds

m

v

4

2

2

42

1

1

1

1

+

+

⋅

+

−=

21 Plan

• Introduction

• Etage différentiel d’entrée

• Amplificateur à deux étages

– Principe

– Dimensionnement

– Gain en basse fréquence

– Calcul du premier pôle

– Simulations

– Pôle dominant et slew-rate

– Analyse de la réponse en fréquence

• Etage de sortie

22

Amplificateur à deux étages :

dimensionnement

• Dimensionnement de T12 et T13

– T13 réglage du courant

de polarisation

identique T7(Slew-Rate)

– T12 Veff et Ids imposés

– gm12 est imposé par le dimensionnement du 1er étage

V- V+

Ibias

T1T2

Vdd

T3T4

Vout

T7

Ibias7

T12

T13

Ibias13

Vout

Vbias

7

7

13

13

L

W

L

W=

( )

( )

7

134

12

4312

2LW LW

I

I

V

V

V

ds

ds

effeffeff

⋅=

=

=

(

)

( ) ( )

4

7

13

12

12

2LW

LW LW

L

W⋅⋅=

23 Plan

• Introduction

• Etage différentiel d’entrée

• Amplificateur à deux étages

– Principe

– Dimensionnement

– Gain en basse fréquence

– Calcul du premier pôle

– Simulations

– Pôle dominant et slew-rate

– Analyse de la réponse en fréquence

• Etage de sortie

24

Cours Circuits Intégrés Analogiques

- 2009/2010

Basic

OpAmp Design

26/02/2010

5

Amplificateur à deux étages : gain

basse fréquence

• Calcul du gain basse fréquence de l’amplificateur

à deux étages

2

2

2bias

oxnm

I

L

W

Cg ⋅⋅=

µ

2

2bias

nds

I

g

λ

≅

2

4bias

pds

I

g

λ

≅

42

2

1

dsds

m

v

gg g

A+

−=

biasoxpm

I

L

W

Cg ⋅⋅=

µ

2

12

biaspds

Ig

λ

≅

12

biasnds

Ig

λ

≅

13

1312

12

2dsds

m

v

gg g

A+

−=

25 Plan

• Introduction

• Etage différentiel d’entrée

• Amplificateur à deux étages

– Principe

– Dimensionnement

– Gain en basse fréquence

– Calcul du premier pôle

– Simulations

– Pôle dominant et slew-rate

– Analyse de la réponse en fréquence

• Etage de sortie

26

Amplificateur à deux étages :

calcul du 1er pôle

prise en compte des capacités…

V- V+

T

1

T

2

Vdd

T

3

T

4

V

out

T

12

V- V+

T

1

T

2

Vdd

T

3

T

4

V

out

V- V+

T

1

T

2

Vdd

T

3

T

4

V

out

T

12

V- V+

T

1

T

2

Vdd

T

3

T

4

V

out

T

12

V- V+

T

1

T

2

Vdd

T

3

T

4

V

out

V- V+

T

1

T

2

Vdd

T

3

T

4

V

out

T

12

12

12

3

2

ings

CC ⋅=

2

4

,

d

d

C

C

1212

%

10

ingd

C

C

⋅

=

121212

LWCC

oxpin

⋅⋅=

27

p1 1

gg g

ggg g

A

4ds2ds

2m

1out4ds2ds

2m

1v

τ+

⋅

+

−=

++

−=

πτ

τ

21

10

1

42

12

2

=⇒

+

≅

c

dsds

in

v

f

gg C

A

Amplificateur à deux étages :

calcul du 1er pôle

• Calcul du pôle lié au premier

étage

– Calcul de la capacité qui charge

le 1er étage prise en compte

de l’effet Miller

p

C

Ag

in

vout

10

12

21

≅⇒

V- V+

I

bias

T

1

T

2

Vdd

T

3

T

4

V

out

T

7

I

bias7

T

12

T

13

I

bias13

V

out

V

bias

V- V+

I

bias

T

1

T

2

Vdd

T

3

T

4

V

out

V- V+

I

bias

T

1

T

2

Vdd

T

3

T

4

V

out

T

7

I

bias7

T

12

T

13

I

bias13

V

out

V

bias

28

Plan

• Introduction

• Etage différentiel d’entrée

• Amplificateur à deux étages

– Principe

– Dimensionnement

– Gain en basse fréquence

– Calcul du premier pôle

– Simulations

– Pôle dominant et slew-rate

– Analyse de la réponse en fréquence

• Etage de sortie

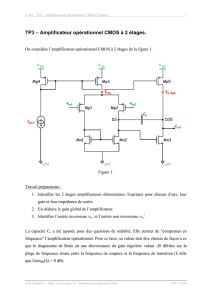

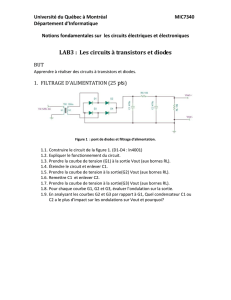

29 Montage étudié

T8

T5

T11

T9

R

Ibias/10

T6

T10

V- V+

T1T2

Vdd

T3T4

T7

Ibias7

T12

T13

Ibias13

Vout

Vref

Cf

T16

Vout1

4ds2ds

1m

1v

gg g

A+

−≅

13

12

12

2

ds

ds

m

v

gg

g

A+

−≅

30

6

6

7

7

8

8

9

9

10

10

11

11

12

12

1

/

12

100%