Page 1 sur 5 Technologie de fabrication des circuits intégrés 05/04

Recherche sur le site

Go

Circuits et composants Guide d'achat Emplois Resources externe Forum de discussion Annonces Divers

Connexion | Datasheet |

Equiv.

Nouv. | Cat. | Boitiers |

Broches

Audio-Vidéo |

Téléphonie

Informatique

Offres |

Ajout

CVs | Ajout

Cours | Montages |

Logiciels

Sociétés | Livres | Ajout

lien

Electronique |

Informatique

Dépannage | Hors Elec.

Liste

annonces

Ajouter

annonce

Actualités | Barre d'outils

Connecteurs | Contact

Annonces Goooooogle

Rigid Flex & Flex

Circuit

Flex Design,

Fabrication &

Assembly Thinking

Flex, Think Lenthor

www.lenthor.com

t digchip

Home » Diverses rubriques » Technologie de fabrication des circuits intégrés

CMOS

bipolaire BiCMOS

SOI Liste de quelques fondeurs

I - Technologie CMOS

La technologie CMOS est une technologie planaire destinée au développement des systèmes à très haute échelle d’inté

gration (VLSI).

Grâce aux propriétés des transistors MOS complémentaires (noté

es CMOS pour Complementary Metal Oxyde Silicon), cette

technologie permet de réaliser des circuits à faible coût et à basse consommation. Cet avantage lui a permis d’ê

tre reconnue comme la

technologie de pointe la plus avancée et la plus maîtrisée dans le domaine de la micro-électronique.

Parmi les types de technologies CMOS, on peut citer les trois qui sont les plus connues: la technologie CMOS à

caisson n, la

technologie CMOS à caisson p, et la technologie CMOS à double caisson. Une technologie CMOS à

caisson n utilise un substrat en

silicium de type p dans lequel est formé un caisson en silicium de type n. Des transistors pMOS sont alors réalisé

s dans ce caisson et

des transistors nMOS dans le substrat. Une technologie CMOS à caisson p, permet de ré

aliser des transistors pMOS sur le substrat de

type n et des transistors nMOS dans un caisson p. Enfin, la technologie CMOS à

double caisson utilise un substrat en silicium de type

quelconque, sur lequel sont déposés des caissons de type n et des caissons de type p.

Les transistors nMOS et pMOS qui peuvent être réalisés par ces technologies sont utilisé

s pour former des fonctions analogiques ou

numériques ; une coupe de ces transistors est donnée sur la fig. (1). Les procédés de fabrication utilisé

s dans chaque technologie

CMOS pour réaliser ces transistors diffèrent d’un fabriquant à un autre et évoluent continuellement pour ré

aliser des composants plus

performants et plus rapides.

Cependant il nous parait intéressant de connaître au moins les étapes de fabrication communes à ces technologies pour avoir une idé

e

sur les différentes structures de composant semi-conducteur qu’elles peuvent réaliser.

fig.(1). Vue en coupe des transistors CMOS de type n et de type p réalisés par trois différents procédé

s de fabrication CMOS. La vue

en coupe (a) montre les deux types de transistors dans une technologie CMOS à

caisson n, (b) montre ces transistors dans une

technologie CMOS à caisson p et (c) dans une technologie CMOS à double caisson.

Dans le paragraphe suivant, nous allons présenter les grandes lignes des procédés de fabrication utilisés par les technologies CMOS

à

caisson n, ce qui permet d’en déduire par analogie les procédés communs utilisés dans les technologies CMOS à caisson p et

à

double caisson.

Procédé de fabrication CMOS à caisson n

L’approche la plus couramment utilisée dans une technologie CMOS à caisson n est d’

utiliser un substrat en silicium de type p

modérément dopé, de créer le caisson n pour les composants à canal p et de former les transistors à

canal n dans le substrat natif. Le

procédé de fabrication utilisé par cette technologie est généralement complexe et dé

pend du fondeur, nous allons donc restreindre

notre étude aux étapes essentielles.

La figure (2) illustre le procédé de fabrication en technologie CMOS à caisson n et donne à chaque étape du procédé

une vue en

coupe de la tranche du silicium en fabrication et le masque correspondant.

Généralement dans une technologie de circuits intégrés, on commence par une tranche de silicium (Wafer) sur laquelle on a déj

à

déposé une couche épaisse d’oxyde. La première étape consiste à définir la région où le caisson n sera formé, dans cette ré

gion la

couche d’oxyde épais est gravée pour permettre une diffusion profonde d’impureté

de type n telle que le phosphore. La profondeur du

caisson ainsi que son niveau de dopage va dépendre de l’énergie et de la durée de la diffusion. Le caisson ainsi formé va servir

à

réaliser des transistors à canal p.

Page

1

sur

5

Technologie de fabrication des circuits int

é

gr

é

s

05/04/2007

http://www.abcelectronique.com/divers/dossiers/techno_ci/index.phtml

La seconde étape consiste à définir les régions où seront formées les couches fines d’oxyde qui sont nécessaires pour ré

aliser les

grilles des transistors. La couche épaisse d’oxyde est alors gravée jusqu’au substrat dans les régions où des transistors à

canal n

seront réalisés, et jusqu’au caisson dans les régions où des transistors de type p seront formés. Les couches fines sont alors cré

es par

oxydation du silicium.

Dans l’étape suivante la grille en polysilicium est formée. Cette étape consiste à recouvrir le matériau de polysilicium puis à

faire une

gravure pour enlever l’essentiel de cette couche de façon à ne laisser que les régions qui vont servir comme grille pour les transistors.

Dans les deux étapes qui suivent les transistors de type n et les transistors de type p sont définis. Une diffusion localisée d’impureté

s

de type donneur telle le phosphore, va former le drain et la source des transistors à canal n, ces régions sont appelées ré

gions de

diffusion n+. Une diffusion localisée d’impuretés de type accepteur telle que le Bore va former les ré

gions de drain et source des

transistors à canal p, ces régions sont appelées région de diffusion p+. Ces deux étapes sont faites aprè

s la formation de la grille de

polysilicium pour assurer un auto-alignement des deux régions de diffusion d’un transistor.

fig(2). La figure montre les différentes étapes suivies pendant un procédé de fabrication d’une technologie CMOS à

caisson n. Elle

donne une vue en coupe de la tranche de silicium en fabrication ainsi que le masque correspondant à chaque étape du procéd

é

CMOS à caisson n.

Comme le montre la figure (2), les étapes précédentes ont permis de réaliser des transistors à

canal p dans le caisson et des

transistors de type n dans le substrat. L’étape qui suit consiste à définir les lieux où un contact sera réalisé. La couche d’

oxyde est

alors gravée jusqu’aux surfaces sur lesquelles sera pris un contact métallique. Cette étape est suivie par une mé

tallisation pour former

ces contacts métalliques ainsi que les pistes d’interconnexions. Le nombre de niveaux de métal diffère d’une technologie à

une autre,

plus il y a de niveaux de métal, plus le concepteur a de facilités pour ré

aliser les connections entre les composants dans le circuit

intégré.

L’étape finale consiste à recouvrir le circuit d’une couche de passivation ( une couche d'oxyde) et à ré

aliser des ouvertures pour les

différents plots du circuit intégré. La couche de passivation est nécessaire puisqu’elle permet de protéger le silicium d’

une

contamination par des impuretés qui peuvent affecter les composants.

Par analogie avec les étapes du procédé de fabrication de la technologie CMOS à caisson n on peut déduire les étapes des procédés

CMOS à caisson p ou à double caisson.

Cliquer ici pour voir une animation sur la technologie CMOS (format flash)

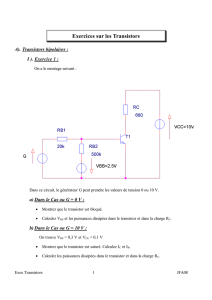

II - Technologie bipolaire

La technologie bipolaire est une technologie planaire qui permet de réaliser des systèmes à très haute échelle d’intégration à

partir de

transistors bipolaires. Un circuit dans cette technologie peut incorporer des transistors npn, des transistors pnp, des diodes, des

résistances et des éléments capacitifs. Les propriétés des transistors bipolaires font que les circuits électroniques réalisé

s dans cette

technologie sont plus rapides comparés aux même circuits réalisés dans une technologie CMOS. Cependant l’inconvé

nient majeur

qu’ils présentent est leur forte consommation.

Une vue en coupe des éléments réalisés dans cette technologie est présentée sur la figure (3) où on peut observer des ré

sistances

formées par des régions de diffusion dans la couche épitaxiale de type n. Une diffusion réalisée dans une région

permet de former des diodes à jonctions. Un transistor npn vertical est réalisé par une succession de diffusions et

dans la

couche épitaxiale. Cette dernière couche sert de collecteur pour le transistor, la diffusion sert de base et la diffusion

d’émetteur. Le transistor pnp latéral est formé par deux régions de diffusion , qui servent d’é

metteur et de collecteur, dans la

couche épitaxiale de type n qui sert de base pour le transistor. Les éléments capacitifs ne sont pas présentés dans cette figure.

Page

2

sur

5

Technologie de fabrication des circuits int

é

gr

é

s

05/04/2007

http://www.abcelectronique.com/divers/dossiers/techno_ci/index.phtml

Fig.(3). Vue en coupe des composants réalisés dans une technologie bipolaire. Le procédé

de fabrication dans cette technologie

permet de faire un empilement de 4 couches de silicium de type différents (pnpn).

Dans ce paragraphe, nous allons décrire les étapes essentielles suivies pendant un procédé

de fabrication dans la technologie

bipolaire.

Procédés de fabrication dans une technologie bipolaire

Le point de départ dans un procédé de fabrication bipolaire est généralement un substrat de type p modérément dopé.

La surface de

ce substrat est ensuite polie et traitée pour enlever les impuretés et les couches d’oxyde.

Une couche mono-cristalline de silicium de type n est ensuite formée par é

pitaxie sur tout le substrat. Cette couche va servir de

collecteur pour les transistors verticaux de type npn ou de base pour les transistors latéraux de type pnp.

Une épaisse couche d’oxyde est alors formée sur toute la surface de silicium. Cette couche dont l’épaisseur est typiquement de l’

ordre

de 5000 Å, permet de réaliser des masques pour définir les régions où seront formés des diffusions d’impuretés donneur ou accepteur.

L’étape suivante consiste à former les îlots d’isolation par diffusion d’impureté donneur . Cette diffusion est réalisé

e dans les

régions définies par la gravure faite dans l’épaisse couche d’oxyde. Ces îlots permettent de séparer é

lectriquement les transistors

adjacents.

fig.(4). Etapes technologiques dans un procédé de fabrication bipolaire. La première étape consiste à déposer par é

pitaxie une couche

de silicium de type n. Une première diffusion d’impureté donneur permet de réaliser des îlots d’isolation. Une deuxiè

me diffusion, moins

profonde, de donneurs permet de réaliser la base du transistor npn vertical. Une diffusion d’impureté accepteur définit la ré

gion

d’émetteur du transistor. Les dernières étapes consistent à réaliser les contacts ohmiques, les pistes métalliques pour l’

interconnexion

et à déposer une couche de passivation.

L’étape suivante consiste à réaliser une gravure dans la couche épaisse d’oxyde pour définir les régions où seront formé

s les

collecteurs ainsi que les émetteurs des transistors pnp latéraux, les ré

gions de base des transistors npn verticaux ainsi que les

résistances. Une seconde diffusion d’impureté donneur permet de réaliser des zones de diffusion dans ces régions.

Les régions d’émetteur des transistors npn verticaux ainsi que les contacts ohmiques dans le caisson n sont alors réalisé

s par une

diffusion d’impureté donneur (diffusion ).

Page

3

sur

5

Technologie de fabrication des circuits int

é

gr

é

s

05/04/2007

http://www.abcelectronique.com/divers/dossiers/techno_ci/index.phtml

Un dépôt de métal permet ensuite de former les contacts sur les différents composants ainsi que les pistes mé

talliques pour

l’interconnexion. Enfin une couche de passivation est formée sur la surface du silicium, elle permet de protéger les composants d’

une

éventuelle contamination.

III Technologie BiCMOS

La technologie BiCMOS est apparue vers les années 1990. Comme elle utilise à la fois le procédé de fabrication d’

une technologie

bipolaire et le procédé d’une technologie CMOS, elle permet de réaliser sur le mê

me circuit des transistors CMOS et des transistors

bipolaires. Ainsi elle rassemble les avantages des ces deux technologies. En particulier, elle permet de réaliser des circuits rapides et

à

faible consommation.

Une vue en coupe des composants réalisés dans cette technologie est donné

e sur la figure (5). Les transistors CMOS de type n sont

réalisés dans les caissons p et des transistors CMOS de type p dans les caissons n.

Fig.(5). Vue en coupe de composants réalisés dans un procédé de fabrication BiCMOS. (cette technologie permet de ré

aliser des

transistors npn verticaux à émetteur en polysilicium. La structure du transistor peut être utilisée pour réaliser des dé

tecteurs de couleur

à trois jonctions enterrées.)

Comme le montre la figure (5), le transistor npn vertical réalisé dans cette technologie a une structure diffé

rente de celle du transistor

npn vertical réalisé dans une technologie bipolaire. En effet l’émetteur de ce transistor est formé

principalement par une couche de

polysilicium (d’où son nom transistor bipolaire à émetteur en polysilicium).

Pendant le procédé de fabrication dans une technologie BiCMOS, la région de base du transistor est formé

e par une diffusion

dans le caisson n. Un îlot de diffusion est alors réalisé

dans le caisson n et sert comme contact ohmique profond. Le caisson

n et cet îlot de diffusion forment la région du collecteur du transistor.

L’émetteur est réalisé en deux étapes : la première étape consiste à déposer le deuxième niveau de polysilicium (poly2) sur la ré

gion

de diffusion (région de la base du transistor) ; la seconde étape consiste à effectuer une diffusion d’impureté

donneur sur cette

couche de polysilicium pour augmenter sa conductivité. La durée de la diffusion de donneurs est fixée de telle sorte que ces impureté

s

traversent la couche de polysilicium et forment une région de diffusion au dessous de cette couche. Cette région de diffusion

forme avec la couche de polysilicium l’émetteur du transistor.

Sachant que le procédé de fabrication dans la technologie BiCMOS combine les deux procédé CMOS et bipolaire, nous n’

allons pas

présenter les étapes de son procédé de fabrication.

Cliquer ici pour voir une animation sur la technologie BiCMOS (format flash)

IV Technologie SOI

Technologie CMOS silicium sur insulaire (SOI) : cette technologie a plusieurs avantages potentiel sur les autres technologies

traditionnelle décrite précédemment, notamment au niveau de la haute densité, pas de problème de ‘latch-up’ et plus faible capacit

é

parasite. Dans le processus SOI, une couche mince d’un film de silicium cristallin est épitaxié

sur un isolateur tel que le saphir ou le

spinelle d'aluminium de magnésium. Plusieurs masques et techniques de dopage sont ensuite utilisé

pour former les canaux n et p.

Les étapes de fabrication typiques sont les suivantes : - on fait croître une couche mince de silicium faiblement dopé n au dessus d’

un

isolant comme le saphir par exemple (fig 6a). - On grave les zone de silicium sauf là où les régions de diffusion seront utilisé (

fig. 6bc).

La gravure doit être ‘anisotropic’ puisque l’épaisseur de silicium est plus grande que la distance désiré

e entre deux ceux couche de

silicium. - ensuite une couche p est formée en masquant la couche n par une couche photoré

sistante. Un dopant p, Bore par exemple,

est implanté(fig. 6d). L’îlot p deviendra ensuite un canal n. - L’îlot p est ensuite recouvert avec un couche photoré

sistante tandis que la

région n est dopé, phosphore par exemple, pour donné un îlot n (fig. 6e). Cet îlot deviendra ensuite un canal n. - On fait croî

tre un une

couche mince d’oxyde au dessus de toutes les structures, ceci est effectué normalement par oxydation thermique. -

Un film

polysilicium est déposé au dessus de la couche d’oxyde. - On dope avec du phosphore cette couche de polysilicium pour diminué

la

résistivité (fig. 6f). Le polysilicium est dessiné en photomasquant et en gravant. Ceci dé

finit la couche polysilicium dans la structure (fig.

6g).- L’étape suivante consiste a former la source et le drain du canal n dans l’îlot p. L’îlot n est couvert par une couche photoré

sistante

et le dopant n est ainsi implanté (fig. 6h). le dopant sera bloqué par la couche photorésistante au niveau de l’îlot n et il sera bloqué

au

niveau de la grille de l’îlot p par le polysilicium. Ainsi cette étape définira le dispositif à canal n. - Le dispositif à

canal p est ensuite

formé en masquant l’îlot p et en implantant le dopant type p. Le polysilicium au dessus de la grille de l’î

lot n bloquera le dopant de la

grille, ainsi le dispositif a canal p est formé (fig. 6i). - Une couche de verre phosphoreux ou un autre type d’

isolant tel que le dioxyde de

silicium est ensuite déposé au-dessus de la structure entière. Cette couche de verre est gravé

e au niveau des contacts. La couche de

métal est formée ensuite par évaporation d’aluminium sur toute la surface et elle est gravée pour garder uniquement les zones où

le

métal est désiré. L’aluminium va coulé à travers les zones de contacts pour établir la liaison avec les diffusion et les ré

gions de

polysilicium (fig. 6j). - Une couche de passivation finale est déposé et gravé au nivaux des ‘bonding’.

La technologie SOI admet des avantages vis à vis des autres technologies qui sont : Absence de caissons ce qui permet d’

avoir des

structures plus denses. Des capacités parasites plus petites ce qui fournit une plus grande rapidité des circuits. Pas de problè

mes

d’inversion du à un substrat isolant. Pas de problème de ‘latch-up’ dû à l’

isolation des transistors n et p par un substrat isolant. Comme

le substrat est isolant, on n’a plus de problème d’effet substrat. Toutefois, vu l’absence de diode substrat, les entré

es sont plus difficile

a protéger. L’autre inconvénient majeur réside dans le coût de fabrication qui est beaucoup plus élevé

que les autres technologies,

notamment au niveaux du substrat employé ici est beaucoup plus chère qu’un substrat silicium.

Page

4

sur

5

Technologie de fabrication des circuits int

é

gr

é

s

05/04/2007

http://www.abcelectronique.com/divers/dossiers/techno_ci/index.phtml

Fig 6 : Procédé de fabrication de la technologie SOI

On vient de décrire les principaux processus de la technologie CMOS. Au cours des années, des améliorations ont été apportées à

ces

technologies. On peut cité par exemple l’emploi de plusieurs niveaux de mé

tallisation ou de policilicium, la diminution de la longueur de

la grille. Ceci dans le but d’augmenter les performances des circuits dans le domaine du numérique ( accroî

tre le nombre de transistors

sur une surface) et de l’analogique ( capacité de haute qualité, des résistances à caractéristiques variable)

© 2000 - 2006 Tous droits réservés.

Page

5

sur

5

Technologie de fabrication des circuits int

é

gr

é

s

05/04/2007

http://www.abcelectronique.com/divers/dossiers/techno_ci/index.phtml

1

/

5

100%