Transistors et architecture de Von Neumann - e-campus

Introduction aux architectures matérielles

Transistors et architecture de Von Neumann

Sylvain Chevallier

IUT de Vélizy

Université de Versailles Saint-Quentin

26 janvier 2015

Transistors

Portes logiques

Architecture de von Neumann

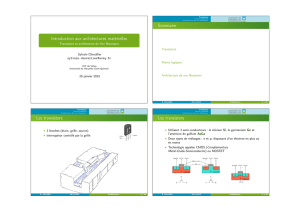

Les transistors

•Utilisent 3 semi-conducteurs : le silicium Si, le germanium Ge et

l’arséniure de gallium AsGa

•Deux types de mélanges : net p, disposant d’un électron en plus ou

en moins

•Technologie appelée CMOS (Complementary

Metal-Oxide-Semiconductor) ou MOSFET

S. Chevallier 26/1/2015 Architecture 4 / 35

Transistors

Portes logiques

Architecture de von Neumann

Loi d’Ohm

•Le courant va d’un point de potentiel élevé vers un point de

potentiel faible

•Analogie directe entre le potentiel et la pression, le courant et le

débit

•Pour un tuyau donné, le débit est proportionnel à la différence de

pression entre ses extrémités

•débit =différence de pression

diamètre

débit exprimé en Ampères (A)

différence de potentiel en Volts (V)

impédance ou résistance en Ohms (Ω)

S. Chevallier 26/1/2015 Architecture 5 / 35

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

1

/

34

100%