DSP - Lirmm

publicité

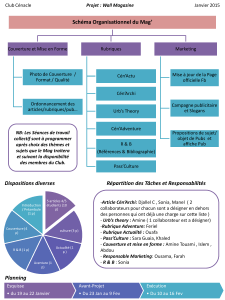

Processeurs de Traitement Numérique du Signal (DSP) Processeurs de Traitement Numérique du Signal (DSP) I. II. III. IV. Olivier Sentieys IRISA Université de Rennes I ENSSAT Lannion [email protected] http://www.irisa.fr/R2D2 Introduction Architectures MAC/Harvard Evolutions des DSP Flot de développement Merci à Daniel Ménard pour son support Exemples d’applications I. Introduction 1. 2. 3. 4. Contexte applicatif Caractéristiques algorithmiques Solutions architecturales Marché des DSP Téléphonie cellulaire Communications sans-fil Contrôle de moteur Modems Photo et caméra numériques Voix sur IP, réseau Audio grand public Navigation Vidéoconférence Jouets, consoles vidéo Synthèse musicale, effets ARCHI’07 - 4 • Performances • Faible coût • Faible énergie Communications satellite Analyse sismique Sécurité Médical Reconnaissance vocale Sonar, radar Débruitage, écho Anticollision … et pleins d’autres à venir Tâches élémentaires Algorithmes de TdSI1 Compression de signal (parole, audio, vidéo) Filtrage Modulation et démodulation Détection et correction d’erreurs Contrôle Traitements audio (e.g. réduction bruit, égalisation, annulation d’écho, conversion de fréquence) Reconnaissance vocale Synthèse de signaux ARCHI’07 - 5 1Traitement du signal et de l’image Signaux numériques o Temps et amplitude discrets o Flot de données o Scalaires, vectorielles, matricielles, … Traitement temps réel o Temps d'exécution Tex guidé par flots de données o Période d'échantillonnage Te période des sorties Tf > Tex e(t) Te s(t) ARCHI’07 - 6 Algorithme ex. s(n) = max(moy(e), s(n-1)) Tf Diversités Fonctions typiques de TdSI Complexité des algorithmes de TdSI Convolution, filtrage (RIF, RII), corrélation, DCT < 5 MOPS 10-30 MOPS Faible mesure/contrôle > 100-1000 MOPS Elevé Compression Compression ADSL UMTS parole modemsaudio GSM Compression Imagerie vidéo médicale Format des données Application Taille des données PWM, mesures, contrôle 1 à 4 - 18 à 22 bits o y = y + x.h : MAC (multiplication-accumulation) Adaptation (LMS) o yn = yn-1 + x.h : MAD (multiplication-addition) FFT, multiplication complexe o xr=xr.wr-xi.wi; xi=xr.wi+xi.wr Viterbi o a1 = x1 + x2; a2 = y1 + y2; o y = (a1>a2) ? a1 : a2 : ACS (addition-comparaison-sélection) convertisseurs sigma -delta ARCHI’07 - 7 radio HF/VHF, radar 6 - 14 bits sonar 10 - 12 bits parole 8 - 14 bits audio 16 - 20 bits imagerie / vidéo 8 - 36 bits (par pixel) analyseurs de s ang 16 - 18 bits Estimation de mouvement o sad += |xi,j - yi+u,j+v| : SAD (sum-of-absolute-difference) ARCHI’07 - 8 Exemple Fil Rouge Fonctions typiques de TdSI Filtre Numérique RIF sur N points Filtre Numérique RIF symétrique sur N points D D D D x(n) h(0) x h(1) x h(2) x h(3) x h(4) + + + + + x y(n) 0 + + h(0) + x h(1) h(2) x y(n) TAP ARCHI’07 - 9 x + ARCHI’07 - 10 + Fonctions typiques de TdSI Fonctions typiques de TdSI FFT Fast Fourier Transform Filtrage adaptatif LMS • Butterfly (DIF) X X’ = X + W.Y Y x x x x ARCHI’07 - 11 Y’ = X - W.Y W + + - DLMS xn(i-1) + - x en ARCHI’07 - 12 + hn(i) hn-1(i) xn(i) x + y y Fonctions typiques de TdSI Caractéristiques algorithmiques Estimation de mouvement Charge de calcul importante o Nids de boucles o Multiplications-accumulations (convolution) o Multiplications-additions (FFT, DCT, adaptation, distances, ...) • Codage vidéo MPEGx, H26x N+2p Matched Block Motion Vector NxN (u,v) p Reference Block NxN Search Window ARCHI’07 - 13 sadmin = MAXINT; mvx=0; mvy=0; for (u=-p; u<=p; u++) for (v=-p; v<=p; v++) { sad = 0; for (i=0; i<N; i++) { for (j=0; j<N; j++) { sad = sad + ABS[BR(i,j)-FR(i+u,j+v)] /* if (sad>=sadmin) break; */ } } if (sad<sadmin) { sadmin = sad; mvx = u; mvy = v; } } Précision des calculs o Virgule fixe ou flottante o Compromis coût – précision des calculs Bande passante mémoire Calculs d'adressage complexes o Gestion signal, accès image, bit-reverse (FFT), ... Boucles de traitement courtes o Les instructions peuvent être placées en interne o Pas besoin de grande taille de cache (données ou instructions) ARCHI’07 - 14 Solutions architecturales Marché des DSP (1) Efficacité énergétique Sans fils domine : 75% des revenus en 2004 Systèmes grand public : DVD, TV et radio numérique, ... Contrôle de moteurs, ... Flexibilité Pleiades, DART 10-50 MOPS/mW Embedded Processor 100 -1000 MOPS/mW Multipurpose 6% Automotive 3% ASIP/DSP Embedded FPGA 100 PowerPC 1 MIPS/mW Cellular phone 62% Reconfigurable Processor EE : MOPS / mW 10 1 Consumer 9% Wireline (modem, xDSL) 6% SA110 0.4 MIPS/mW ASIC ARCHI’07 - 15 Flexibility • Spécialisation, parallélisme 2 V DSP 3 MOPS/mW Wireless (other) 2% ARCHI’07 - 16 Computer 6% Cellular infrastructure 5% Wirless short range 1% Marché des DSP (2) Marché des DSP (3) En haut de la liste des plus fortes croissances du marché de l’industrie des semi-conducteurs Place dans le marché des processeurs embarqués 14000 DSP Market (M$) 12000 10000 8000 6000 4000 2000 0 1992 1993 1994 1995 1996 1997 1998 1999 2000 2001 2002 2003 2004 2005 2006 2007 Prévisions Forward Concept Co. ARCHI’07 - 17 ARCHI’07 - 18 II. Architecture MAC/Harvard Architecture Von Neumann E.g. processeurs RISC MEMORY DATA BUS PC MEM. DATA REGISTER REGISTER FILE ADDRESS REGISTER MUX ALU 1. Genèse des DSP : MAC/Harvard 2. Modélisation des générations 1 et 2 Panorama des DSP 3. Performances Code example: multiply & accumulate r2 = r2 + #imm * r1 mov #imm,r3 mul r1,r3 add r3,r2 3 instructions, plus de 3 cycles d'horloge MEMORY ADDRESS BUS ARCHI’07 - 20 FIR sur machine Von Neumann Problèmes • Bande passante avec la mémoire • Code pour le contrôle et la gestion de l'adressage • Multiplication lente loop: mov mov mpy add mov inc inc inc dec tst jnz *r0,x0 *r1,x1 x0,y0,a a,b y0,*r2 r0 r1 r2 ctr ctr loop Data Path Généralités sur les DSPs Propriétés du traitement numérique du signal Calculs intensifs et répétitifs Primitives simples Memory Le tout dans un environnement temps réel Exécution en N.(15 à 20) cycles ARCHI’07 - 21 ARCHI’07 - 22 Architecture Harvard (1) Unité de traitement PROGRAM ADDRESS BUS DATA ADDRESS BUS PROGRAM RAM/ROM DATA RAM-A DATA BUS - A DATA BUS - B 24 24 X0 X1 Y0 Y1 Operand Registers DATA RAM-B 24 24 Multiplier DATA BUS - A 56 DATA BUS - B 56 ALU Shifter 56 (-1, 0, +1) PROGRAM DATA BUS Accumulators PROGRAM CONTROL AGU-A AGU-B Address Generation MULTIPLIER ALU REGISTERS ACCUMULATORS 24 A (56) B (56) 56 ARCHI’07 - 23 Conséquences sur les architectures Fonctionnement pipeline Architecture Harvard Structures de contrôle évoluées Unités de traitement spécialisées câblées Gestion d’adressage complexes 24 56 Shifter/Limiter Motorola DSP 5600x Processing Unit ARCHI’07 - 24 (-1, 0, +1) 24 24 Architecture Harvard (2) FIR sur DSP conventionnel Bus et mémoires données/instructions séparées Unité de traitement de type mpy-acc Registres distribués ( RISC register file) Instructions complexes s’exécutant en 1 cycle • Chaque module (ALU) possède ses propres registres locaux Génération adresses efficaces (AGUs) • Modes d’adressage spéciaux : auto incr-decr, circular buffering (delay line) ... in@2 in@1 in ARCHI’07 - 25 T=DM(*r1+); P=T*PM(*r0+) || T=DM(*r1+); loop: acc=acc+P || P=T*PM(*r0+) || T=DM(*r1+) jnz loop; acc=acc+P || P=T*PM(*r0+); acc=acc+P T Program Memory MULT Data Path P Data Memory ALU ACC Exécution en N+ cycles ARCHI’07 - 26 II. Architecture MAC/Harvard Processeur : modélisation Unité de contrôle (IP : Instruction Processor) • Unité fonctionnelle (UF) qui interprète les instructions et les passe à l’unité de traitement (DP) 1. Genèse des DSP : MAC/Harvard 2. Modélisation des générations 1 et 2 Panorama des DSP 3. Performances Unité de traitement (DP : Data Processor) • UF qui modifie ou transforme les données Unité de mémorisation • IM : Instruction Memory : stocke les instructions • DM : Data Memory : stocke les données traitées par le DP Unité de communication (EIU : External Interface Unit) • Contrôle les accès aux données ou instructions externes, ou à d'autres processeurs ARCHI’07 - 28 [Flynn72] [Skillicorn88] Architecture Harvard de base Processeur : modélisation IP : Instruction Processor, DP : Data Processor IM : Instruction Memory, DM : Data Memory IP DP IP DP DM IM IM IM Address from PC Request Instruc Receive Intstruc. Receive State from DP Determine Oper. Add. Decode Send to DP DP DP DP IP IP DM Receive Instruc. Receive Oper. Address Request Operand DM e.g. TMS320C10 ARCHI’07 - 29 Return State Classification de E. Lee [Lee89] Architecture Harvard de base TMS320C10 (1982) • 2N+4 cycles • 2N+4 instructions! ARCHI’07 - 30 IP Store Results Receive Operand Exec. Instruction DM Optimisations des performances Comment améliorer l’architecture Harvard ? Transformations du diagramme d'états • réarrangement des états • exécution en parallèle d'états (e.g. Store Results et Return State) Pipeline de l'exécution des états • mise en parallèle d'états appartenant à des instructions successives Augmentation du nombre de FUs et/ou de DMs • plusieurs DPs peuvent exécuter des instructions en parallèle sur des données indépendantes • FUs spécialisées pour la génération d’adresses ARCHI’07 - 31 [Verbauwhede00] ARCHI’07 - 32 Interconnexions entre FUs Modification 1 Les interconnexions suivantes sont valables pour toutes les FUs précédentes (DP, IP, IM, DM). Autorisation de mémorisation de données dans l'IM En un cycle : fetch deux opérandes de la mémoire, exécute MAC, écriture du résultat en I/O ou mémoire • 1 - vers - 1 o une FU est connectée à une autre FU • n - vers - n o une FUi d'un ensemble de FUs est connectée à une autre FUi • 1 - vers - n o une FU est connectée à n autres FUs d'un ensemble de FUs • n - par - n DP IP 1-vers-2 DM IM/DM o toute FUi d'un ensemble est connectée à chaque autre FUj e.g. AT&T DSP32 et DSP32C ARCHI’07 - 33 ARCHI’07 - 34 Modification 2 Modification 3 DM est une mémoire multi-ports, plusieurs accès aux données par cycle Utilisable pour des mémoires internes Cache pour charger les instructions fréquentes Évite les conflits d'accès données et instructions de la modification 1 DP DM IP IM e.g. Fujitsu MB86232 (3 ports en mémoire interne) TMS320C25 : cache 1 instruction (boucles) DSP16 : cache 15 instructions ADSP-2100 : cache 16 instructions ARCHI’07 - 35 ARCHI’07 - 36 DP IP 1-vers-2 cache DM IM/DM FIR sur DSP conventionnel Deuxième génération (Modification 4) TMS320C2x (1986) Deux mémoires données DM séparées En un cycle : fetch deux opérandes et une instruction si le cycle mémoire est le même que le cycle d'instruction de base ZAC || LTD; LTD || MPY; RPTK N-1 MACD APAC || MPY; APAC; ARCHI’07 - 37 1-vers-2 DM 1 DM 2 IM ARCHI’07 - 38 CORE PROCESSOR DUAL-PORTED SRAM TIMER INSTRUCTION CACHE TWO INDEPENDENT DUAL PORT BLOCKS PROCESSOR PORT ADDR DATA ADDR DAG 1 DAG 2 8x4x32 8x4x24 DATA BLOCK 0 SHARC BLOCK 1 Architecture Analog Devices TEST & EMULATION PROGRAM SEQUENCER PM ADDRESS BUS EXTERNA L PORT ADDR BUS MUX 32 DM ADDRESS BUS 48 BUS CONNECT (PX) 48 DATA BUS MUX DM DATA BUS HOST PORT IOP REGISTERS (MEMORY MAPPED) BARREL SHIFTER ALU I/O PROCESSOR 32 MULTIPROCESSOR INTERFACE PM DATA BUS 40/32 DATA REGISTER FILE Modification 5 JTAG DATA ADDR ADDR DATA 24 ARCHI’07 - 39 IP Motorola DSP 56001 et 96002 TMS320C30, C40, C50 ADSP-2100 Exécution en N cycles MULTIPLIER DP CONTROL, STATUS & DATA BUFFERS DMA CONTROLLER Bancs mémoire multiples Instruction multiopérandes en parallèle avec accès I/O Problème de partition des données sur un grand nombre de bancs (FFT) LINK PORTS (6) IP 2-vers-2 1-vers-4 DM DM DM DM IM EIU IOM 1-vers-4 4 6 SERIAL PORTS (2) DP 6 Hitachi DSPi (6 bancs mémoire) 36 ARCHI’07 - 41 Générations Caractéristiques complémentaires Performances normalisées (BDTImark) 10000 4ème génération 1000 StareCore(300MHz) TMS320C62x (300MIPS) Carmel (300 MHz) DSP16210 (100 MIPS) 100 DSP56301 TMS320C54x (50-100MIPS) ADSP2183 (50MIPS) 2ème génération DSP56001 (13MIPS) ADSP21xx (13MIPS) TMS320C50 10 1ère Localisation des données • Modèle registre-mémoire, Load-Store Codage des instructions complexes • Stationnarité temporelle ou par les données Format des instructions • Type d’encodage, compromis consommation/efficacité Structures de contrôle 3ème génération • Boucles matérielles, branchement génération Modes d’adressage TMS320C20 (5 MIPS) TMS320C10 (2.5 MIPS) 1 1980 1982 1984 1986 1988 1990 ARCHI’07 - 42 1992 1994 1996 1998 2000 2002 Année Résumé (1) Calcul Précision Bande passante mémoire ARCHI’07 - 44 ARCHI’07 - 43 [cf. Annexes] Résumé (2) FUs spécialisées pour les fonctions classiques de TdSI en parallèle, MAC simple cycles Bits de garde, saturation, arrondis, multiplication 16-24 bits, addition 32-40 bits Harvard, bancs et bus adresses/données multiples Accès aux données Localité temporelle d’exécution Flots de données (streaming) Temps réel ARCHI’07 - 45 Modes d’adressage complexes Boucles matérielles (zerooverhead), caches d’instructions spécifiques Pas de cache de données, DMA puissants, mémoires SRAM internes Gestion des interruptions Puissance de calcul II. Architecture MAC/Harvard MIPS (Millions of instructions per second) • Mesure facile mais… • …peu représentatif des performances réelles 1. Genèse des DSP : MAC/Harvard 2. Modélisation des générations 1 et 2 Panorama des DSP 3. Performances o VLIW, génération des adresse MOPS (Millions of operations per second) MMACS (Millions of MAC per second) • Prise en compte de l’aspect traitement du signal • Les autres opérations ne sont pas prises en compte MOPS/W : Efficacité énergétique ARCHI’07 - 47 Métriques de performance Contenu d’un benchmark Comparaison précision - effort d’implantation Différents niveaux Précision de la métrique • Applications complète Applications Taches o Système de vidéo-conférence, émetteur/récepteur radiomobile, player MP3 ... • Taches d'une application o Codeur ou décodeur audio ou vidéo, codeur de parole, décodeur de Viterbi Cœurs d’algorithme Benchmarking MMACS/MOPS • Cœurs d'algorithme o FIR, IIR, FFT, Control, .. • Opérations MIPS o ADD, Mult/MAC, Décalage, Transfert mémoire Disponibilité … Effort d’implantation ARCHI’07 - 48 ARCHI’07 - 49 BDTImark2000 BDTIMARK http://www.bdti.com Basé sur des cœurs d’algorithme de traitement du signal o o o o o o o o o o o Filtre FIR réel, traitement par blocs Filtre FIR réel, traitement par échantillons Filtre FIR complexe, traitement par blocs Filtre adaptif LMS Filtre IIR, 2 cellules d'ordre 2 cascadées Produit de vecteurs Addition de vecteurs Recherche de la valeur maximale d’un vecteur Décodeur de Viterbi FFT 256 points Manipulation de bits Code optimisé manuellement ARCHI’07 - 50 ARCHI’07 - 51 Temps d’exécution (FFT) Coût Important pour une production à fort volume Zoran ZR3800x Texas Instruments TMS320C80 Texas Instruments TMS320C541 • Faible coût Texas Instruments TMS320C52 Texas Instruments TMS320C44 o Les DSPs sont efficaces en MIPS/mW et en MIPS/mm2 o Cela se paye sur la flexibilité et la programmabilité Texas Instruments TMS320C31 Texas Instruments TMS320C209 SGS-Thomson D950-CORE NEC PD77015 Motorola DSP56166 Motorola DSP56002 mW/MIPS M68K $200 IBM MDSP2780 DSP Group OAK DSP Group PINE Lucent Technologies DSP 3207 Lucent Technologies DSP32C Lucent Technologies DSP 1627 Analog Devices ADSP-21062 I386 $300 DSP1 $150 Pentium $500 Pentium MMX $700 DSP32C $250 DSP16A $15 Analog Devices ADSP-2171 0 100 200 300 400 500 600 700 800 900 DSP16210 <$10 DSP1600 $10 Execution Tim e (s) ARCHI’07 - 52 I286 $200 ARCHI’07 - 53 [Ackland ISLPD98] Coût – performance (FFT) Énergie Filtrage numérique RIF Zoran ZR3800x C549 Texas Instruments TMS320C541 • 100 MHz, 2.5V 18 NEC PD77015 Motorola DSP56166 Motorola DSP56002 IBM MDSP2780 Lucent Technologies DSP 3207 Lucent Technologies DSP32C Lucent Technologies DSP 1627 Analog Devices ADSP-21062 Analog Devices ADSP-2171 0 10000 20000 30000 40000 50000 60000 70000 Cost-Time Product (s$) ARCHI’07 - 54 16 14 12 ARCHI’07 - 55 Virgule Fixe Virgule Flottante C6201 • 200 MHz, 1.8V DSP16210 • 100 MHz, 3.3V 10 ZSP16401 8 6 • 200 MHz, 2.5V 4 ADSP-21160 2 • 100 MHz, 2.5V 0 C6701 C6 70 1 Texas Instruments TMS320C31 Texas Instruments TMS320C209 C5 49 Watt-microsecondes Texas Instruments TMS320C44 C6 20 1 DS P1 62 10 ZS P1 64 01 AD SP -2 11 60 Texas Instruments TMS320C52 • 167 MHz, 1.8V Évolution des DSP III. Évolution des DSP 1. 2. 3. 4. 5. 6. DSP conventionnels améliorés Capacités SIMD DSP hybride MCU VLIW Superscalaire Comparaison de performances Améliorer les performances au delà de l'augmentation liée à la vitesse d'horloge ? Augmenter le parallélisme • Augmentation du nombre d'opérations exécutées dans chaque instruction • Augmentation du nombre d'instructions exécutées par cycle d'horloge Ajouter des unités spécialisées Améliorer le contrôle ARCHI’07 - 57 Plus d’opérations par instruction Plus d’instructions par cycle Augmenter le nombre d'opérations qui peuvent être exécutées dans chaque instruction L'objectif est ici de profiter du parallélisme au niveau instruction (ILP) d'une application Deux techniques sont bien connues : • Ajouter des unités d'exécution o o o o multiplieur, additionneur, ... jeu d'instruction à enrichir taille de l'instruction à augmenter bus de transfert mémoire à augmenter • VLIW : empaquetage de plusieurs instructions de type RISC dans une seule "super-instruction" • Superscalaire : exécution parallèle de plusieurs instructions sélectionnées dynamiquement par le processeur • Augmenter les capacités SIMD (ou SWP) Dans le même ordre d'idées • Utiliser des unités fonctionnelles spécialisées • Utiliser un coprocesseur • Architectures hybrides DSP/MCU ARCHI’07 - 58 ARCHI’07 - 59 Générations DSP conventionnels améliorés Performances normalisées (BDTImark) 10000 4ème génération 1000 StareCore(300MHz) TMS320C62x (300MIPS) Carmel (300 MHz) DSP56301 TMS320C54x (50-100MIPS) ADSP2183 (50MIPS) 2ème génération DSP56001 (13MIPS) ADSP21xx (13MIPS) TMS320C50 10 • TMS320C54x Architectures multi-MAC DSP16210 (100 MIPS) 100 Troisième génération (1995) Ajout d’unités spécialisés ou utilisation de coprocesseurs • Lucent DSP 16xxx Multiprocesseurs sur une puce 3ème génération • Principalement pour image/vidéo • TMS320C80, MC68356 1ère génération TMS320C20 (5 MIPS) TMS320C10 (2.5 MIPS) 1 1980 ARCHI’07 - 60 1982 1984 1986 1988 1990 1992 Année 1994 1996 1998 2000 2002 ARCHI’07 - 62 Architecture C54x DB C54x C54x • 40-100-160 MIPS • 1000-2000-3000 MIPS/W • 60% of cellular handsets • $5 for C5402 100MIPS - $75 CB PB DB DB CB DB CB EB 17x17b mult. 40b ALU 40b adder ACS unit Viterbi,LMS FIRS, FFT • Dual cores (C5420) ARCHI’07 - 63 ARCHI’07 - 64 C54x C54x FIR symétrique A B Bus1 A Bus1 T Mult Add A Bus1 Bus2 Bus3 x(N-i-1) x(i) + x h(i) + y y ALU A B Bus1 T ARCHI’07 - 65 A B 0 A B Bus1 Bus2 DFG du coeur de la boucle ARCHI’07 - 66 A B ALU ALU A B A B MAC Bus4 C54x C54x e.g. N=20 Ressources du C54x T + x + + A x + + x + + x + + x + + 2 3 4 B Mul/Add x + 1 10 9 8 7 + 5 6 x + ALU + Bus 1 x(0) Bus 2 x(15) + + + + + + + + + Bus 3 + x ARCHI’07 - 67 + Bus 4 ARCHI’07 - 68 Architectures multi-MAC FIR sur DSP conventionnel • e.g. Lucent DSP 16xx DO N TIME: acc=acc+P // P=X*Y // Y=*r0++ // X=*r1++ Architectures multi-MAC Bus X 16b Bus I 16b MULT ALU FIR sur DSP dual-MAC Bus X 32b • e.g. Lucent DSP 16xxx Bus I 32b o 400 MIPS, 380mW o $5 - $80 DO N/2 TIME: acc=acc+P0+P1 // P0=X0*Y0 // P1=X1*Y1 // Y=*r0++ // X=*r1++ MULT ALU MULT ADDER Exécution en N cycles Exécution en N/2 cycles 2 ACC ARCHI’07 - 69 8 ACC ARCHI’07 - 70 Architecture C55x C55x C55x FIR sur C55x dual-MAC • Jusqu'à 20 MIPS/mW • C54x o Consommation -85% o Performances 5x C5510 • • • • rptblocal sample_loop-1 mov *AR0+,*AR1 ; Put new sample to signal buffer x[n] mov *AR0+,*AR3 ; Put next new sample to location x[n+1] mpy *AR1+,*CDP+,AC0 ; The first operation :: mpy *AR3+,*CDP+,AC1 || rpt CSR mac *AR1+,*CDP+,AC0 ; The rest MAC iterations :: mac *AR3+,*CDP+,AC1 macr *AR1,*CDP+,AC0 :: macr *AR3,*CDP+,AC1 ; The last MAC operation mov pair(hi(AC0)),dbl(*AR2+); Store two output data sample_loop 160 MHz, 320 MIPS 80mW 4 MIPS/mW 160 KW SRAM C5502 • 400 MIPS • 160 mW • 2.5 MIPS/mW ARCHI’07 - 71 ARCHI’07 - 72 Capacités SIMD (ou SWP) Opérations parallèles sur différentes largeurs de chemins de données (16 bit, 8 bit, ...) • Split unités d'exécution • Unités d'exécution multiples Exemples • Lucent DSP16xxx, ADI ADSP-2116x, ADI TigerSHARC, TI C64x 16 bits 16 bits x,+,- ARCHI’07 - 73 16 bits 16 bits x,+,- 16 bits 16 bits Avantages et inconvénients Méthode Augmenter le nombre d'UE Augmenter les capacités SIMD Matériel dédié ARCHI’07 - 74 Avantages Inconvénients Augmentation limitée de la consommation, du coût et de la densité de code Augmentation importante de la complexité Difficulté à programmer et à compiler Compatibilité maintenue Perspectives limitées Gain en performance très Nécessité d'avoir un important pour des parallélisme au niveau des traitements par blocs données important Modifications architecturales limitées Consommation mémoire importante Gain en performance important Nécessite une bonne connaissance de l'application Architecture hybride DSP/MCU III. Évolution des DSP 1. 2. 3. 4. 5. 6. Associer des fonctionnalités MCU… DSP conventionnels améliorés Capacités SIMD DSP hybride MCU VLIW Superscalaire Comparaison de performances • gestion efficace des ITs • manipulation de bits • exécution conditionnelle à des fonctionnalités DSP, • calcul intensif pour obtenir un code performant et efficace • limiter la taille du code et donc du circuit ARCHI’07 - 76 Architecture hybride DSP/MCU Architecture Hybride DSP/MCU Méthodes de couplage ST100, ST122, ST140 (STMicroelectronics) Méthode Multiprocesseur Coprocesseur Avantages 2 jeux d'instructions Les 2 cœurs travaillent en // Pas de conflits de ressources Les 2 cœurs travaillent en // Inconvénients Duplication de ressources Deux outils de développement • 32 bits MCU / 16 bits DSP • Fonctionnalités DSP o MAC, architecture Harvard, modes d’adressages complexes • et microcontrôleur o architecture load/store, large espace d’adressage, code compact Modèle de programmation plus complexe Transferts de données Extension Solution Hybride Modèle de programmation plus simple Contraintes imposées par l'architecture initiale Architecture plus "propre" Développement plus risqué Contrôleur mémoire instruction @ d UC Mémoire UT UA Contrôleur mémoire donnée ARCHI’07 - 77 ARCHI’07 - 78 ST 140 Compatible ST100 Compatible ST122 (dualMAC) Flexible 16-bit/32-bit Load/Store architecture 4-MAC/4-ALU Two data clusters Double data memory bandwidth ST140-DSP Core in 0.13m process Frequency up to 600 MHz Intensive Processing 2.4 GMAC/s Large Data Bandwidth 9.6 Gbytes/s Power Consumption down to 0.180 mW/MHz III. Évolution des DSP 1. 2. 3. 4. 5. 6. 100 mW, 24 MMAC/mW DSP conventionnels améliorés Capacités SIMD DSP hybride MCU VLIW Superscalaire Comparaison de performances ARCHI’07 - 79 Very Long Instruction Word Parallélisme niveau instructions . . INS N ALU MAC MU INS3 – Ordonnancement des instructions – compilation – Run-time – Unité de dispatch ARCHI’07 - 81 INS1 INS2 ? INS4 INS6 INS5 Caractéristiques ... Time INS 1 INS 2 INS 3 ... • Plusieurs instructions par cycle, empaquetées dans une "super-instruction" large • Architecture plus régulière, plus orthogonale, plus proche du RISC • Jeu de registres uniforme, plus large Exemples • • • • TI TMS320 C62x et C64x ADI TigerSHARC ADS-TS20x Freescale (Motorola) MSC71xx et MSC81xx StarCore SC1400 Agere/Motorola (DSP core) ARCHI’07 - 82 Texas Instruments TMS 320C6x VLIW : C62xx 256 MPY MPY ADD ADD MV STW ADD MPY SHL ADD SUB STW STW ADDK ADD B ADD SUB LDW LDW B MVK NOP NOP MPY MPY ADD ADD STW STW ADDK NOP Fetch VLIW CPU with eight functional units (RISC-like code) 2400 MIPS @ 300MHz CPU • Two sets of functional units including: o Two multipliers o Six arithmetic logic units (ALUs) o 32 registers with 32-bit wordlength each o Data-addressing units .D1 and .D2 exclusively responsible for data transfers between memory and the register files 32x8=256 bits Dispatch Unit L:ALU S:Shift+ALU M:Multplier D:Address Functional Unit .L1 Functional Unit Functional Unit Functional Unit .S1 .M1 .D1 Functional Unit .D2 Register File A Functional Unit Functional Unit Functional Unit .M2 .S2 .L2 Register File B 1M-bit on-chip memory 32-bit ext. mem. interface 2 enhanced-buffered serial ports 16-bit host access port (Host processor access to on-chip data memory) Flexible PLL clock generator (x ext. clock rate for 2 or 4) Price: $9-$102 • • • • Data Memory Controller Data Address 1 8-/16-/32-bit data support 40-bit arithmetic options Saturation and normalisation Bit-field manipulation and instruction: extract, set, clear, bit counting Data Address 2 ARCHI’07 - 83 ARCHI’07 - 84 Internal Memory Exploitation du parallélisme Exploitation du parallélisme Déroulage des boucles : augmente l'ILP Pipeline logiciel : maximiser l’IPC For(i=0;i<N;i+=3) { ACC=ACC + x[i].h[i] ACC=ACC + x[i+1].h[i+1] ACC=ACC + x[i+2].h[i+2] } For(i=0;i<N;i++) { ACC=ACC + x[i].h[i] } • Optimisation du code assembleur Prologue LOAD MULT LOAD LOAD MULT N/3 ACC LOAD N MULT MULT LOAD LOAD ACC ACC MULT MULT ACC Taux d’utilisation du processeur Épilogue 100% ARCHI’07 - 85 ACC ACC 100% ARCHI’07 - 86 Taux d’utilisation du processeur C6x Functional Unit Functional Unit Functional Unit Functional Unit Functional Unit Functional Unit Functional Unit Functional Unit .L1 .S1 .M1 .D1 .D2 .M2 .S2 .L2 Exploitation du parallélisme Filtre FIR sur DSP VLIW C6x Register File A Register File B x[0] = input; acc = 0; for (i=0; i<8; i++) { prod = h[i] * x[i]; acc = acc + prod; } output = (short) (acc >> 15); Data Memory Controller Instruction Description LDH ADD Charge une donnée 16 bits venant de la mémoire dans un registre Charge deux données 16 bits consécutives venant de la mémoire Multiplication entre 2 registres, résultat dans un troisième Addition SUB Soustraction B NOP LDW MPY Nombre de cycles 5 Unités .M Unités .L Unités .S Unités .D - - - .D1 .D2 5 - - - .D1 .D2 2 .M1 .M2 - - - 1 - 1 - Branchement 6 - .L1 .L2 .L1 .L2 - .D1 .D2 .D1 .D2 - aucune opération 1 - - .S1 .S2 .S1 .S2 .S1 .S2 - ARCHI’07 - 87 Méthodes d’optimisation Depuis le code “RISC” Instructions en parallèle Enlever les NOP Déroulage de boucle Pipeline logiciel Lecture mémoire de paquets de données 2 LDH 1 LDW 2 LDW 1 LDDW ARCHI’07 - 89 - 1 Start 2 3 Loop 4 5 6 7 8 9 [B0] 10 [B0] MVKL .S2 8, B0 MVKL .S1 0, A5 LDH .D1 *A8++,A2 LDH .D1 *A9++,A3 NOP 4 MPY .M1 A2,A3,A4 NOP ADD .L1 A4,A5,A5 SUB .L2 B0,1,B0 B .S1 loop // Update most recent sample // Zero accumulator // 8 taps // perform Q.15 multiplication // Update 32-bit accumulator // Cast output to 16 bits ; ; ; ; ; ; ; ; ; ; Intialize the loop counter (B0) to 8 Intialize the accumulator (A5) to 0 Load x(i) in A2 Load h(i) in A3 LDH has a latency of 5 cycles Multiply x(i) and h(i) in A4 MPY has a latency of 2 Add A4 to the accumulator A5 Sub 1 to the counter B0 Branch to loop if B0 <> 0 ARCHI’07 - 88 Code non optimisé loop: loop: ldh.d1 ldh.d1 ldh.d1 ldh.d1 nop *A8++,A2 *A9++,A3 4 mpy.m1 mpy.m1 nop add.l1 add.l1 A2,A3,A4 sub.l2 sub.l2 [b0] b.s1 nop ARCHI’07 - 90 A4,A6,A6 B0,1,B0 loop 5 Code RISC 40 itérations 16*40 = 640 cycles Instructions parallèles loop: ldh.d1 || ldh.d2 ldh.d2 nop mpy.m1x mpy.m1x nop add.l1 sub.l2 [b0] b.s1 nop *A8++,A2 *B9++,B3 4 A2,B3 ,A4 A2,B3,A4 Parallélisme ? 40 itérations 15*40 = 600 cycles Remplacer les NOP loop: ldh.d1 || ldh.d2 ldh.d2 nop *A8++,A2 *B9++,B3 4 mpy.m1x mpy.m1x nop add.l1 A4,A6,A6 B0,1,B0 loop 5 Not Optimized Properly A2,B3 ,A4 A2,B3,A4 Instructions à la place des NOP Dépendances interinstructions LDH A4,A6,A6 sub.l2 [b0] b.s1 nop B0,1,B0 loop 5 LDH a b 5 5 MPY * 2 ADD 1 + loop 1 ARCHI’07 - 91 B 6 ARCHI’07 - 92 Remplacer les NOP loop: ldh.d1 || ldh.d2 ldh.d2 sub.l2 [b0] b.s1 nop mpy.m1x mpy.m1x nop add.l1 ARCHI’07 - 93 count SUB *A8++,A2 *B9++,B3 B0,1,B0 loop 2 A2,B3 ,A4 A2,B3,A4 A4,A6,A6 Déroulage de boucles Instructions à la place des NOP 40 itérations 8*40 = 320 cycles Déroulage + ré-ordonnancement des instructions Cycle 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 ARCHI’07 - 94 .D1 LDH LDH LDH LDH LDH LDH LDH LDH LDH .D2 LDH LDH LDH LDH LDH LDH LDH LDH LDH .L1 ADD ADD ADD ADD ADD ADD ADD ADD ADD .L2 .M1 MPY MPY MPY MPY MPY MPY MPY MPY MPY .M2 .S1 .S2 NOP N=40 itérations 7 + (N-7) +7 = 47 cycles 47 instructions VLIW! Accès mémoire multiples Pipeline logiciel Réintroduction de la boucle sur le motif répété Cycle 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 .D1 LDH LDH LDH LDH LDH LDH LDH LDH LDH .D2 LDH LDH LDH LDH LDH LDH LDH LDH LDH .L1 ADD ADD ADD ADD ADD ADD ADD ADD ADD .L2 SUB SUB SUB SUB SUB SUB SUB .M1 MPY MPY MPY MPY MP Y MPY MPY MPY MPY MPY .M2 .S1 .S2 B B B B B B A7 a1 * x1 47 cycles 15 instructions A0 LDW.D1 *A5++,A0 x0 A1 LDW.D1 *A6++,A1 = A3 a0 * x0 MPY.M1 A0, A1, A3 MPYH.M1 A0, A1, A7 + a1x1 + a0x0 A4 ADD.L1 A3, A7, A4 ARCHI’07 - 96 Accès mémoire multiples StarCore SC1400 core Lecture de 4 données + 2 MAC en parallèle ARCHI’07 - 97 a0 x x1 ARCHI’07 - 95 Cycle 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 a1 NOP .D1 LDW LDW LDW LDW LDW LDW LDW LDW .D2 LDW LDW LDW LDW LDW LDW LDW LDW .L1 ADD ADD ADD ADD ADD ADD ADD ADD ADD .L2 ADD ADD ADD ADD ADD ADD ADD ADD .M1 .M2 MPY MPY MPY MPY MPY MPY MPY MPY MPYH MPYH MPYH MPYH MPYH MPYH MPYH MPYH .S1 .S2 NOP Processeur VLIW 16 bits développé en commun par Agere (Lucent) et Freescale (Motorola) 300 MHz, faible tension Optimisé pour faible consommation • Meilleure densité de code (16 bits) que C6x • Pipeline plus simple (5 étages contre 11) N=40 itérations 7 + (N/2-7) +8 = 28 cycles BMU ARCHI’07 - 98 MAC ALU Shift MAC ALU Shift MAC ALU Shift MAC ALU Shift VLIW combiné au SIMD VLIW combiné au SIMD ADI TigerSHARC C64x • Jusqu’à 1.1 GHz, ~9 GOPS • Six ALUs (32/40-Bit) • Combine le VLIW au SIMD afin d'atteindre un parallélisme massif • SIMD hiérarchique o une 32/40-Bit, deux 16-Bit, ou quatre 8-Bit opérations arithmétiques par cycle et par ALU o Le TigerSHARC peut exécuter 8 multiplications 16x16 en virgule fixe par cycle (4x le C62xx) • Deux multiplieurs, quatre 16x16-Bit ou huit 8x8-Bit multiplications par cycle • Coprocesseurs VCP (Viterbi) et TCP (Turbo) Instruction SIMD ALU MAC Shift 4 MAC 16 bits ARCHI’07 - 99 C64x ALU MAC Shift 'C6411: 300 MHz, $39, 1.0 V, 250mW, 2400 MIPS, 1200 MMACS 4 MAC 16 bits ARCHI’07 - 100 Superscalaire Techniques dérivées des processeurs généraux hautes-performances • Prédiction de branchement • Cache dynamique Plusieurs (2-4) instructions par cycle Jeu d'instructions de type RISC Parallélisme important LOOP // LDDU Exemple • LSI Logic LSI40x o 4-way, 260MHz ARCHI’07 - 101 ARCHI’07 - 102 (ZSP400 core) FIR on LSI40x R4, R14, 2 LDDU R8, R15, 2 MAC2.A R4,R8 AGN0 LOOP Avantages et inconvénients Méthode Avantages Grand bon dans les performances VLIW Superscalaire Architectures plus orthogonales meilleures cibles pour les compilateurs Grand bon dans les performances Architectures plus orthogonales meilleures cibles pour les compilateurs Pas de problèmes de séquencement Générations : bilan Inconvénients Bande passante vers la mémoire importante Forte consommation Séquencement délicat Augmentation de la taille du code importante Bande passante vers la mémoire importante Plus forte consommation Temps d'exécution difficilement prédictible ARCHI’07 - 103 ARCHI’07 - 104 ARCHI’07 - 105 ARCHI’07 - 106 Processeurs récents (2006) Vitesse (BDTImark2000) DSP • • • • • Analog Devices BF53x (Blackfin) Analog Devices TS20x (TigerSHARC) Freescale MC1xx/81xx Texas Instruments C55x Texas Instruments C64x Processeurs applicatifs • • • • Intel PXA255/26x (XScale) Intel PXA27x (XScale + Wireless MMX) Samsung S3C24xx (ARM9) Texas Instruments OMAP 591x (ARM9 + C55x) ARCHI’07 - 107 Coût – performance (mark/$) ARCHI’07 - 109 ARCHI’07 - 108 Efficacité énergétique (mark/mW) ARCHI’07 - 110 Efficacité mémoire (memmark) ARCHI’07 - 111 BDTIMark ARCHI’07 - 112 Flot de développement général III. Flot de développement Développement (actuel) d'applications (signal) Algorithme 1 1. Flot général de développement 2. Compilation pour DSP 3. Arithmétique virgule fixe Mise au point de l'algorithme – Matlab/Simulink – SPW, Ptolemy, CoCentric – VCC Génération manuelle ou automatique Code C "flottant" – Compilateur C, debugger – Utilisation de vecteurs de test issus de la simulation système Génération manuelle Code C "fixe" ARCHI’07 - 114 – Compilateur C, debugger – Utilisation de vecteurs de test issus de la simulation système Flot général (suite) Algorithme 1 Code C Outils de développement Implantation logicielle – Compilateur C pour DSP – Simulation assembleur Spécifications flots de données du TS, prototypage rapide, simulation, validation • Matlab/Simulink, Cadence SPW, Synopsys Cossap, Ptolemy Outils de profiling Système d'Exploitation Temps Réel Implantation Matérielle Algorithme 2 Code C – Traduction en VHDL – Synthèse du circuit – Simulation VHDL • gprof, ... Compilateurs depuis des langages de haut-niveau • DSP en virgule fixe ou flottante Optimisations de l'assembleur Critères de sélection des outils et du langage • Compilateurs : taille et vitesse du code • Simulateurs : vitesse Algorithme N Code C ARCHI’07 - 115 ARCHI’07 - 116 Compilation Inefficacité des compilateurs C Compilation C vs optimisation assembleur Surcoût associé au compilateur • e.g. STMicrolectronics Assembl er MCU 28% Assembl er DSP 55% Code C DSP 8% Code C Ctrl 9% Code C MCU 5% Assembler MCU 25% Assembler DSP 25% Code C DSP 45% Facteur 4 à 10 (virgule fixe) Facteur 2 à 4 (flottants) Orthogonalité 1000 800 Sur coût (%) Conception de code enfoui dans l'industrie Sur coût temps d'execution 1200 ANSI C C modifié 600 400 200 • VLIW 0 [Paulin97] ARCHI’07 - 117 ADSP21xx/ ADI [Paulin00] DSP56002/ Motorola TMS320C51/ TI Processeurs ARCHI’07 - 118 TMS320C54/ TI TMS320C62/ TI Inefficacité des compilateurs C Raisons de l’inefficacité Surcoût associé au compilateur Absence de support de l’arithmétique virgule fixe Inefficacité des techniques classiques de développement des compilateurs Sur coût taille du code 400 350 ANSI C • Taille du code 300 o développement de l'architecture puis du compilateur compilateurs reciblables C modifié Sur coût (%) 250 200 Inefficacité des techniques classiques de compilation 150 100 o architecture non orthogonale, unités spécialisées, instructions complexes 50 0 Absence de support des spécificités des DSP -50 o registres d’état, modes d’adressage (modulo, bit inversé)... -100 ADSP21xx/ ADI DSP56002/ Motorola TMS320C51/ TI TMS320C54/ TI Processeurs ARCHI’07 - 119 TMS320C62/ TI Extensions du langage C : e.g. Embedded C ARCHI’07 - 120 Formats de codage III. Flot de développement Virgule fixe • Représentation : signe - partie entière - partie fractionnaire nx mx 1. Flot général de développement 2. Compilation pour DSP 3. Arithmétique virgule fixe S bm-1 bm-1 b1 b0 b-1 b-2 m 1 bn-2 bn-1 bn x = (2) m S + bi 2i CA2 i = n o bx = m x + n x + 1 o le format d’une donnée ne varie pas au cours du temps Virgule flottante • Représentation : exposant - mantisse Exposant e bits SE d1 d2 Mantisse M+1 bits de-1 SE C1 C2 C3 Cm-2 Cm-1 Cm 1 M x = 2u (1) S E + Ci 2i 1 2 i =1 E 1 avec u = (1) S E d i 2i i =1 ARCHI’07 - 122 Comparaison fixe - flottant Eléments de l’UT Virgule fixe (>90% des ventes des DSP) Multiplieur câblé Additionneur U.A.L. • Précision importante mais problèmes de débordement o nécessité de recadrer les données • • • • Temps de développement plus long Efficacité énergétique plus importante, plus rapide et moins cher Consommation moins importante Marché : applications grand public 2N+bg Accumulateur Gestion des débordements Bits de garde Registres d’accumulation Sat /Arr stockage des données en double précision ARCHI’07 - 123 ARCHI’07 - 124 Codage en virgule fixe : objectifs Règles de l’arithmétique virgule fixe mA SA bmA nA b1 + b0 b-1 b-2 mB mBnB bnA nB SB SB SB bmB Sb0 bb-1 bb-2 bbnB b0 b0 B mB 0 -1 -2 nB SR bmR b1 b0 b-1 b-2 m R = max(m A , m B ) + 1 • Représentation identique • Doublement du bit de signe bnA Objectifs pour le codage en virgule fixe • Garantir l’absence de débordements o Connaissance du domaine de définition des données • Maximiser la précision n R = max(n A , n B ) mA Multiplication: a b SA bmA b1 nA b0 b-1 b-2 bnA mB Minimiser le nombre de bits de poids fort non utilisés Minimiser le pas de quantification nB SB bmB b0 b-1 bnB S bm-1 bm-1 SR SR bmR b1 mR = m A + mB ARCHI’07 - 125 + recadrage des données • C67x > $30 o Alignement de la virgule o Extension de bits Registres à décalage Temps de développement plus rapide, compilateurs plus efficaces Plus grande portabilité, pas de recadrage Pas de débordements : dynamique de 1500dB (32 bits) Plus cher, consomme plus • Format de a et b identique • Choix d’un format commun N MAC Virgule flottante Addition: a+b B N 2N • C5x > $5 • • • • A (1 Op/cycle) b0 b-1 b-2 b1 b0 b-1 b-2 bn-2 bn-1 bn bnR PMSB nR = nA + nB ARCHI’07 - 126 PLSB Codage en virgule fixe : étapes Fil rouge : filtre FIR N 1 1. Détermination de la dynamique des données y ( n ) = ai x ( n i ) Méthodes statistiques ou analytiques 2. Détermination de la position de la virgule i =0 3. Détermination de la largeur des données z-1 x (n) a0 Opérateurs SIMD, précision multiple z-1 a1 4. Evaluation de la précision des calculs + Méthodes par simulation ou analytiques ARCHI’07 - 127 aN-2 z-1 + Dynamique des données float x[N] = {0.123, -0.569,...} /* Signal d’entrée du filtre */ float h[N] = {-0.0295, 0.0364,.., -0.0295 }; /* Coefficients du filtre */ int main() { float x[N], y[M], acc; int i,j; Normes utilisées en TS Norme L1 /* Initialisation variables internes */ for(j=0; j<M; j++) { /* Filtrage du vecteur d'entrée input */ x[0] = Input[j]; acc = x[0]*h[0] ; for(i=N-1; i>0; i--) { acc = acc + x[i]*h[i]; /* Calcul d'une cellule du filtre */ x[i] = x[i-1]; /* Vieillissement du signal */ } y[j] = acc; } z max1 = max n (x(n) ). h(m) m = Norme Chebychev z max 2 = max n , (x(n) )max(H ( ) ) + y (n) Méthode garantissant l’absence de débordements Méthode garantissant l’absence de débordements pour un signal d’entrée à bande étroite e.g. x(n)=cos(wt) Arithmétique d’intervalle (non récursifs) } ARCHI’07 - 129 ARCHI’07 - 128 Fil rouge : filtre FIR for(i=0; i<N; i++){x[i] = 0;} aN-1 ARCHI’07 - 130 Filtre FIR Filtre FIR Propagation de la dynamique (intervalles) des entrées au sein du GFS représentant l’application Détermination de la position de la virgule pour les données Insertion des opérations de recadrage pour aligner la virgule Dx = 0.99 z-1 mx = 0 [-1,1] z-1 x (n) z-1 x[i] z-1 x[i-1] Da = 0,4 a0 [- |a0|, |a0| ] a1 aN-2 aN-1 ma = 1 N 1 N 1 ai , ai i =0 i =0 [- |a1|, |a1| ] + Norme L1 + + ai N 1 m = m =0 >> 1 m'MULT ' = 1 ARCHI’07 - 132 Graphe flot de données d’une cellule du FIR Sources de bruit dans un FIR Bruit de quantification associé à l’entrée Bruit lié au recadrage externe Recadrage des coefficients [ xm , xm ] x (n) b0 z-1 >> >> >> b1 z-1 >> bN-2 >> >> bN-1 x (n) >> Renvoi en mémoire du résultat >> b0 Filtre FIR + + Recadrage interne + b m k = log 2 ( K ) b1 + b1 + z-1 bN-2 + b N-2 bgm1 + bN-1 + b N-1 bgm N-2+ bgm N-1+ + + + + Filtre FIR Biais lié au codage des coefficients m = ARCHI’07 - 133 z-1 bg mem [ K .xm , K .xm ] K= + bgm0 + >> z-1 + b0 y (n) + Bruit lié au renvoi en mémoire du résultat bx z-1 >> ACC + m ADD = max(mMULT , m ACC , m ACC ) = 1 Recadrage des données dans un FIR Recadrage externe ACC m ACC = 1 max n (y (n) )= max n (x(n) ). h(m) = ai = 1.65 ARCHI’07 - 131 mMULT = mb + mx + 1 = 0 mMULT = 0 y (n) DACC = 1,65 ARCHI’07 - 134 Bruit lié au recadrage interne y (n) Filtre FIR Filtre FIR : code C virgule fixe Architecture du processeur cible x[i] h[i] • Données en mémoire sur 16 bits • Multiplication 16 bits 16 bits 32 bits • Addition 32 bits + 32 bits 32 bits MULT bmult + ADD int x[M] = {-809, -6180, -1570, ...} int h[N] = {-1933, 2386, 3631,}; /* Signal x, codage (16,0,15)*/ /* Coefficients (16,-1,16) */ Le signal d’entrée et les coefficients sont spécifiés au niveau du code C en entiers sur 16 bits (absence de type virgule fixe en C) : • l’entier représentant x (16,0,15) est obtenu en multipliant x par 215 • l’entier représentant h (16,-1,16) est obtenu en multipliant h par 216 int main() { int x[N]; y[M]; long acc; int i,j; ACC (16,0,15) x (n) z-1 a0 (16,-1,16) z-1 a1 (32,0,31) >> 1 aN-2 z-1 >> 1 >> 1 + + + (32,1,30) y (n) Filtre récursif (IIR) z-1 b1 /* Calcul d'une cellule du filtre */ /* Vieillissement des variables internes */ Réduction de la largeur de la variable 32 bits 16 bits Récupération des 16 bits les plus significatifs de la donnée (l ’opération de cast sur acc permet de récupérer les bits de poids faible uniquement) ADD0 + b0 … yn yi-1(n) sortie cellule précédente + + a2,i a1,i wi(n-2) wi(n-1) wi(n) a1 z-1 b2,i b1 b2 z-1 a2 wn +yn b0 z-1 + } } (entrée) x(n) ADD 1 wn a1 for(i=N-1; i>0; i--) { acc = acc + ((long)(x[i]*h[i])>>1); x[i] = x[i-1]; } y[j] = (int)(acc>>16); Recadrage de la sortie de la multiplication : changement de format : (32,0,31) (32,1,30) Filtre IIR d’ordre 2 (cellule i) Cascade de cellules d’ordre 2 /* Filtrage du vecteur d'entree input */ ARCHI’07 - 136 Renvoi de la donnée en mémoire + for(j=0; j<M; j++) { x[0] = Input[j]; acc = (long)(x[0]*h[0])>>1; (16,1,14) ARCHI’07 - 135 ADD 0 /* Initialisation des variables internes du filtre */ aN-1 >> 1 (32,1,30) xn for(i=0; i<N; i++){x[i] = 0;} a2 b1,i + b2 b0,i ADD1 + y (n) (sortie) yi(n) (entrée cellule suivante) ARCHI’07 - 137 ARCHI’07 - 138 Dynamique des données (IIR) Dynamique des données (IIR) Sources de débordements : additionneurs Exemple 2 • IIR : 2 sources ADD0 et ADD1 x [1,1] H ( z) = ADD 1 wn ADD 0 xn + + =2 0 0.5 1 1.5 z-1 h D ( m) = 9 mw = 4 k1 = 4 1 1 + a1 z + a2 z 2 ymax1 = xmax . h(m) 1 H ( z) = 1 b2 2 b0 + b1 z + b2 z 1 + a1 z 1 + a2 z 2 ARCHI’07 - 139 a1 a2 b2 b0 b1 = -27951 = 27581 = 16384 = 16384 = -7956 Dynamique des données (IIR) Position de la virgule (IIR) mx = log 2 (max n (x(n) ))= 0 H1 ( z ).H 2 ( z ).H 3 ( z ) mwi = log 2 (max n (wi (n) ))= 4 H1 ( z ).H 2 ( z ) H1 ( z ) H1(z) H 1D ( z ) y1(n) y2(n) H2(z) y3(n) H3(z) w2(n) w3(n) H1 ( z ).H 2 ( z ).H 3 D ( z ) 1 b + b z 1 + b2i z 2 H iD ( z ) = H i ( z ) = 0i 1i 1 1 + a1i z 1 + a2i z 2 1 + a z + a z 2 1i m yi = log 2 (max n (yi (n) ))= 2 maij = log 2 (max j (ai ( w1(n) H1 ( z ).H 2 D ( z ) 3.5 Fonction de transfert des filtres H(z) et HD(z) ARCHI’07 - 140 Cellules d’ordre 2 cascadées 3 Codage des coefficients m = a2 2.5 HD(jw) m = b1 2 xmax a1 m = ARCHI’07 - 141 y wmax1 = xmax . hD (m) x(n) 0 h(m) = 2.5645 m H(jw) 1 0.5 m = H D ( z) = 0.5 0.2428 z 1 + 0.5 1 0.85 z 1 + 0.8417 z 2 xmax yn b0 z-1 1.5 ))= 0 ( ))= 0 mbij = log 2 max j bij m ADD 0 = MAX (mx , mai + mwi + 1, mwi ) = 5 m ADD1 = MAX (mbi + mwi + 1, m yi ) = 5 2i ARCHI’07 - 142 Codage des données (IIR) Conversion flottant-fixe (IRISA) ADD0 (16,mx,,nx) x(n) (16,0,15) (32, madd0 , nadd0) + + C source code (32,5,16) #define pi 3.1416 #define pi 3.1416 main() { float x,h,z for(i=1;i<n;i++) { *z= *y++ + *h++ } for(i=1;i<n;i++) { *z= *y++ + *h++ } C orrelator.C #define pi 3.1416 # define pi 3.1416 #define pi 3.1416 main() { float x,h,z for(i=1;i<n;i++) { *z= *y++ + *h++ } #define pi 3.1416 main() { float x,h,z for(i=1;i<n;i++) { *z= *y++ + *h++ } for(i=1;i<n;i++) { *z= *y++ + *h++ } for(i=1;i<n;i++) { *z= *y++ + *h++ } Floating-point specification C orrelator.C C orrelator.C a2,i A a1,i (16,mw,nw) B wi(n-2) 16 16 wi(n-1) b2,i 32 wi(n) b1,i + b0,i ADD1 + (32, madd1, nadd1) (32,5,16) Binary-point position determination High level synthesis tool BSS Selection Scheduling Allocation 32 Acc Fixed-point conversion (16,4,11) Fixed-point specification optimization Accuracy evaluation Fixed-point specification optimization Code generation tool CALIFE Selection Scheduling Allocation (16,my,ny) (16,2,13) Precision constraint y (n) ARCHI’07 - 143 ARCHI’07 - 144 [Ménard02, Ménard04] Conclusions Conclusions Processeurs spécialisés garantissent : Les processeurs généraux ont maintenant des performances qui concurrencent les DSPs • efficacité énergétique, rapport performances/coût • autres exemples probants o Processeurs multimédia o Network Processor NPU Les performances des processeurs DSPs ont augmenté de 150x sur 15 ans (40% par an) Les nouvelles architectures sont nombreuses • Mais les DSPs conventionnels dominent toujours le volume • Mais le prix ... et la consommation ne sont pas applicables aux applications embarquées grand public La facilité de compilation est un facteur important • time-to-market... Choisir un DSP requiert une analyse fine • qui dépend de l'application... ARCHI’07 - 145 ARCHI’07 - 146 Perspectives Piste 1 : DSP conventionnel Quelle sera l’architecture pour le traitement du signal et de l’image de demain (ou d’après demain) ? DSP conventionnel multi-MAC Unités spécialisés Programmation ? Viterbi Turbo MULT MULT MULT MULT FFT ALU ALU ALU ALU CDMA ACC ARCHI’07 - 147 ARCHI’07 - 148 Piste 1 : DSP conventionnel Piste 2 : ULIW DSP spécialisés Ultra Large Instruction Word • Texas Instruments OMAP 591x • e.g. Silicon Hive AVISPA+ o Mobile 2-3G o ARM9 + C55x Compilation ? SMT ? • Digital Media System-on-Chip (DMSoC): DaVinci o Codec vidéo o ARM926EJ-S Core • 202.5-MHz at 1.05 V or 256-MHz at 1.2 V o C64x+TM • 405-MHz at 1.05 V or 513-MHz at 1.2 V o Blocs dédiés au codage vidéo o Interface imager/DAC/HD ARCHI’07 - 149 ACC ARCHI’07 - 150 Piste 3 : multiprocesseur PicoArray PicoArray (picoChip) Static Interconnect PE: 16-bit 3-way VLIW • ~320 PE (VLIW 3-way) • 160 MHz • 190 GIPS VHDL: structure C/Assembly: PE ARCHI’07 - 151 Piste 4 : FPGA ARCHI’07 - 152 Piste 5 : processeur reconfigurable e.g. Altera Stratix Architecture DART RDP1 Segmented Network RDP2 • Multiplieurs 9x9 – 18x18, 2 GMAC/s par bloc, 250 MHz Ctrl RDP3 RDP4 Ctrl DMA RDP5 Config Mem. FPGA Data. Mem. • 3G/UMTS Mobile Terminal • 802.11a (Channel Est.) • IRISA/R2D2 • STMicroelectronics • CEA LIST/LETI RDP6 Loop Managment AG1 AG2 AG3 AG4 Data mem1 Data mem2 Data mem3 Data mem4 Performances Fully Connected Network reg ARCHI’07 - 153 reg ARCHI’07 - 154 FU1 FU2 FU3 FU4 • • • • • 5-10 GOPS/[email protected] 200MHz, 11mm2 300 mW @ 5 GOPS 16 MOPS/mW @ 5 GOPS Circuit en juin 2005 Bibliographie Bibliographie DSP Processor Fundamentals : Architectures and Features (IEEE Press Series on Signal Processing) by Phil Lapsley, Jeff Bier, Amit Shoham, Edward A. Lee, Wiley-IEEE Press, 1997 Programmable Digital Signal Processors by Yu Hen Hu (Editor), Marcel Dekker, 2001 Digital Signal Processors : Architectures, Implementations, and Applications by Sen M. Kuo, Woon-Seng S. Gan, Prentice Hall, 2004 ARCHI’07 - 155 Bibliographie Digital Signal Processing Applications With Motorola's DSP56002 Processor by Mohammed El-Sharkawy, Prentice Hall, 1996 Digital Signal Processing Implementation Using the TMS320C6000 DSP Platform (With CD-ROM) by Naim Dahnoun, Prentice Hall, 2000 DSP Applications Using C and the TMS320C6x DSK by Rulph Chassaing, Wiley-Interscience, 2002 VLSI Digital Signal Processors: An Introduction to Rapid Prototyping and Design Synthesis by Vijay Madisetti, Butterworth-Heinemann, 1995 Méthodes et architectures pour le TSI en temps réel, de Didier Demigny, Hermès, 2002 ARCHI’07 - 156 Références ARCHI’07 - 157 [David00] R. David, Etat de l'art des cœurs de DSP, Rapport DEA, ENSSAT, 2000. [Sentieys00] O. Sentieys, Etat de l'art des DSP, École thématique du CNRS - Conception de systèmes enfouis, Seix (Ariège), 20-23 novembre 2000. [Sentieys01] O. Sentieys, DSP et processeur superscalaire : la convergence ?, Symposium en Architectures Nouvelles de Machines, Paris, 2001. [Ménard04] D. Ménard, Processeur de traitement du signal, ENSSAT/EII, 2004. [ICE97] B. McClean, “Status 1997: A Report on the Integrated Circuit Industry”, Integrated Circuit Engineering Corporation (ICE), Scottsdale, 1997 [Bhaskaran95] V. Bhaskaran & K. Konstantinides, “Image and Video Compression Standards Algorithms and Architectures”, Kluwer Academic Publishers, Boston, 1995. [Bier97] J. Bier, P. Lapsley & G. Blalock, “Choosing a DSP Processor”, Berkeley Design Technology (BDT), 1997. [DeMan97] H. De Man and al., “Language Based Design of Digital Systems”, AI Course, KU Leuven/IMEC, april 1997. [Lapsley96] P. Lapsley and G. Blalock, “How to Estimate DSP Processor Performance”, IEEE Spectrum, July 1996. [Pirsch97] P. Pirsch: “Video and Image Processing Architectures - Dedicated and Programmable Solutions”, NFWO Symposium on Video Processing Architectures, January 1997. [Ackland98] B. Ackland and C. Nicol, "High Performance DSPs - What's Hot and What's Not?", IEEE Int. Symposium on Low Power Electronic Design ISLPED, 1998. [Ropers99] A. Ropers and al., "DSPstone : TI C54x" Report IISPS AAchen University of Technology, 1999. ARCHI’07 - 158 Webographie http://www.bdti.com http://dsprelated.com/ http://www.ti-training.com/courses http://www.eg3.com/dsp/index.htm Annexes BDTIMark Caractéristiques complémentaires Génération de code pour DSP ARCHI’07 - 159 BDTIMARK ARCHI’07 - 161 ARCHI’07 - 162 ARCHI’07 - 163 ARCHI’07 - 164 ARCHI’07 - 165 ARCHI’07 - 166 Localisation des opérandes Codage des instructions Mémoire Modèle registre-mémoire tacc • Opérandes situées en mémoire et dans les registres Stationnarité temporelle R texec Opérateur o Temps d ’exécution de l’instruction tinst = tacc+ texec • Une instruction définit l’ensemble des opérations à réaliser pour chaque unité fonctionnelle A MULT R1,R2,T Mémoire Modèle « Load-Store » i tacc • Opérandes situées uniquement dans des registres o tinst = max(texec,,tacc) RX Transfert mémoire .U.T. RY Opérateur A ARCHI’07 - 167 ADD T,A,A Unité Multiplieur texec LOAD LD R1,AR1 i+1 i+2 i+3 LOAD LOAD MULT MULT MULT ADD ADD Unité Accumulateur LD R2,AR2 i+4 ADD ARCHI’07 - 168 Codage des instructions Structures de contrôle Stationnarité des données Boucle matérielle • Une instruction définit une séquence complète d ’opérations à réaliser sur un ensemble de données. • Optimiser le traitement des boucles de petite taille o Initialisation des paramètres de la boucle en 1 instruction o Pas d'instructions supplémentaires pour la gestion de la fin de la boucle Instructions de branchement MAC *AR1,*AR2 i Transfert mémoire .U.T. Unité Multiplieur Unité Accumulateur ARCHI’07 - 169 LOAD i+1 LOAD MULT i+2 i+3 i+4 • Branchement multi-cycles: ajout de NOP entre BR et 1ère instruction • Branchement retardé Instructions à prédicat LOAD MULT MULT ADD ADD • Instructions conditionnelles ADD ARCHI’07 - 170 If Then Else [R1] [!R1] INF R1,R5,10 ADD R3,R2,3 ADD R3,R2,3 Modes d’adressage Modes d’adressage Adressage immédiat : Adressage indirecte par registre : directement dans l’instruction la donnée est stockée Adressage registre directe : stockées dans des registres • Registre d’adresse (AR) pointant sur les données (Ex C54x: LD #248, A) LD *AR1, A les données sont • Possibilités de post modifications: (Ex C54 : SUB A, B) Adressage mémoire directe : donnée est stockée dans l’instruction l’adresse de la partie stockée dans un pointeur de page DP 9 bits a11 A10 a9 a8 TMS320C54x 7 bits x0 x1 x2 x5 a0 partie stockée dans l’instruction ARCHI’07 - 171 o linéaire : AR:= AR ± 1 LD *AR1+, A addr = AR1 AR1 = AR1 + 1 o indexé : AR:= AR ± MR LD *ARx+0, A addr = AR1 AR1 = AR1 + AR0 LD *AR1+% ,A addr = AR1 AR1 = circ(AR1 + 1) – MR: registre d’index • Pour limiter le nombre de bits stockés dans l’instruction un adressage paginé est utilisé. L’adresse est composée de deux parties : a15 addr = AR1 (A *AR1) o modulo : (AR:= AR ± 1)N x3 (%) specifies the size of the circular buffer. o bit inversé : FFT addr = ARx ARx = B(ARx + AR0) LD *ARx+0B ,A After access, AR0 is added to ARx with reverse carry (rc) propagation. ARCHI’07 - 172 Génération de code pour DSP Partie frontale Génération d’un code de qualité But: transformation du code source en une représentation intermédiaire (I.R.) o rapide (Texec faible) o compacte (Tcode faible) o sûr de fonctionnement y = k + 60 * x Analyse lexicale id1= id2+60*id3 Analyse syntaxique Intégration des spécificités des DSP = id1 Table des symboles + id2 o arithmétique virgule fixe o spécificités des unités de mémoire et de contrôle k id2 réels …. Analyse sémantique id3 = id1 x id3 réels …. Flexibilité du compilateur Génération I.R. id1 Optimisation I.R. ARCHI’07 - 173 * Entier Réel id3 60 = o compilateur « reciblable » ARCHI’07 [SUIF] - 174 60 + id2 [Leupers97,Marwedel99] * y id1 réels …. + id2 * id3 60.0 Partie finale But: génération d’un code cible à partir de la représentation intermédiaire Sélection d’instructions [SPAM, CHESS, CodeSyn, Calife] o Reconnaissance de motifs [Leupers97, Leupers99] o Couverture d’arbre Programmation dynamique Allocation et assignation de registres o allocation de registres Coloration de graphe o assignation de registres [Araujo95, Wess95] Ordonnancement • Ordonnancement par liste, ILP, de traces Optimisations dépendantes de l’architecture o adresses mémoire [Liao96, Sudarsanam95] ARCHI’07 - 175 Post-optimisations Post-optimisations • instructions de changement de mode • assignation des bancs de mémoire • l’allocation mémoire et la génération des adresses Génération des adresses : exploiter les U.G.A. registres d’adresse : ARi post-modifications (ARi++, ARi--) registres d’offset : MRk (ARi= ARi ± MRk ) Optimiser le placement des données en mémoire afin d’utiliser efficacement les UGA ARCHI’07 - 177 Sélection de code E:= E1 Op E2 Principe : Op • découpage du problème de production de code optimal pour E en sous-problèmes optimaux de production de code pour les sous-expressions E1 et E2 Ri = Rj Rj = Ri op Rj Ri = Ri op Mj Ri = Rj Mi = Ri C =1 C=2+4+1 C =1 + C =1 C =1 Jeu d ’instructions 2 registres : R0, R1 3 opérateurs : *,+,/ tlatence_op = 1 cycle (C[0], C[1], C[2]) (3,2,2) + (0,1,1) a S2 S1 (0,1,1) b c * (0,1,1) (5,4,4) / (3,2,2) (0,1,1) d Architecture de la machine ARCHI’07 - 176 E2 Rj = Ri op Rj Ri = Ri op Mj (8,8,7) C =1 E1 Hypothèses e (0,1,1)