MC-ENSL1 - Julien VILLEMEJANE

IUT Créteil-Vitry /GEII 2A /Projet /Sujet A

Dept GEII Année universitaire 2012-2013 - Durée : 4 x 3 heures

MC-ENSL1 J. VILLEMEJANE - [email protected]

Mise en oeuvre d’un microcontroleur simple

Objectifs

– Réaliser l’architecture d’un microcontroleur simple en VHDL.

Consignes

– Chaque module devra être réalisé dans un fichier séparé.

– Chaque module devra être validé par l’enseignant.

– L’ensemble des modules devra être fourni à la fin de la dernière séance à l’enseignant.

1. Architecture d’un microcontroleur

Les systèmes basés sur des microprocesseurs, tel que les microcontroleurs, pos-

sèdent les éléments suivants :

–Processeur

–Mémoires (Programme - ROM /Données - RAM)

–Entrée-Sorties

Afin de relier l’ensemble de ces éléments, différents bus sont indispensables : le bus de données, le bus

d’adresses et le décodeur d’adresse.

Le microprocesseur est composé : d’une Unité Arithmétique et Logique (UAL /ALU), de Registres,

d’un Contrôleur (registre d’instruction, décodeur d’instruction et séquenceur) et d’un Compteur programme.

Concernant l’architecture des microcontroleurs et le traitement des instructions, il vous est conseillé de

revoir votre cours de II2.

2. Séquenceur microprogrammé

2.1. Cahier des charges

On souhaite à présent réaliser un microprocesseur à jeu d’instruction très réduit (8 instructions) mais

relativement complet dans sa structure et pouvant traiter des données de 4 bits.

Le microprocesseur sera composé :

– d’une unité arithmétique et logique (addition, soustraction, logique booléenne)

– d’un registre interne A

– d’un contrôleur/séquenceur

– d’un compteur programme

Afin de pouvoir tester ce système sur la carte d’étude, nous rajouterons :

– une ROM programme

– des gestionnaires d’entrées/sorties

Le tout s’apparentera donc plutôt à un microcontrôleur.

IUT Créteil - GEII - MC-ENSL1 IUT Créteil-Vitry /GEII 2A /Projet /Sujet A

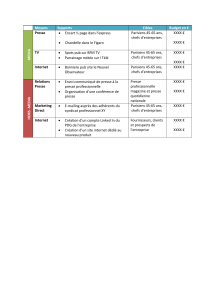

2.2. Le jeu d’instruction

Chaque instruction sera codée sur un mot de 8 bits (1 octet).

instruction adr Opérande

oc2 oc1 oc0 ad op3 op2 op1 op0

3 bits 1 bit 4 bits

Deux modes d’adressage seront possibles :

–littéral opérande fourni (cste) - ad =0

–direct adresse de l’opérande fourni (adr) - bit ad =1

Le jeu d’instruction sera le suivant :

Chargement LDA #cste 000 0XXXX Addition ADDA #cste 010 0XXXX

LDA $adr 000 1XXXX ADDA $adr 010 1XXXX

ET logique ANDA #cste 100 0XXXX Soustraction SUBA #cste 011 0XXXX

ANDA $adr 100 1XXXX SUBA $adr 011 1XXXX

Sauvegarde STA $adr 001 1XXXX Remise à zéro RST #cste 111 0XXXX

Décalage gauche ROLA #cste 101 0XXXX Décalage droite RORA #cste 110 0XXXX

3. Réalisation du microprocesseur

Le processeur sera réalisé à l’aide des différents blocs présentés dans le diagramme suivant.

3.1. L’accumulateur /le registre

Selon son instanciation, ce registre doit pouvoir mémoriser une donnée de 4 ou 8 bits présente en entrée

lors de la sélection du registre (entrée WR). Le registre doit être synchrone.

MODULE 1

1. Décrire un registre générique en VHDL (fichier registre.vhd).

2. Instancier un composant de ce type ayant 8 entrées, dans un système (fichier micropro.vhd).

3. Tester ce registre en attribuant les interrupteurs aux entrées et les leds aux sorties. L’horloge

sera réalisée avec un bouton-poussoir, ainsi que la validation de l’écriture.

–2–

IUT Créteil - GEII - MC-ENSL1 IUT Créteil-Vitry /GEII 2A /Projet /Sujet A

3.2. L’unité arithmétique et logique

Comme son nom l’indique, cet élément réalise des opérations arithmétiques (addition, soustraction...) et

logiques (et, ou...) entre deux données Aet B, ici chacune sur 4 bits.

Dans le cadre de notre application, l’ALU doit réaliser 5 opérations différentes. Pour pouvoir les différen-

cier, il est impératif de les coder, ici sur 3 bits : ADD =000 ; SUB =001 ; ROR =010 ; ROL =011 ; AND =

100.

MODULE 2

1. Décrire cette unité en VHDL (fichier alu.vhd).

2. Instancier ce composant dans le système précédent (fichier micropro.vhd).

3. Tester cette unité en attribuant 3 interrupteurs à l’entrée A, 3 à l’entrée B et 4 leds aux sorties.

Les deux derniers interrupteurs serviront comme sélection de la fonction à réaliser.

3.3. Le compteur programme

Le compteur programme contient l’adresse de la prochaine instruction à exécuter. Il ne doit pas être

incrémenté à chaque coup d’horloge mais seulement lorsque le contrôleur le lui ordonne (une instruction n’étant

pas exécutée en un seul coup d’horloge).

Il doit pouvoir être remis à zéro de façon asynchrone.

MODULE 3

1. Décrire ce compteur en VHDL (fichier cpt_pgm.vhd).

2. Instancier ce composant dans le système précédent (fichier micropro.vhd).

3. Tester cette unité en attribuant les leds aux sorties, un bouton-poussoir comme remise à zéro

et un bouton-poussoir comme validation de comptage.

3.4. Le contrôleur

Le contrôleur est l’organe principal du microprocesseur. C’est lui le chef d’orchestre du système. En

fonction des instructions qui se succèdent, il doit décoder les instructions, les opérandes, mettre en relation les

différents organes de traitement et enfin exécuter ces instructions.

Dans cet exemple, nous allons reprendre le cycle du PIC16F84 pour réaliser une machine à état de type

Moore. FETCH, DECODE, EXECUTE, WRITEBACK seront les 4 états possibles de cette machine qui se

succéderont.

Le décodage des sorties sera réalisé dans un second processus.

MODULE 4

1. Décrire le contrôleur en VHDL (fichier controleur.vhd) en le décomposant en 2 processus

concurrents : la machine à état (séquenceur) et le décodage des sorties en fonction :

– de l’état ;

– de l’instruction à exécuter.

2. Instancier ce composant dans le système précédent (fichier micropro.vhd).

3. Tester cette unité seule en attribuant :

– 7 leds aux différentes sorties (wr_accu,up... ) ;

– 4 switchs en entrée prog ;

– 1 bouton poussoir pour l’horloge clk ;

– 1 bouton poussoir pour la remise à zéro raz.

–3–

IUT Créteil - GEII - MC-ENSL1 IUT Créteil-Vitry /GEII 2A /Projet /Sujet A

On pourra aussi utiliser un décodeur 7 segments ainsi qu’un des afficheurs pour afficher le numéro de l’instruction décodée par

le contrôleur.

3.5. Le processeur

Maintenant que tous les composants ont été testés séparément, on peut les lier ensemble pour réaliser le

processeur.

MODULE 5

1. Instancier tous les composants nécessaires dans un système (fichier micropro.vhd). Vous

veillerez à créer les signaux internes nécessaires au bon fonctionnement.

2. Rajouter une sortie fct_out sur votre composant processeur, image de l’instruction à exécu-

ter.

3. Pour tester, ajouter un affichage multiplexé (voir TP 3).

4. Application autour du microprocesseur

Nous allons utiliser ce processeur dans le cadre d’une application simple mettant en jeu :

– une ROM (pour le programme) ;

– deux périphériques distincts.

4.1. Les périphériques

Notre système utilisera deux types de périphériques différents :

– un bloc d’affichage (2 x 4 Leds) ;

– un bloc d’entrée (2 x 4 interrupteurs).

Le bloc d’affichage écrit les données qu’il reçoit en entrée sur l’une de ces 2 adresses.

Le bloc d’entrée écrit sur sa sortie (4 bits) les données qu’il récupère sur l’un des deux sous-ensembles

d’interrupteurs.

Les deux blocs sont équipés d’une entrée de validation.

MODULE 6

1. Décrire ces deux blocs dans 2 fichiers séparés (periph_1.vhd et periph_2.vhd).

–4–

IUT Créteil - GEII - MC-ENSL1 IUT Créteil-Vitry /GEII 2A /Projet /Sujet A

4.2. Le décodage d’adresse

Le décodage des adresses d’entrées/sorties est indispensable pour éviter d’attribuer des données à des péri-

phériques non concernés.

MODULE 7

1. Décrire le décodeur d’adresse (decodeur.vhd).

4.3. Premier essai

Nous nous servirons du bloc d’interrupteurs pour entrer les données.

Les leds serviront de sortie du périphérique 1. Le périphérique d’entrée 2 se verra attribuer une valeur par

défaut. L’afficheur affichera d’une part l’instruction à décoder et d’autre part l’adresse programme.

MODULE 8

1. Instancier tous les composants nécessaires dans un fichier application.vhd.

2. Tester un programme quelconque et vérifier le bon fonctionnement de votre microcontrôleur.

On pourra par exemple tester la séquence suivante : LDA # 0101,STA $ 0000.

Que se passe-t-il dans ce cas ?

4.4. Mémoire programme

ENTITY rom IS

PORT( adresse : i n STD_LOGIC_VECTOR ( 3 DOWNTO 0 ) ;

data_out : out STD_LOGIC_VECTOR( 7 DOWNTO 0 ) ) ;

END rom ;

ARCHITECTURE simple OF rom IS

TYPE tableau IS array ( 0 TO 1 5) OF STD_LOGIC_VECTOR( 7 DOWNTO 0 ) ;

CONSTANT r om_ tab : t a b l e a u :=

(X" E0 " ,X" 12 " ,X" 30 " ,X" E0 " ,X" 00 " ,X" 00 " ,X" 00 " ,X" 00 " ,

X" 00 " ,X" 00 " ,X" 00 " ,X" 00 " ,X" 00 " ,X" 00 " ,X" 00 " ,X" 00 " ) ;

BEGIN

data_out <= rom_t ab ( t o _ i n t e g e r ( u n s i g n e d ( a d r e s s e ) ) ) ;

END simple ;

–5–

6

6

1

/

6

100%