Conception d`un convoyeur de courant CMOS à l

Conception d’un convoyeur de courant CMOS à l’aide de

l’algorithme NSGA-II

Abbas El Dor1, Patrick Siarry2

1Ecole des Mines de Nantes, TASC INRIA (CNRS UMR 6241),

4 rue Alfred Kastler, 44300 Nantes, FRANCE

2Université de Paris-Est Créteil

Laboratoire Images, Signaux et Systèmes Intelligents, LiSSi (E.A. 3956)

122 rue Paul Armangot, 94400 Vitry-sur-Seine, FRANCE

Mots-clés :optimisation, algorithme génétique, multiobjectif, convoyeur de courant, CMOS.

1 Introduction

Cet article porte sur une contribution relative à l’optimisation du dimensionnement d’un

circuit analogique, plus précisément à l’optimisation des caractéristiques importantes d’un

convoyeur de courant de seconde génération positif à boucle translinéaire CMOS. Le but est de

trouver les dimensions des transistors qui permettent au circuit d’avoir des performances opti-

males, suivant un critère donné. En d’autres termes, nous cherchons à déterminer les longueurs

et les largeurs des transistors qui permettent au circuit d’avoir des performances optimales,

suivant un critère donné. Ce problème peut être considéré comme un problème d’optimisation

multi-critères à variables continues soumis à des contraintes. Nous utilisons un algorithme gé-

nétique pour générer le front de Pareto en minimisant la résistance parasite RXet maximisant

la fréquence de coupure en courant fci. Des simulations effectuées sur SPICE 1mettent en relief

les résultats atteints.

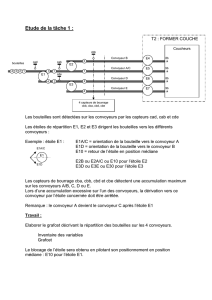

2 Convoyeur de courant de seconde génération

Les convoyeurs de courant (CCs, Current Conveyors) ont été introduits en 1970 [1]. Ces

convoyeurs constituent à ce jour l’élément le plus courant des circuits analogiques en mode

courant (CMCs, Current Mode Circuits). En effet, un convoyeur de courant (CC) est un dispo-

sitif électronique composé de trois ports actifs (X,Yet Z). Le convoyeur de courant de seconde

génération est le convoyeur le plus souvent utilisé, tant pour ses bonnes performances, que pour

l’intérêt apporté par l’utilisation d’une boucle translinéaire. La figure 1-(a) montre l’exemple

d’un convoyeur de courant de seconde génération positif à boucle translinéaire CMOS (CCII+).

La Figure 1-(b) montre les différents composants parasites d’un convoyeur de courant qui sont

souvent modélisés par trois impédances ZX, ZYet ZZet reliés aux ports correspondants. Ces

composants affectent de manière significative le comportement du circuit. Il a été prouvé que,

parmi ces éléments, ZXest le composant parasite dont les effets sont les plus importants sur le

comportement du convoyeur de courant. Plus précisément, c’est la résistance parasite RXdu

port X qui est la plus importante et qui affecte les performances de la façon la plus significative

du CC.

1. SPICE (Simulation Program with Integrated Circuit Emphasis) est un logiciel de simulation généraliste

de circuits électroniques analogiques.

to minimize is configured as

f

obj

¼

a

1

f

ci

þ

b

R

X

ð4Þ

For our system we could achieve satisfactory performance

with the first choice of parameters

a

¼

b

¼1. The suitable

expression of f

ci

is obtained for the system by employing a

symbolic analyzer [16] and the expression contains large number

of terms. Because of the presence of these large number of terms,

the explicit expression of f

ci

is not given here.

3. The bacterial foraging optimization (BFO) algorithm

According to foraging theory, the animals search for and obtain

nutrients in such a fashion that the energy intake per unit time is

maximized, so that the animals get enough nutrient sources to

survive and, at the same time, they can have spare time for other

activities [9]. Hence, it is well-known that those animals which

have poor foraging capability, get eliminated and those animals

which have strong foraging capability, have their genes propa-

gated for further reproduction procedure. An analog of this

foraging problem has been formulated as an optimization

problem by employing optimal foraging theory, to propose a

new evolutionary optimization algorithm [9,17,18]. The idea is to

biomimic the foraging behavior of a common type of bacteria,

E. coli, popularly known as E. Coli [18]. The movement of a E. Coli

bacterium in a three-dimensional space is usually characterized

by alternate phases of running and tumbling. The basic difference

C C

Z

X

YZ

X

Y

Z

X

Y

r=1ohm r=1ohm

Fig. 1. (a) General representation of current conveyor, (b) the nullor equivalency of an ideal CCII, and (c) the nullor equivalency of an ideal CCII+.

Cx

Rz

Cz

ZVz

Vx

Vy

real CC

Iz

Ix

Iy

Zz

X

Lx

Zx

Rx

Cy

Ry

Zy

Y

CC

ideal

Xi

Zi

Yi

Fig. 2. Equivalent model of a CC.

I0

M13

M10

M12

M9

M11

M8M7

M5M6

M1M2

M3M4

ZXY

VSS

VDD

Fig. 3. A conventional translinear loop based CMOS CCII+ [6].

Cx

Rz

Cz

ZVz

Vx

Vy

real CC

Iz

Ix

Iy

Zz

X

Lx

Zx

Rx

Cy

Ry

Zy

Y

CC

ideal

Xi

Zi

Yi

CC

idéal

CC réel

(a) (b)

FIG. 1 – (a) Convoyeur de courant de seconde génération positif (CCII+), et (b) Schéma équivalent

avec composants parasites.

L’utilisation de ce type de circuits nécessite leur optimisation pour pouvoir tirer un maximum

de profit de leurs performances, en particulier maximiser la fréquence de coupure en courant

fci et minimiser la résistance parasite RX.

3 Présentation de l’algorithme génétique

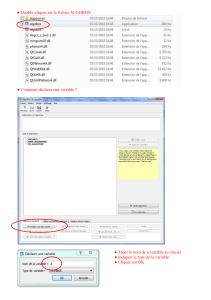

NSGA (Non-dominated Sorting Genetic Algorithm) est un algorithme génétique qui génère

le front de Pareto d’un problème d’optimisation multiobjectif. Il s’agit d’un algorithme très

efficace mais généralement critiqué pour sa complexité de calcul, le manque d’élitisme et le choix

de la valeur optimale du paramètre de la fonction de partage des performances (sharing : qui

a été utilisé pour maintenir la diversité).

Une version modifiée NSGA-II a été développée [2], cette modification présente une meilleure

procédure de tri de la population en la répartissant sur plusieurs fronts. Ainsi, dans cette

version, l’élitisme a été intégré et aucun paramètre de partage ne doit être choisi à priori. Dans

cet algorithme, les étapes principales sont : la création d’une population initiale, la sélection

de parents, les opérations de croisement et de mutation pour créer des enfants, et le choix des

meilleures solutions selon la dominance de Pareto. Toutes ces étapes sont répétées à chaque

génération. Il existe 4 paramètres à régler pour NSGA-II : la taille de la population, le nombre

de générations, la probabilité de croisement et la probabilité de mutation. Ces paramètres

déterminent la convergence de l’algorithme et aident à obtenir des résultats diversifiés.

4 Travaux en cours

Des résultats encourageants ont été obtenus en configurant le problème comme un problème

bi-objectif à minimiser. Notre travail continue en appliquant l’algorithme génétique NSGA-

II sur ce problème, dans son cas standard multiobjectif, afin de concevoir un convoyeur de

courant (CCII+) de manière optimale pour donner de meilleures performances. Cela revient

alors à trouver les positions de l’espace de recherche qui correspondent au front de Pareto.

Références

[1] A. Sedra and K. Smith. A second generation current conveyor and its applications. In IEEE

Transactions on Circuits Theory, Vol. 17, pp. 132-134, 1970.

[2] K. Deb, A. Pratap, S. Agarwal and T. Meyarivan. A Fast Elitist Multi-objective Genetic

Algorithm : NSGA-II. In IEEE Transactions on Evolutionary Computation, Vol. 6, N˚2,

pp. 182-197, 2002.

1

/

2

100%