Support systèm e des accès utilisateurs

Support système des accès utilisateurs STS SIO, 1ère année

Chapitre 3 : Les échanges au sein de la carte mère page 1

Support système des accès utilisateurs

SI

1

BTS Services Informatiques

aux Organisations

1ère année

Chapitre 3 :

Les échanges au sein

de la carte mère

Objectifs :

Comprendre les mécanismes d'échange au sein de la carte mère, entre la mémoire

centrale et le processeur et au sein du processeur.

Plan :

1. Les bus de données : des autoroutes sur la carte mère.

1.1. Les différents types de bus.

1.2. Le bus FSB.

1.3. Le bus HSB.

1.4. Le NorthBridge.

1.5. Le SouthBridge.

1.6. Évolution.

2. La mémoire centrale : la RAM.

2.1. Histoire de barrettes.

2.2. Les technologies des RAM.

2.3. Le marché de la barrette.

2.4. Le bon timing.

3. Les processeurs.

3.1. Processeur et fréquence.

3.2. Les instructions du processeur.

3.3. Les registres.

3.4. Unités fonctionnelles.

3.5. HyperThreading et multi-cœur.

Ressources :

Comment ca marche : Le processeur

Vulgarisation-informatique : La mémoire

Support système des accès utilisateurs STS SIO, 1ère année

Chapitre 3 : Les échanges au sein de la carte mère page 2

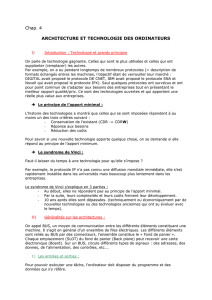

1. Les bus de données : des autoroutes sur la carte mère.

On appelle bus tout canal physique de communication entre plusieurs dispositifs. Ainsi, on trouve des bus

sur les cartes mères, mais également au sein du microprocesseur ou entre plusieurs ordinateurs.

1.1. Les différents types de bus.

Parmi les bus que l'on rencontre au sein d'un ordinateur, on trouve :

Le bus d'adresses (appelé parfois bus d'adressage ou bus mémoire) transporte les adresses mémoire

auxquelles le processeur souhaite accéder pour lire ou écrire une donnée.

Le bus de contrôle (parfois bus de commandes) transporte les ordres et les signaux de synchronisation

en provenance de l’unité de commande et à destination de l'ensemble des composants matériels. Il

s'agit d'un bus directionnel dans la mesure où il transmet également les signaux de réponse des

éléments matériels.

Le bus de données véhicule les informations en provenance ou à destination du processeur. Il s'agit

d'un bus bidirectionnel.

Les bus d'adresses et de contrôle sont internes au microprocesseur.

Les bus de données sont ceux qui permettent au microprocesseur de communiquer avec le reste des

composants de la carte mère.

Micro

-

Processeur

FSB

Cache

niveau 2

North

bridge

Bus AGP

Carte

graphique

RAM

South

bridge

ATA

ISA

Bus PCI Express

Cartes

d'extension

Stockage

de masse

SCSI

HSB

COM

LPT

USB

FireWire

Lecteurs

disquettes

Port

Réseau

Bus PCI

Support système des accès utilisateurs STS SIO, 1ère année

Chapitre 3 : Les échanges au sein de la carte mère page 3

1.2. Le bus FSB.

Le FSB ou Front Side Bus est appelé Bus processeur ou bus système. C'est celui qui entre et qui sort du

microprocesseur. Ce bus a une fréquence particulièrement élevée (jusqu'à 3,3 GHz).

Le bus de communication avec la mémoire cache L2 ou L3 est directement connecté (comme une

dérivation) sur le FSB. La mémoire cache est ainsi considérée comme intégrée au processeur tellement les

temps de réponse sont infimes.

C'est ensuite le northbridge qui gère les échanges avec les autres composants.

1.3. Le bus HSB.

Le HSB ou High Speed Bus, également appelé Bus Interne, est le bus qui relie le northbridge au

southbridge. Malgré son nom, il a des fréquence de fonctionnement moindre que le FSB.

1.4. Le NorthBridge.

Le northbridge a un rôle essentiel : gérer les flux d'échanges de données avec tous les éléments de la carte

mère, en privilégiant le bus RAM et le bus PCIExpress x16 (destiné à la carte graphique).

Le nom de northbridge est en voie d'être abandonné au profit de MCH pour Memory Controller Hub

1.5. Le SouthBridge.

Le southBridge permet de contrôle des bus éloignés comme ISA, PCI, ATA, SATA, PCI Express…

Le nom de southbridge est en voie d'être remplacé par ICH pour I/O Controller Hub.

1.6. Évolution.

Les nouvelles architectures tendent à faire disparaître le northbridge-MCH.

En effet, le contrôleur de RAM est intégré au processeur pour améliorer encore les échanges, comme c'est

le cas pour les processeurs i7 depuis la série 900.

Du coup, le bus FSB disparaît également, au profit du bus QPI (QuickPath Interconnect) chez Intel ou

HyperTransport chez AMD. Ceux-ci offrent de meilleurs temps de réponse, et une meilleure gestion des

échanges.

2. La mémoire centrale : la RAM.

2.1. Histoire de barrettes.

Les premières mémoires se présentaient sous la forme de puces appelées DIP

(Dual Inline Package).

Désormais les mémoires se trouvent généralement sous la forme de barrettes,

c'est-à-dire des cartes enfichables dans des connecteurs prévus à cet effet.

Support système des accès utilisateurs STS SIO, 1ère année

Chapitre 3 : Les échanges au sein de la carte mère page 4

On distingue deux types de barrettes de RAM : les barrettes au format SIMM (Single Inline Memory

Module) et les barrettes au format DIMM (Dual Inline Memory Module) : ce sont des circuits imprimés

possédant respectivement sur une ou deux faces des puces de mémoire.

Les barrettes au format SIMM (Single Inline Memory Module) ne

possèdent de puces de mémoire que sur un seul côté. Ce type de

barrettes a disparu avec l'apparition des premiers pentiums.

Les barrettes au format DIMM (Dual Inline Memory Module) sont

des mémoires 64 bits qui possèdent des puces de mémoire de part et

d'autre du circuit imprimé.

A noter que les connecteurs DIMM ont été améliorés afin de

permettre une insertion facile des barrettes grâce à des leviers situés

de part et d'autre du connecteur.

2.2. Les technologies des RAM.

La SDRAM (Synchronous DRAM, traduisez RAM dynamique synchrone), apparue en 1997, permet une

lecture des données synchronisée avec le bus de la carte-mère. La SDRAM est capable de fonctionner

avec une cadence allant jusqu'à 150Mhz, lui permettant d'obtenir des temps d'accès d'environ 10ns.

La DDR-SDRAM (Double Data Rate SDRAM) est une mémoire fondée sur

la technologie SDRAM, exploite simultanément deux canaux, permettant

ainsi de doubler le taux de transfert de la SDRAM à fréquence égale.

Apparue en 2000, elle s'est généralisée au détriment de la SDRAM. Elle a

également été commercialisée sous le nom de DDR ou DDR 1.

Puis les évolution technologiques ont permis de multiplier le nombre de

canaux d'échange des flux de données, pour donner en 2003 la DDR II avec 4

canaux et en 2007 la DDR III et ses 8 canaux.

Le déplacement du détrompeur permet de ne pas utiliser une barrette à la

place d'une d'une autre génération.

Support système des accès utilisateurs STS SIO, 1ère année

Chapitre 3 : Les échanges au sein de la carte mère page 5

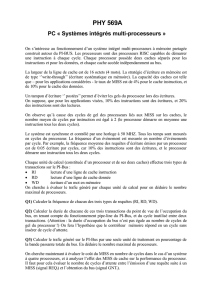

2.3. Le marché de la barrette.

Le nom commercial de ces barrettes commence par PC, suffixé de leur bande passante ou DDR suffixé de

la fréquence.

PC est suivi d'un 2 pour la DDR II et d'une 3 pour la DDR III.

Barrette Fréquence MHz Bande passante

maximale Nom commercial

du bus DDR Puce Barrette

DDR-SDRAM

DDR

DDR I

100 2x100 = 200 200 x 8 = 1600 Mio/s

PC 1600 DDR-200

… … … … …

200 400 3200 Mio/s PC 3200 DDR400

DDR II

QDR

100 2x200=400 400x8 = 3200 Mio/s PC2 4300 DDR2-400

… … …

300 1200 1200 x 8 = 9600

Mio/s

PC2 9600 DDR2-1200

DDR III

100 800 800 x 8 = 6400 Mio/s

PC3 6400 DDR3-800

… … … … …

375 3000 24000 Mio/s PC3 24000 DDR3-3000

Il n'y a pas de différence architecturale entre les différentes DDR SDRAM conçues pour les différentes

fréquences d'horloge, comme par exemple entre la PC3 6400 et la PC3 24000.

Le nombre indique simplement le niveau de fonctionnement garanti pour chaque type de mémoire.

Il est possible d'utiliser de la DDR SDRAM à une fréquence inférieure à celle prévue (sous-fréquençage)

ou supérieure (sur-fréquençage), ce qui n'est toutefois à tenter qu'avec des mémoires de haute qualité.

2.4. Le bon timing.

Les barrettes sont généralement accompagnées d'une notation du type 3-2-2-2 ou 7-7-7-19 pour décrire le

paramétrage de la mémoire vive. Cette suite de quatre nombres décrit la synchronisation de la mémoire

(en anglais timing), c'est-à-dire la succession de cycles d'horloge nécessaires pour accéder à une donnée

stockée en mémoire vive.

Lorsqu'on parle de timings mémoire on communique souvent les timings dans l'ordre suivant (même si ce

n'est pas indiqué) :

CAS ou CAS delay (column address strobe)

RAS to CAS

RAS precharge Time

RAS (row address strobe)

6

6

7

7

8

8

9

9

1

/

9

100%