corrigé Interro 2014/2015

Université Constantine 2 (MAHRI ABDELHAMID)

Faculté des nouvelles technologies

Département du Tronc commun Math-Informatique / Licence 1

15/11/2014

Matière : Electronique des composants et systèmes

Corrigé - Interrogation écrite

1pt-Q1 : Dans un système avec microprocesseur, pourquoi une architecture Harvard est-elle

avantageuse?

Le bus d’instruction et le bus de données indépendant de l’architecture Harvard permettent de lire

une instruction tout en exécutant une autre instruction qui écrit ou lit une donnée.

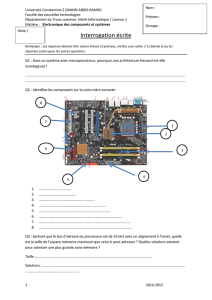

2pts-Q2 : Identifiez les composants sur la carte mère suivante :

1pt-Q3 : Sachant que le bus d’adresse du processeur est de 16 bits avec un alignement à l’octet, quelle est

la taille de l’espace mémoire maximum que celui-ci peut adresser ? Quelles solutions existent pour adresser

une plus grande zone mémoire ?

R3 : 216 = 65536 = 64 ko

Les solutions possible utiliser un système de pagination ou augmenter la taille du bus mémoire

1pt-Q4 : Le Facteur d'encombrement représente pour une carte mère :

Sa vitesse

Sa capacité à intégrer de nouveaux composants

Entre autres la géométrie et les dimensions de ses constituants

Les caractéristiques électriques de la carte mère

2 2014-2015

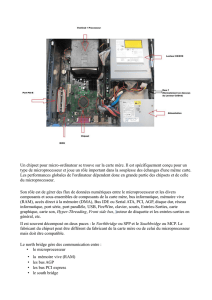

2pts- Q5 : Complétez le schéma du microprocesseur suivant :

0.25 pt-Q6 : Les composants de la carte mère sont orientés parallèlement pour

permettre une meilleure évacuation de la chaleur

une économie d’espace de la carte

pour les deux raisons

1pt-Q7 : Le chipset est composé par deux éléments : Pont Nord et Pont Sud. Le pont Nord et le pont

Sud ont le même rôle du faite qu’ils permettent d’interfacer le microprocesseur avec les

périphériques.

Oui Non pour quoi ?

North bridge : s’occupe d’interfacer le microprocesseur avec les périphériques rapides (mémoire

et carte graphique) nécessitant une bande passante élevée.

South bridge : s’occupe d’interfacer le microprocesseur avec les périphériques plus lents (disque

dur, CDROM, lecteur de disquette, réseau, etc…).

0.5pt-Q8 : L'horloge temps réel ( RTC) est un circuit chargé de régler l’heure du système.

Oui Non

1pt-Q9 : le BIOS et le CMOS sont complémentaires pour lancer le système.

Le CMOS est une mémoire qui contient le BIOS

Le BIOS est une mémoire qui contient le CMOS

Le CMOS et le BIOS sont tous les deux des mémoires

Autres propositions :

Le BIOS est un programme responsable de la gestion du matériel. Il utilise les données contenues

dans le CMOS pour connaître la configuration matérielle du système

1.25pt-Q10 : Classez par ordre décroissant (plus grand au plus petit) de fréquence des bus suivants :

Bus IDE, Bus AGP, Bus Mémoire, Bus PCI, Bus Processeur, Bus SCSI.

Ordre

Bus

Indication de la fréquence ou

taux de transfert (selon cours)

1

Bus Processeur

66-200 Mhz

2

Bus Mémoire

66-200 Mhz

3

Bus AGP

66 Mhz x1,x2,x4,x8

Mémoire

cache

Bus de commandes

3 2014-2015

0.75pt-Q11 : Les bus « internes » (PCI, IDE, AGP) vont être amenés à disparaître très rapidement et

seront remplacés par des bus S-ATA et Le PCI Express. Ses deux bus sont de type Série.

Le bus Serial ATA, remplacera le bus IDE, présentera des débits encore plus élevé. Il permettra de

connecter des disques durs ou des lecteurs optiques

Le PCI Express, remplacera les bus PCI et AGP

1.25pt-Q12 : A quoi servent les registres suivants :

1. le registre accumulateur (ACC), stockant les résultats des opérations arithmétiques et

logiques ;

2. le registre d'état (PSW, Processor Status Word), permettant de stocker des indicateurs sur

l'état du système (retenue, dépassement, etc.) ;

3. le registre instruction (RI), contenant l'instruction en cours de traitement ;

4. le compteur ordinal (CO ou PC pour Program Counter), contenant l'adresse de la prochaine

instruction à traiter ;

5. le registre tampon, stockant temporairement une donnée provenant de la mémoire.

1.5pts-Q13 : A quoi servent les mémoires caches et combien de niveaux sont-elles ?

La mémoire cache (également appelée antémémoire ou mémoire tampon) est une mémoire

rapide permettant de réduire les délais d'attente des informations stockées en mémoire vive.

Elles sont de troix (03) niveaux.

0.5pt-Q14 : Les mémoires caches se situent dans :

Le processeur

La carte mère

La puce du microprocesseur

4

Bus IDE

100-133 Mo/s

5

Bus PCI

33-133 Mhz

6

Bus SCSI

40-80 Mhz

1

/

3

100%