Projet de TDO Mémoires FLASH et bus de données Etude et

Projet de TDO

Mémoires FLASH et bus de données

Etude et comparaison

Sophie Sivignon

Florent Castelli

Groupe 2

Mars 2005

2

Introduction

Actuellement, sans forcément le savoir, nous sommes tous entourés par ce qui est une des

dernières révolutions technologiques. Cette révolution a ouvert de nombreuses portes et

énormément réduit les coups de fabrication. Celle-ci est la mémoire Flash. La mémoire Flash

se retrouve partout : ordinateurs, mémoires pour appareils photos, clés USB, cartes contrôleur

ou d’extension et bien d’autres applications. Cette mémoire si répandue de nos jours dépend

du périphérique sur lequel elle est connectée. Et ce périphérique communique avec d’autres et

échange des informations ; cela se fait par l’intermédiaire d’un bus de données. Tout le monde

connaît au moins l’USB. Mais il en existe d’autres qui ont chacun leurs avantages et nous

allons en étudier quelques uns dans ce rapport.

Nous verrons donc une explication sur le fonctionnement des mémoires Flash. Ensuite nous

nous intéresserons au fonctionnement du bus SPI et Microwire. Nous verrons en détail le bus

I²C et enfin une comparaison entre ces déférents bus.

Introduction _______________________________________________________________ 2

I – Mémoires Flash _________________________________________________________ 3

II – Bus de données _________________________________________________________ 5

1) SPI ______________________________________________________________________ 5

2) Microwire ________________________________________________________________ 6

3) I²C ______________________________________________________________________ 7

Présentation _________________________________________________________________________ 7

Protocole ___________________________________________________________________________ 7

Driver______________________________________________________________________________ 8

4) Comparaison______________________________________________________________ 8

Conclusion _______________________________________________________________ 10

Annexe __________________________________________________________________ 11

Driver I²C pour 6502 __________________________________________________________ 11

3

I – Mémoires Flash

La mémoire flash est une mémoire à semi-conducteurs, non volatile et réinscriptible, c'est-à-

dire une mémoire possédant les caractéristiques d'une mémoire vive mais dont les données ne

disparaissent pas lors d'une mise hors tension (mémoire de masse). Ainsi, la mémoire flash

stocke les bits de données dans des cellules de mémoire, mais les données sont conservées en

mémoire lorsque l'alimentation électrique est coupée.

En dépit de sa relative lenteur, la durée de vie et la consommation faible (et même nulle au

repos) de la mémoire flash la rendent utile pour de nombreuses applications : appareils photo

numériques, téléphones cellulaires, assistants personnels (PDA), ordinateurs portables ou

dispositifs de lecture et d'enregistrement sonore comme les baladeurs MP3, clef USB. De

plus, ce type de mémoire ne possède pas d'éléments mécaniques, ce qui lui confère une assez

grande résistance aux chocs.

La mémoire flash est un type d'EEPROM (Electrically Erasable Programmable ReadOnly

Memory) qui permet la modification de plusieurs espaces mémoires en une seule opération.

La mémoire flash est donc plus rapide lorsque le système doit écrire à plusieurs endroits en

même temps.

Elle existe sous deux formes: flash NOR et NAND, d'après le type de pont logique utilisé

pour chaque cellule de stockage.

La mémoire flash NOR est la première à être développée par Atmel. Les temps d'effacement

et d'écriture sont longs mais elle possède une interface d'adressage permettant un accès

aléatoire à n'importe quelle position. Elle est adaptée à l'enregistrement de programmes

informatiques qui sont rarement mis à jour, comme dans les appareils photo numériques ou

les organisateurs personnels. Elle peut supporter de 10 000 à 100 000 cycles d'effacement.

La mémoire flash NAND fut développée par Toshiba. Elle est plus rapide à l'effacement et à

l'écriture, offre une plus grande densité, un coût moins important par bit et une durée de vie

dix fois plus importante. Toutefois son interface d'entrée / sortie n'autorise que l'accès

séquentiel aux données. Elle est donc utilisée pour le stockage d'informations et est moins

utile en tant que mémoire pour ordinateurs.

Dans la mémoire flash NOR, chaque cellule de mémoire est similaire à un transistor standard

MOSFET, excepté qu'il y a deux portes au lieu d'une. Une des deux portes est le CG (Control

Gate) comme dans les autres transistors MOS et la seconde est la FG (Floating Gate) qui est

isolée par une couche d'oxyde. Ainsi les électrons, passant au dessus, se retrouvent

emprisonnés et stockent l'information.

Lorsque les électrons sont sur la FG, ils modifient partiellement le champ magnétique venant

du CG qui modifie la tension de la cellule. De ce fait, lorsque la cellule «est lue» une tension

spécifique est placée sur le CG, le courant électrique passe ou ne passe pas selon la tension de

la cellule qui est, elle, commandée par le nombre d'électrons stockés sur le FG. La présence

ou l'absence de courant électrique est traduite par des 0 et des 1, reproduisant ainsi les

données stockées.

Dans un dispositif à plusieurs niveaux de cellules, qui stocke plus de 1 bit de données par

cellule, connaître le flux de passage du courant électrique plutôt que simplement sa présence

ou son absence permet de mieux déterminer le nombre d'électrons stockés sur le FG.

4

Une NOR flash cellule est programmée en utilisant un processus appelé hot-electron injection

qui consiste à placer un haut voltage sur le CG pour obtenir un champ électrique assez fort

pour déplacer le flux d'électrons d'un pôle à un autre. La plupart des composants des

mémoires flash NOR modernes sont divisés en segments effaçables appelés blocs ou secteurs.

Toutes les cellules mémoires d'un bloc doivent être effacées en même temps.

La programmation NOR peut généralement être exécutée à un octet ou mot à la fois.

En ce qui concerne la NAND flash, elle utilise le procédé de tunnel injection pour l'écriture et

le tunnel release pour l'effacement.

5

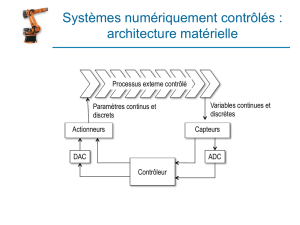

II – Bus de données

1) SPI

Le « Serial Peripheral Interface Bus » ou bus SPI de Motorola est un standard de contrôle

adapté à presque tous les équipements électroniques qui acceptent un flux de bits en série et

avec une horloge.

SPI est très peu cher car il utilise très peu de fils et donc moins de place sur un circuit intégré

et il ne multiplie donc pas les broches sur les composants. On peut aussi l’implémenter en

software avec peu de pattes d’entrée / sortie d’un microcontrôleur.

Le bus SPI est capable de travailler en duplex et il est donc un très bon choix pour des

systèmes de transmission de données.

Le bus SPI n’a besoin que de 4 fils sur chaque circuit intégré :

- une horloge (SCLK)

- une entrée « Master Data Out / Slave Data Input » (MOSI)

- une sortie « Master Data Input / Slave Data Output » (MISO)

- un « chip select » aussi appelé « slave select » (SS).

Organisation Maître / Esclave du bus SPI 1

Dans le cas général, les données arrivent dans le périphérique quand l’horloge est basse et

sortent quand l’horloge est haute. Un périphérique pour communiquer doit avoir le chip-select

bas. Dans le cas contraire, la plupart des périphériques ont leur sortie avec une haute

impédance (désactivée). Tout cela permet à de nombreux appareils de communiquer avec un

écouteur unique. La fréquence de l’horloge peut varier de quelques kHz à quelques MHz.

Quand il y a plusieurs périphériques esclaves, le périphérique maître possède plusieurs SS et

doit donc n’en activer qu’un seul à la fois.

Organisation Maître / Esclave du bus SPI 2

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

1

/

14

100%