Système multiprocesseur intégrés sur puce

Alain Greiner

PHY 568

Systèmes multi-processeurs

Systèmes multi-processeurs

intégrés sur puce

intégrés sur puce

version 1.0

2

PHY 568 Alain Greiner

Pla

Pla

n

n

Architectures multi-processeurs à mémoire partagée

Applications parallèles embarquées

Bus système / exemple du PIBUS

3

PHY 568 Alain Greiner

Bu

Bu

t

t

Un système multiprocesseurs intégré sur puce (MPSoC),

cherche à exploiter le parallélisme « gros grain » d’une

unique application embarquée.

Exemple : contrôle d’un téléphone portable

Une même puce contient plusieurs processeurs exécutant

en parallèle différentes tâches.

Ces tâches communiquent généralement entre elles à

travers un espace d’adressage partagé, suivant un schéma

producteur/consommateur.

4

PHY 568 Alain Greiner

Espace d’adressage

Espace d’adressage

partagé

partagé

P0 P1 P2 P3

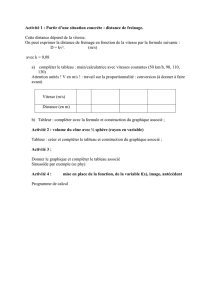

Les maîtres (ou initiateurs) démarrent une transaction en effectuant une

lecture ou une écriture à une adresse particulière.

Les esclaves (ou cibles) terminent la transaction en renvoyant la

donnée demandée (lecture), ou en renvoyant un acquittement (écriture)

Une transaction est un couple (commande / réponse).

RAM ROM TTY I/O

Maîtres

Esclaves

Interconnect

5

PHY 568 Alain Greiner

Décodage des

Décodage des

adresses

adresses

Tous les composants du système

ont la même vision de l’implantation

des cibles dans l’espace d’adressage.

L’interconnect décode les bits de poids

fort de l’adresse pour pour acheminer

la commande vers la cible concernée.

31 0

La cible décode les poids faible de l’adresse

pour adresser la case mémoire visée,

en lecture ou en écriture.

MSB LSB

FFFF FFFF

0000 0000

ROM

TTY

RAM

I/O

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

1

/

20

100%