Cours 4 : Circuits combinatoires Cours 4 : Circuits combinatoires

1

qAdditionneurs

– Demi additionneur : 2 entrées sur 1 bits àUne sortie sur 2 bits

– Additionneur complet : 3 entrées sur 1 bits àUne sortie sur 2 bits

– Additionneur sur n bits

qDécodeurs / Codeurs

– Décodeurs : adresse sur 2 bits à4 sorties dont une seule est active

– Circuit constructeur avec port d’entrée de validation et sortie active L

– Cascade de plusieurs circuits ==> décodeur d ’@ sur 4 bits à16 sorties (1 seule active)

– Codeur : Opération inverse d’un décodeur

qMux ou multiplexeur / Demultiplexeur

– Mux : Mettre en relation une entrée parmi n avec la sortie

– Demux : Mettre en relation une entrée avec une sortie prise parmi N

qComparateur

– Sortie VRAI ou FAUX indiquant la comparaison des entrées

qAfficheur 7 segments

qCircuits programmables

Cours 4 : Circuits combinatoires

Cours 4 : Circuits combinatoires

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

2

Sum = A ⊕B

A

0

0

1

1

B

0

1

0

1

Sum

0

1

1

0

Carry

0

0

0

1Carry = A . B

Additionneurs Elémentaires

Additionneurs Elémentaires

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

Cin

0

1

0

1

0

1

0

1

S

0

1

1

0

1

0

0

1

Cout

0

0

0

1

0

1

1

1

A B

Cin

0

1

00 01 11 10

0

0

0

1

0

1

1

1

Cout = B.Cin + A.Cin + A.B

A B

Cin

0

1

00 01 11 10

0

1

1

0

1

0

0

1

DEMI-ADDITIONNEUR

ADDITIONNEUR Complet

Carry

A

B

Sum

S

A

B

Cin

Cout

S = Cin ⊕A⊕B

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

3

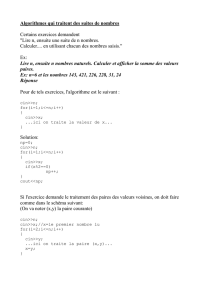

Additionneur sur n bits

Additionneur sur n bits

Mécanisme d ’addition en partant

des poids faibles et en propageant

la retenue vers les poids forts

Exemple additionneur sur 5 bits

S

A

B

Cin

Cout Cout

S

B

A

Cin

Cout

S

B

A

Cin

Cout

S

B

A

Cin

Cout

S

B

A

Cin

Cout

S

B

A

Cin

Cout

S

B

A

Cin

S1

S2

S3

S4

So

Co

Bo

Ao B1

A1B2

A2B3

A3B4

A4C5

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

4

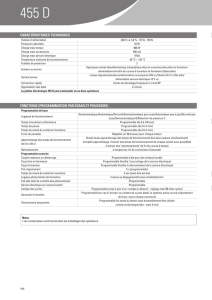

Décodeur n à2n

Décodeur n à2n

• Décodeur n à2n

Un décodeur est un circuit à n

entrées et 2nsorties dont une

seule est active à la fois.

• Décodeur 2 à4 sorties

actives à l’état haut

• Equations

Yo= !B.!A

Y1= !A.B

Y2= A.!B

Y3= A.B

Circuit constructeur

• Enable G

• Sorties active L

• Table de vérité

A

0

0

1

1

B

0

1

0

1

Yo

1

0

0

0

Y1

0

1

0

0

Y2

0

0

1

0

Y1

0

0

0

1

A B Y1Y2Y3

G

X X H H H HH

L L LH H HL

L H H LH HL

H L H H LHL

H H H H H LL

Yo

Yo

Y1

Y2

Y3

A

B

G

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

5

Cascade de plusieurs circuits

Cascade de plusieurs circuits

Décodeur 4 à16 sorties

décodeur d ’@ sur 4 bits à16 sorties

(1 seule active)

Circuit constructeur

• Enable G

• Sorties active L

La cascade de plusieurs circuits

est possible grâce à l ’entrée de

validation G

Y1

Y2

Y3

A

B

G

Y0

Y1

Y2

Y3

A

B

G

Y0

Y1

Y2

Y3

A

B

G

Y0

Y1

Y2

Y3

A

B

G

Y0

Y1

Y2

Y3

A

B

G

Y0

G

@3

@2

@1

@0

Y1

Y2

Y3

Y0

Y5

Y6

Y7

Y4

Y9

Y10

Y11

Y8

Y13

Y14

Y15

Y12

PDF Creator - PDF4Free v2.0 http://www.pdf4free.com

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

1

/

16

100%