Ensimag 2A

Ensimag 2A

Ensimag 2A

Examen d’Architecture Avancée

Filières SLE/ISI, 3 heures, tous documents et calculette autorisés.

Lisez l’ensemble des questions relatives à un exercice avant de commencer à répondre !

1 Exercice 1 : Cache assurant la cohérence mémoire (8pts)

Soit pprocesseurs connectés chacun par un PI-Bus à la mémoire centrale partagée, par l’intermédiaire d’un

cache. Les caches sont tous identiques, à correspondance directe (direct mapping), à écriture systématique (write

through), structurés en 128 lignes de 4 mots de 32 bits. On fait également l’hypothèse que les seuls transferts qui

ont lieu sont des lectures ou des écritures de mots de 32 bits.

Rappels et préliminaires

On rappelle ici les signaux du PI-Bus :

Nom emis reçu commentaires

RESETN environnement tous remise à zéro.

CLK environnement tous horloge système, active sur front montant.

REQxmaître xBCU Requête du maître xpour le bus.

GNTxBCU maître xDonne le bus au maître x.

READ maître esclave Lecture si 1, écriture si 0.

LOCK maître BCU Garde la propriété du bus.

OPC[3 :0] maître esclave, BCU Type de transfert.

A[31 :2] maître esclave, BCU Adresse du transfert.

D[31 :0] maître, esclave esclave, maître Donnée.

ACK[2 :0] esclave, BCU maître Réponse au transfert.

SELyBCU esclave ySélection de l’esclave y.

Les signaux sont tous actifs à l’état haut, hormis le RESETN qui est actif à l’état bas. Nous rappelons que les

adresses sont sur 30 bits, les 2 bits de poids faibles étant définis par les opcodes spécifiant le transfert, et que les

octets significatifs sont alignés à droite. Les signaux READ,OPC,LOCK et Asont positionnés au cycle t, et les

signaux ACK et Dsont positionnés au cycle t+ 1.

Le signal ACK peut prendre les valeurs suivantes :

symbole description

WAT transfert retardé.

RDY transfert effectué.

Le signal OPC ne peut prendre que la valeur WDU dans notre exercice (uniquement transferts de mots de 32

bits).

Un exemple de chronogramme est donné dans la figure 1.

La mémoire utilisée pour implanter le cache est une mémoire simple accès, les lectures et les écritures ne peuvent

donc avoir lieu au même cycle.

L’interface du processeur vers le cache de données dont nous avons l’usage est la suivante :

–TYPE. Émis par le processeur, indiquant le type de transfert à effectuer. Dans un but de simplification, seules 3

valeurs sont possibles : NOP (pas de requête), RWD (requête de lecture d’un mot), WWD (requête de d’écriture

d’un mot).

Examen d’architecture - 2S page - 1

Ensimag 2A

A0 A2 A3

WDU WDU WDU WDU

D2

CLK

REQA

GNTA*

RDYWAT

1 2 3 4 5 6 7CYCLE

SEL*

LOCK

A1 A3

D0 D1 D3

READ

OPC

A

D

WDU

RDY RDY RDY

ACK

SNOOPDO

FIGURE 1 – Chronogramme d’écritures successives en mémoire.

REQ

REQ<=1

A0

REQ<=1

GNT

FRZ<=1

FRZ<=1

A1D0

REQ<=0

FRZ<=1

GNT

IDLE

REQ<=0

A2D1

REQ<=0

A3D2

REQ<=0

D3

REQ<=0

LOCK<=1

LOCK<=1 LOCK<=1

LOCK<=1

LOCK<=0

RWRD.HIT/FRZ<=1

ACK=WAT/FRZ<=1

ACK=RDY/FRZ<=1

ACK=WAT/FRZ<=1

ACK=WAT/FRZ<=1

ACK=WAT/FRZ<=1

ACK=RDY/FRZ<=1

ACK=RDY/FRZ<=1

ACK=RDY/FRZ<=0

WWRD...../FRZ<=? Non considéré dans

cet exercice

RWRD.HIT/FRZ<=0

NOP/FRZ<=0

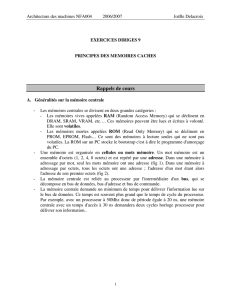

FIGURE 2 – Automate de chargement d’une

ligne de cache (sans la génération des sor-

ties).

–ADR[31 :0]. Émis par le processeur, contenant l’adresse de la requête courante. Pour notre exercice ADR[1 :0]

= 00 ;

–FRZ. Reçu par le processeur. Si ce signal vaut 1, le processeur est gelé (combinatoirement, c.-à-d. que si DFRZ

passe à 1 dans un cycle, les registres du processeur ne sont pas modifiés à la fin du cycle).

Exercice proprement dit

On se propose dans cet exercice de concevoir un mécanisme implanté dans le cache qui espionne les transferts de

données en écriture et invalide la ligne de cache si une écriture a lieu à une adresse correspondant à une donnée

qui se trouve dans le cache.

On doit pour se faire ajouter un signal supplémentaire, SNOOPDO, émis par le contrôleur de bus à destination

des maîtres, qui est à 1la première fois qu’une adresse est émise sur le bus par un maître. On voit sur le

chronogramme de la figure 1 que le signal SNOOPDO est à 1chaque fois qu’une nouvelle adresse est présentée

sur le bus, mais qu’en cas de ACK=WAT, qui implique que le maître remet l’adresse suivante, le signal n’est pas

réactivé.

Question 1 (0.5pt)

Donnez la « structure » de l’adresse pour ce cache, c’est-à-dire le nombre de bits de tag, d’index et d’offset.

128 lignes d’ou 7 bits d’index, lignes de 4 mots, donc 2 bits d’offset, 2 bits pour l’octet dans le mot, et donc

32 - (7+2+2) = 21 bits de tags.

Question 2 (1pt)

Du point de vue du protocole de bus (et indépendamment du comportement attendu du cache qui sera l’objet de la

suite), qu’est-il absolument nécessaire de faire au niveau des caches lorsque le signal SNOOPDO est à 1? Dessinez le

petit circuit permettant de faire cette action. (Il n’y a pas de piège, la réponse est simple.)

Examen d’architecture - 2S page - 2

Ensimag 2A

Échantillonner l’adresse !

Un registre avec @ sur data et snoopdo sur we

On change la sémantique du signal HIT. Ce signal indique à présent soit que la donnée requise par le processeur

est cachée, soit qu’il y a un hit externe, c’est à dire que la donnée écrite circulant sur le bus se trouve dans le

cache.

Question 3 (1pt)

Proposez une solution à faible coût matériel (typiquement sans dupliquer des choses existantes) permettant de calculer

ce signal. Faites le schéma de la partie opérative correspondante, sachant que le contrôle sera déterminé dans les 2

questions suivantes.

Un mux sur les fils d’adresse représentant le tag multiplexant soit l’adresse venant du processeur, soit

celle venant du bus. Le signal de hit correspond alors soit à un hit interne, soit à un hit externe. On utilis-

era le signal SNOOPDO pour commander le mux, qui s’il est actif fera passer l’adresse du bus qui a été

échantillonnée, et l’adresse du processeur sinon.

Question 4 (1pt)

En considérant les instants d’arrivée possibles des requêtes de lecture du processeur et des requêtes d’écriture circulant

sur le bus, décrivez le problème qui se pose sur le cache et proposez une solution qui garantisse un fonctionnement

correct. (On notera ici que le cache n’est pas maître des transferts qui ont lieu sur le bus, et qu’il ne peut intervenir sur

ceux-ci). Vous pouvez vous aider d’une table énumérant les 4 situations possibles pour expliquer votre raisonnement.

Requête de lecture du processeur et requête d’écriture circulant sur le bus :

Proc Bus Problème ?

0 0 Pas de problème

1 0 Pas de problème

0 1 Pas de problème

1 1 Geler le processeur et donner la priorité au bus

Le chargement d’une ligne de cache pour un système mono-processeur se passe comme indiqué grossièrement

(on n’indique pas ici les sorties de l’automate pilotant le chemin de données) par l’automate de la figure 2, déjà

vu en cours.

On veut à présent prendre en compte le signal SNOOPDO dans les transitions de l’automate.

Question 5 (2pt)

– à quelle condition y a-t-il un hit externe ? Donnez l’équation logique permettant de la calculer.

– dans quels états de l’automate est-on certain de ne jamais avoir de hit externe ? Justifiez votre réponse.

xhit = hit.snoopdo d’après ce qui a été dit avant

Dans les états durant lequel le processeur est propriétaire du bus : A0, A1D0, A2D1, A3D2, D3

On fera l’hypothèse que l’on va dans un état INVAL pour invalider la ligne visée (écriture d’un 0 dans le bit de

validité).

Question 6 (2.5pt)

Ajoutez un ou des états INVAL là où cela est nécessaire dans l’automate. Modifiez les conditions de transitions des

états qui peuvent être sensibles à un hit externe pour prendre en compte le signal SNOOPDO et passer ainsi dans cet

état. Donnez également les transitions permettant de sortir de l’état INVAL.

Examen d’architecture - 2S page - 3

Ensimag 2A

REQ

REQ<=1

A0

REQ<=1

GNT

FRZ<=1

FRZ<=1

A1D0

REQ<=0

FRZ<=1

GNT

IDLE

REQ<=0

A2D1

REQ<=0

A3D2

REQ<=0

D3

REQ<=0

LOCK<=1

LOCK<=1 LOCK<=1

LOCK<=1

LOCK<=0

ACK=WAT/FRZ<=1

ACK=RDY/FRZ<=1

ACK=WAT/FRZ<=1

ACK=WAT/FRZ<=1

ACK=WAT/FRZ<=1

ACK=RDY/FRZ<=1

ACK=RDY/FRZ<=1

ACK=RDY/FRZ<=0

SNOOPDO.WWRD...../FRZ<=?

SNOOPDO.RWRD.HIT/FRZ<=0

Non considéré dans

cet exercice

SNOOPDO.NOP/FRZ<=0

SNOOPDO.HIT/FRZ<=1

SNOOPDO.HIT/FRZ<=1

INVAL

WE <= 1

mux <= inval

SNOOPDO.HIT/FRZ<=1

1/FRZ<=0

SNOOPDO.

RWRD.HIT/FRZ<=1

Question bonus : inutile de s’y attaquer si vous n’avez pas fini le reste !

Au lieu d’invalider la ligne, on désire la mettre à jour, ce qui nécessite 2 états : UPDTR pour lire la ligne et UPDTW

pour la ré-écrire modifiée dans le cache, comme vu en cours.

Question 7 (bonus 1pt)

Quel est le problème si un hit externe à lieu (sur une autre ligne) lorsque l’automate est dans l’un de ces 2 états ?

Quelle est alors la seule solution pour assurer la cohérence des données ?

On est en train d’invalider une ligne à cause d’un précédent accès à une adresse dans le cache, et une

autre adresse est en train de circuler en écriture et on ne peut la prendre en compte, il y a donc risque

d’incohérence. La seule solution est alors d’invalider la totalité du cache car on ne sait pas quelle ligne

invalider

2 Exercice 2 : Analyse quantitative (2,5pts)

Soit les hypothèses suivantes :

– un processeur exécute une instruction RISC par cycle, et lit ou écrit une donnée en 1 cycle si elle est dans le

cache (cas hit). Les instructions sont supposées être dans un cache parfait, et n’interviennent donc pas dans les

calculs qui suivent. On prend comme hypothèse que si les accès mémoire donnée se faisaient en 1 cycle, le CPI

de la machine serait de 1 ;

– la latence de chargement d’une ligne de cache à partir de la mémoire est de l= 50 cycles ;

– pour une application donnée, le pourcentage d’instructions de lecture est de 20%, que nous notons r= 0.20,

et le pourcentage wd’instruction d’écriture est 12%, que nous noterons w= 0.12 ;

– le cache de données est write-back ; dans le cas où un accès mémoire fait miss, il faut dans 27% des cas (dirty

rate dr = 0.27) écrire la ligne en mémoire (ligne modifiée, dirty) avant de rapatrier la ligne désirée (stratégie

write allocate pour les écritures)

– les écritures font hit dans le cache dans 65% des cas : dwh = 0.65. Les écritures qui font miss sont synchro-

nisées : on attend la disponibilité de la ligne en cache pour faire effectivement l’écriture avant de passer à

l’instruction suivante ;

– le taux de miss en lecture drm est de 8% (drm = 0.08) pour le cache de données

Question 8 (2pt)

Examen d’architecture - 2S page - 4

Ensimag 2A

Donnez la formule générale du CPI(l, r, w, dwh, drm, dr)dans ces conditions, en supposant que le CPI avec un

cache parfait serait de 1. Faites l’application numérique avec les valeurs fournies.

CPI = ((1−(r+w))×1+r×(drm×l+(1−drm)×1)+w×(dwh×1+(1−dwh)×(2×l×dr +l×(1−dr))))

On multiplie par 2 la taille du cache des données, ce qui fait que les miss rates diminuent, dwh = 0.75 et

drm = 0.06, mais que le dirty rate en écriture augmente, donc dr = 0.42. En contrepartie, la fréquence de

fonctionnement du deuxième système est légèrement plus basse que celle du premier : fs2 = 0.985 ×fs1.

Question 9 (0,5pt)

Est-il utile de faire ce changement ? Justifiez votre réponse.

L’application numérique, que je n’ai pas faite, le dira !

3 Exercice 3 : Opérations atomiques (1pt)

Soit les instructions ll rt, imm(rs) et sc rt, imm(rs) vues en cours. On rappelle que si sc échoue, après

l’exécution de cette instruction le registre rt vaut 0, et sinon il vaut 1. On suppose que le registre $2 contient

l’adresse d’une case mémoire.

Question 10 (1pt)

Écrivez un programme qui incrémente le contenu de cette case mémoire de manière atomique à l’aide de ces instruc-

tions.

C’est très simple, juste pour voir s’ils sont venus en cours.

4 Exercice 4 : Processeur pipe-line à 8 étages (8,5pts)

Le successeur du processeur R3000 vu en cours est le R4000. Ce processeur, utilisé par exemple dans la play-

station portable, possède un pipe-line à 8 étages : l’analyse de la solution classique à 5 étages montrait que les

étages critiques (ceux déterminant la période d’horloge) étaient les étages d’accès mémoire, qu’il s’agisse de la

mémoire instruction ou de la mémoire donnée. En effet, si ces mémoires sont des caches à gestion complexe (taille

importante, associativité importante, accès TLB pour traduction adresses logiques vers adresses physiques, . . . ),

les accès, même en cas de « hit », sont 3 fois plus lents que les opérateurs des autres étages du pipe-line.

On décide donc d’effectuer les accès mémoire en 3 étapes :

1. préparation de l’accès (étages Instruction First et Data First) ;

2. accès effectif, (étages Instruction Second et Data Second). C’est dans ces étages qu’une instruction est

effectivement lue, et que les données sont effectivement lues ou écrites ;

3. vérification du hit/miss (étages Register File et Tag Check). Le circuit "Calcul Hit" calcule combinatoirement

si l’instruction dans le registre IS/RF ou la donnée dans le registre DS/TC est valide en cas de lecture, et si

la donnée a fait un « hit » dans le cache en cas d’écriture. On rappelle qu’un hit (encore appelé « miss »)

peut servir à geler le processeur, . . .

Examen d’architecture - 2S page - 5

6

6

7

7

1

/

7

100%