atmel atmega64 / peripheriques integres

1

ATMEL ATMEGA64 / PERIPHERIQUES INTEGRES

1 INTRODUCTION

Ce document est une synthèse de la documentation constructeur nécessaire pour les TDs / TPs et

l’évaluation finale. Seuls les périphériques intégrés suivants sont décrits ici :

Ports d’entrée / sortie

Timers

Convertisseur Analogique Numérique

2 LES PORTS D’ENTREE / SORTIE PARALLELES

2.1 DESCRIPTION

Chacun des 7 ports d’interface parallèles de l’ATmega64 sont accessibles au travers de 3 registres 8

bits.

Un registre de direction DDRx : Un "1" logique dans un de ses bits, configure la broche de

port correspondante en sortie. Un "0" la configure en entrée.

Un registre de données entrantes PINx : L’état des bits de ce registre reflète les niveaux

présents en entrée sur les broches correspondantes.

Un registre de données sortantes ou d’option, PORTx : l’état des bits de ce registre fixe le

niveau des broches correspondantes qui sont configurées en sortie. Si les broches

correspondantes sont configurées en entrée, un "1" logique dans un des bits du registre

valide, la résistance de rappel interne au +VCC.

2.2 CONFIGURATION DES BROCHES

Chaque broche d’un port peut être configurée individuellement. Il suffit pour cela de positionner à 1

ou à 0 les bits des registres DDRx et PORTx.

Bit du

DDRx

Bit du

PORTx

Direction

Configuration

0

0

Entrée

Sans résistance de tirage au 5V (Pull-Up).

0

1

Entrée

Avec résistance de tirage au 5V (Pull-Up).

1

0

Sortie

La broche délivre un niveau bas.

1

1

Sortie

La broche délivre un niveau haut.

La lecture du registre PINx donne l’état des broches du PORTx orientées en entrée. L’écriture dans le

registre PORTx fixe l’état des broches configurées en sortie. (PINx n’est accessible qu’en lecture)

2.3 UTILISATION DES PORTS PARALLELES

L’utilisation des ports d’entrée / sortie parallèle généralement effectuée de la façon suivante :

Définition de la direction des broches du port par le registre DDRx.

Ecriture dans le registre PORTx pour définir le niveau des broches configurées en sortie ou la

présence ou non d’une résistance de rappel sur les broches configurées en entrée.

2

Lecture dans le registre PINx pour obtenir le niveau des broches configurées en entrée.

Exemple en langage C :

DDRD =0; // Tous les bits du port D sont en entrées

PORTD=0b11111111; // Résistance de rappel sur chaque entrée.

…

if ((PIND & 0b00000010)==0) {... // lecture du port D suivie d’un masquage et d’un test …

3 TIMERS

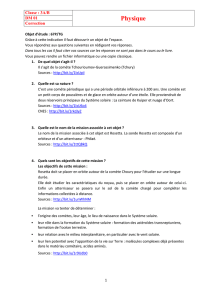

3.1 DESCRIPTION

Le fonctionnement d'un Timer/Compteur repose sur un compteur TCNTn (Timer CouNTer), à 8 ou 16

bits, incrémenté en permanence avec les fronts actifs d’une horloge clkTn et dont le contenu est

comparé en permanence au registre OCRn (Output Compare Register). Il peut générer des actions

sur une sortie OCn (Output Compare pin) à chaque égalité entre TCNTn et OCRn ou à chaque

débordement, etc.

Les 4 timers

ont des

structures très

proches.

La figure

suivante

montre les

points

communs et

les principales

différences.

L’horloge clkTn de TCNTn peut être :

l’horloge interne, via un pré-diviseur de fréquence (prescaler)

une horloge externe appliquée sur la broche Tn

Timer 0

uniquement

Timer 1, 2, 3

Pour les Timers 1 et 3, il y a 3

registres de comparaison + 3 géné.

de forme d’onde associés

Division par 1, 8, 32, 64,

128, 256, 1024

Avec les Timers 1 et 3, on peut fixer la

valeur max de comparaison (TOP)

(jusqu’à FFFF)

Les Timer 1 et 3 ont aussi un

registre de Capture

Broche du µC

Compteur

du timer

Horloge du

timer

Horloge

du timer

Registre(s) de

contrôle du timer

3

aucune horloge (timer non utilisé, permet de diminuer la consommation du µC).

Le ou les registres de commande TCCRn permettent de choisir parmi les modes de fonctionnement.

La demande d’interruption (Interrupt Request) positionne un bit à un dans le registre TIFR (Timer

Interrupt Flag Register) ou ETIFR (Extended Timer Interrupt Flag Register). Toutes les interruptions

sont individuellement masquées dans TIMSK (Timer Interrupt Mask Register) et ETIMSK (Extended

Timer Interrupt Mask Register).

L’ATmega64 intègre 4 timers possédant les caractéristiques suivantes :

Timer 0 et Timer 2 : Résolution : 8 bits, 1 registre de comparaison, utilisation en mode

normal, CTC ou PWM (MLI).

Timer 1 et Timer 3 : Résolution : 16 bits, 3 registres de comparaison, utilisation en mode

normal, CTC, PWM (MLI) ou Capture.

3.2 FONCTIONNEMENT "NORMAL"

Le mode normal est le mode de fonctionnement le plus simple.

TCNTn est incrémenté à chaque front actif de clkTn. TCNTn évolue de 0 à FF (ou FFFF). Au front

suivant, TCNTn déborde et le drapeau TOVn est mis à 1, générant une interruption si elle a été

autorisée. TCNTn repart de 0 et le cycle recommence.

Si le drapeau TOVn est utilisé (sans interruption), il doit être remis à 0 par le programme utilisateur.

Une nouvelle valeur peut être écrite n'importe quand dans le registre TCNTn.

Le Timer combiné avec l’unité de comparaison OCRn peut être employé pour produire une

interruption au bout d’un temps donné.

Durée comptage (DC) :

TCNTn 8 bits, F quartz = 8 MHz

Sans prédivision pour l’horloge du timer : TclkTN = TclkI/O : DC = 256 / 8 MHz = 32 µs F = 30 KHz

Avec prédivision par 8 pour l’horloge du timer : TclkTN = 8 TclkI/O : DC = 8*256 / 8 MHz = 256 µs F =

3,9 KHz.

TCNTn

OCRn

TCNTnMAX

=255 (0xFF)

ou 65535

0

t

Interruption

provoquée par

TCNTn = OCRnX

Interruption provoquée

par le débordement de

TCNTn

0

1

2

3

4

TclkTn

256 (65536) TclkTn

4

3.3 FONCTIONNEMENT "CTC" (Clear Timer on Compare match)

Dans le mode CTC, le registre OCRn est employé pour définir le modulo du compteur. Le compteur

est incrémenté et lorsque sa valeur est égale à OCRn, le compteur est remis à 0 et le drapeau OCFn0

(Output Compare Flag) est mis à 1 pour déclencher une éventuelle interruption. L'OCRn définit la

valeur supérieure pour le compteur donc son modulo.

Sur la figure suivante, 4 valeurs de OCRn sont successivement écrites.

Le drapeau OCFn est mis à 0 lors de l’exécution du programme de traitement de l’interruption.

La durée entre 2 interruptions est égale à : TclkTn * (OCRn + 1). Le +1 n’est pas justifié dans la

doc.

3.3.1 GENERATION DE FREQUENCE AVEC LE MODE CTC

Ce mode peut être utilisé pour générer un signal carré dont la fréquence est liée à OCRn. Il suffit de

programmer un changement d’état sur la sortie OCn avec les bits COM du ou d’un des registre TCCR.

La fréquence du signal délivré en sortie est :

Avec N le rapport du pré-diviseur (1, 8, 64, 256 ou 1024) et Fclk_I/O étant la fréquence d’horloge

du quartz.

3.4 MODULATION DE LARGEUR D’IMPULSION (MLI)

Il existe 2 types de modulation de largeur d’impulsion :

MLI (ou PWM Pulse Width Modulation) « classique »

MLI rapide

Seule est mentionnée ici la MLI rapide

En mode MLI "rapide" le compteur TCNTn se comporte comme un compteur ordinaire. Lorsque sa

valeur atteint sa valeur maxi, le prochain front d’horloge provoque son débordement (RAZ).

OCRnN

OIfclk

OCn

f

12

/_

5

Avec les timers 16 bits 1 et 3, on peut choisir la valeur maxi entre 255, 511 et 1023, ce qui revient à

avoir un timer 8, 9 ou 10 bits. Ceci permet de diminuer la durée entre 2 débordements.

Un signal MLI peut être automatiquement généré sur la sortie OCnX, sans avoir à utiliser les

interruptions. La période de ce signal correspond à la durée entre 2 débordements.

3.5 REGISTRES COMMUNS AUX 4 TIMERS

TIFR (Timer Interrupt Flag Register) : Registre d’état des timers, indique l’état des compteurs et des

comparaisons.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

OCF2

TOV2

ICF1

OCF1A

OCF1B

TOV1

OCF0

TOV0

ETIFR (Extended Timer Interrupt Flag Register) : Registre d’état des timers, indique l’état des

compteurs et des comparaisons.

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

-

-

ICF3

OCF3A

OCF3B

TOV3

OCF3C

OCF1C

TOVn (Timer OVerflow flag du timer n) : positionné à 1 lorsque le compteur TCNTn déborde (Passage

de 255 à 0 ou 65535 à 0)

OCFn (Output Compare Flag du timer n) : positionné à 1 lorsque TCNTn = OCRn.

La remise à 0 de ces drapeaux s’effectue par :

L’écriture par votre programme d’un "1" dans le drapeau à remettre à 0.

Le microcontrôleur lui même si l’interruption correspondante au drapeau à été générée.

(Voir ci dessous)

TIMSK (Timer Interrupt Mask Register): Registre de validation des interruptions des timers

Permet de valider la génération d’interruptions par le timer. (A condition que le bit 1 du registre

SREG soit à 1)

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

OCIE2

TOIE2

TICIE1

OCIE1A

OCIE1B

TOIE1

OCIE0

TOIE0

TCNTn

OCRnX

TCNTnMAX

=255 (0xFF)

En mode MLI

rapide 8 bits

0

t

Mise à 0 de OCnX en

mode MLI non

complémentée

Mise à 1 de OCnX en

mode MLI non

complémentée

256 TclkTn

OCnX

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

1

/

14

100%