LA MEMOIRE

LA MEMOIRE

1. Les différents types de supports physiques

1.1 Format d'une barrette SIMM 8 bits

1.2 Format d'une barrette SIMM 32 bits

1.3 Format d'une barrette DIMM 64 bits

1.4 Format de la barrette RDRAM

2. Bancs de mémoire

2.1 Mémoire avec Parité et sans Parité

3. Structure physique de la mémoire

3.1 Architectures interne de la SRAM

3.2 Chronogramme des cycles d'accès

3.3 Cycle de lecture

3.4 Cycle d'écriture

3.5 Cycle de rafraîchissement

4. Description des différents types de mémoires

4.1 La mémoire FPM

4.2 La mémoire EDO

4.3 La mémoire BEDO

4.4 La mémoire SDRAM

4.5 La mémoire DDR SDRAM, QBM et DDR-II SDRAM

4.6 La mémoire QDR SDRAM et QDR-II SDRAM

4.7 La mémoire Rambus DRAM (RDRAM) et SLDRAM

4.8 La mémoire Auto-correctrice ECC et AECC

5. Taux de transfert des différents types de mémoires

6. Liens utiles

1. Les différents types de supports physiques

Il y a plusieurs manières d'intégrer physiquement des puces RAM à la carte mère ou à la carte d'extension. Les systèmes

anciens utilisent des puces mémoire séparées, appelées des puces DIP (à doubles rangées de broches), qui étaient

raccordées par des connecteurs ou soudées directement à une carte.

La plupart des systèmes modernes utilisent des barrettes mémoires appelées SIMM ( Single In-line Memory Module =

module mémoire à simple rangée de broches de connexion ).

Ce type de module combine plusieurs puces sur une petite plaquette enclenchée dans un socle de maintien. Le module

SIPP est semblable à un SIMM, mais utilise des broches à la place du connecteur plat pour se connecter à la carte mère.

Il est possible de transformer une barrette SIPP en SIMM en supprimant les broches, ou de transformer une SIMM en

SIPP en soudant les broches. Certaines sociétés fabriquent des convertisseurs de SIPP en SIMM qui permettent au SIPP de

se brancher sur des connecteurs SIMM 30 broches conventionnels. Il existe donc actuellement 4 types de support de

mémoire. Les puce DIP, les barrettes SIPP, SIMM et DIMM. Viens ensuite la génération de mémoires, RDRAM.

Fig. 1: Des barrettes SIP, avec leurs fines pattes soudées sont presque aussi délicates à installer que les puces

traditionnelles

1.1 Format d'une barrette SIMM 8 bits

Fig. 2: Les barrettes SIMM 30 broches sont plus pratiques. L'échancrure à gauche évite qu'elles soient montées à

l'envers. Ce sont des barrettes 8 bits.

1.2 Format d'uns barrette SIMM 32 bits

Barrette SIMM 72 broches 32 bits

Montage d'une barrette SIMM 72 broches

L'échancrure au milieu et à gauche évite qu'elle soit montée

à l'envers.

1.3 Format d'uns barrette DIMM 64 bits

Barrette DIMM 168 broches en 64 bits.

Montage d'une barrette DIMM 168 broches

Les deux échancrures au milieu évitent de monter la barrette à l'envers. Ces

barrettes existent en 3,3 v et en 5 v. La positions des échancrures varie en fonction

de la tension de la barrette.

Barrette DIMM 184 broches en 64 bits.

On voit qu'ici il n'y a qu'une seul échancrure.

Ces barrettes existent en 2,5 v.

Barrette DIMM 208 broches en 64 bits (QBM).

On voit ici la serie de petit composants situés en

dessous des blocs mémoires.

Le format DIMM est utilisé, entre autre, par des mémoires de type SDRAM en 168 broches puis par des mémoires DDR

SDRAM et QDR SDRAM en 184 broches et le 208 broches pour les mémoires QBM.

1.4 Format de la barrette RDRAM

Ce sont des barrettes mémoires séries constituées de composants 16 bits ( ou 18 bits ) avec un connecteur de 184 broches.

On a donc une largeur de bus de 16 bits ( Oui j'ai bien dit 16 bits ). Ce type de mémoire a fait son apparition début 1999 et

aurait dut se généraliser en 2002 malheureusement sont prix était trop excessif par rapport à la DDR Ram. Ce qui a eu

pour conséquence de faire disparaître petit à petit ce type de mémoire.

2. Bancs de mémoire

Les barrettes mémoire ( SIPP, SIMM et DIMM ) sont organisées en bancs sur les cartes mères et les cartes mémoires.

Vous devez connaître l'agencement du banc de mémoire et sa position sur les cartes mères et les cartes mémoires quand

vous ajoutez de la mémoire au système. En outre, les diagnostics mémoire indiquent les emplacements des erreurs par

octet et par adresse et vous devez utiliser ces chiffres pour savoir où se trouve le banc défectueux. Les bancs de mémoire

correspondent, en général, à la capacité du bus de données du microprocesseur.

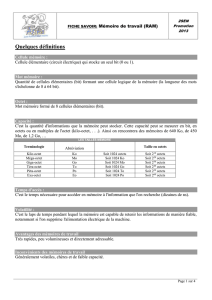

Le Tableau suivant montre la taille de chaque banc selon le type de PC :

Processeur

Bus de

données

Taille du banc

( Parité )

SIMM 30 broches par

banc

SIMM 72 broches par

banc

8088

8 bits

9 bits

1

1 (4bancs)

8086

16 bits

18 bits

2

1 (2bancs)

286

16 bits

18 bits

2

1 (2bancs)

386SX, SL, SLC

16 bits

18 bits

2

1 (2bancs)

386DX

32 bits

36 bits

4

1

486SLC,SLC2

16 bits

18 bits

2

1 (2bancs)

486SX, DX, DX2,

DX4

32 bits

36 bits

4

1

Pentium

64 bits

72 bits

8

2

Le nombre de bits de chaque banc peut être fait de simples puces ou de SIMM. Par exemple, dans un système 286 utilisant

un banc 18 bits, vous pourriez faire un bloc de 18 puces d'une capacité de 1 bit, ou utiliser quatre puces d'une capacité de 4

bits, pour les bits de données, et deux puces d'une capacité de 1 bit comme bits de parité. La plupart des systèmes

modernes n’utilisent pas de puces mais des SIMM. Si le système dispose d'un banc 18 bits, il utilisera plutôt des SIMM 30

broches, deux par banc. Toutes les barrettes SIMM d'un même banc doivent être de la même taille et du même type.

Comme vous pouvez le constater, les SIMM 30 broches sont moins intéressants pour les systèmes 32 bits parce que vous

devez en utiliser quatre par banc !

Ces SIMM n’étant disponibles qu’en 1 Mo ou 4 Mo, cela signifie qu'un banc doit faire 4 Mo ou 16 Mo de mémoire. II

n'y a pas de capacité intermédiaire.

L'utilisation de SIMM 30 broches dans un système 32 bits limite artificiellement la configuration de la mémoire et n'est

pas conseillé. Sur les systèmes 32 bits qui utilisent des SIMM 72 broches, chaque SIMM représente un banc séparé et

peut être ajouté ou enlevé individuellement, et non forcément par groupe de quatre. La configuration de la mémoire est

ainsi plus facile et plus souple. Par contre sur des systèmes 64 bits comme les Pentium II, les barrettes SIMM doivent être

utilisées par paires. Seules les barrettes DIMM de 64 bits peuvent être montées par unité.

La disposition physique sur les cartes mères ou les cartes mémoire est arbitraire, elle est déterminée par les constructeurs.

Vous pouvez choisir la disposition de votre carte mère ou de vos cartes d'extension en faisant des tests, mais cela prend du

temps et ce n'est pas toujours facile, surtout si vous avez des problèmes avec votre système. La documentation de votre

système ou de votre carte vous y aidera.

2.1 Mémoire avec Parité et sans Parité

Les mémoires avec parité sont des mémoires qui utilisent 1 bit supplémentaire pour stocker la parité d'un octet ( 8 bits ).

C'est à dire que lorsque le système écrit un octet, par exemple 0000 0010, il compte le nombre de bit qui sont à 1. Si ce

nombre est pair alors le bit de parité est mis à 0 sinon il est mis à 1. De même, à chaque lecture, le système recalcule le

nombre de bit à 1 et vérifie que le résultat correspond bien à la valeur stockée. Pour que le contrôle de parité soit effectué,

il faut au préalable qu'il soit activé dans le bios. Lorsqu'une erreur de parité est détectée, le système est toujours arrêté

brutalement avec un message du type :

'PARITY ERROR AT 0AB5:00BE. SYSTEM HALTED.'

Et cela pour les systèmes d'exploitation DOS, Windows v3.11 et Windows 95, car c'est une erreur matérielle classifiée de

'FATALE' et que l'on ne peut pas ignorer. Par contre certains systèmes comme Linux ou SCO-Unix, gèrent eux même

cette erreur soit en détournant l'interruption 02h soit en mettant à zéro le bit 7 du port 70h. Certain type de mémoire stocke

le nombre de bit impair au lieu du nombre de bit pair. Le tableau suivant fournit la valeur du bit de parité en fonction du

type de mémoire

Type

Bits de données

Nombre de 1

Bit de parité

Parité pair

0000 0000

pair

0

1000 1001

impair

1

Parité impaire

1000 1000

pair

1

0111 0000

impair

0

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

1

/

17

100%