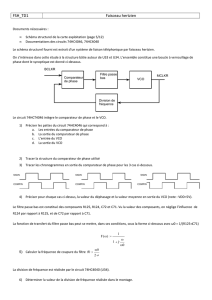

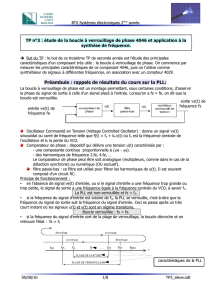

2. Schéma n°1

TpPll1 R&T Page 1 sur 24

T.P. La boucle à verrouillage de

phase (PLL) : caractérisation

Objectif : Comprendre le fonctionnement d'une PLL..

1. Introduction :

Une boucle à verrouillage de phase (ou Phase Locked Loop en anglais, souvent abrégé par PLL) est un système bouclé

dont le but est d’asservir la phase instantanée du signal de sortie d’un oscillateur à celle d’un signal de référence.

Le principe a été étudié par Bellescize en 1932, mais la technologie de l’époque ne permettait pas de réaliser des

montages simples et économiques. Il a fallu attendre l’avènement des circuits LSI (Large Scale Integration) pour voir

les PLL se développer dans de nombreuses applications. Citons par exemple :

démodulation AM et FM

multiplication de fréquence

synthèse de fréquence

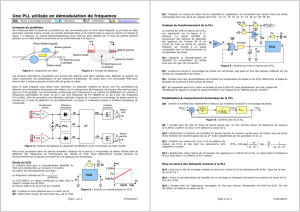

La boucle à verrouillage de phase présente le schéma fonctionnel suivant :

: N

Diviseur de

retour

(facultatif)

KV(s)

VCO

KF(s)

Filtre

passe-bas

+

-

Comparateur

de

phase

Toute PLL est constituée d’un :

comparateur de phase de gain (V/rad)

filtre passe-bas de fonction de transfert KF(s) (V/V)

oscillateur contrôlé en tension (VCO) de gain KV(s) (rad/s/V)

Fonctionnement qualitatif :

Nous allons d’abord étudier la manière dont une PLL se verrouille et définir les notions de fréquence libre, plage de

verrouillage et plage de capture. Le montage d’étude est conforme à la figure suivante :

fOUT

OUT

Figure 2

fIN

IN

Figure 1

TpPll1 R&T Page 2 sur 24

KV(s)

VCO

KF(s)

Filtre

passe-bas

+

-

Comparateur

de

phase

GBF

source

A. Caractéristiques des différents éléments constituant la PLL :

A.1. Comparateur de phase :

Phase d’un signal :

Un signal de la forme :

v = Vsin(t)

permet de définir :

la phase instantanée (radians)

la pulsation instantanée =

d

dt

(radians/s)

N.B :

f =

2

Le comparateur de phase de notre PLL est supposé avoir la caractéristique linéaire suivante :

Remarques :

Lorsque , on a U0 = 0V.

La tension U0 représente la tension continue ou basse fréquence que laisse passer le filtre passe-bas.

A.2. Le filtre passe-bas :

fOUT

OUT

fIN

IN

U0 (V)

+

-

+

-

(rad)

Figure 3

TpPll1 R&T Page 3 sur 24

Pour notre exemple, il est considéré comme parfait ; sa fréquence de coupure est de 100Hz :

A.3. Le VCO :

Il est défini par la caractéristique suivante :

Remarque :

Un VCO est un montage qui est conçu pour travailler sur une gamme de fréquence importante. Il existe plusieurs

structures électroniques pouvant réaliser cette fonction.

B. Etude du fonctionnement pour fIN variable :

Tension d’entrée nulle :

On suppose que le VCO oscille à sa fréquence libre f0 = 1KHz, on a donc vOUT = VOUT.sint. Le déphasage entre vIN et

vOUT est t. Le filtre passe-bas élimine cette composante, donc u0 = 0V, ce qui confirme que le VCO oscille à sa

fréquence libre.

En conclusion :

Le VCO d’une PLL bouclée à entrée nulle, oscille à sa fréquence libre f0

Tension d’entrée alternative à fréquence croissante :

Prenons différentes fréquences :

fIN = 100 Hz

vIN = VIN. sint et vOUT = VOUT. sint

avec fIN = 100 Hz et fOUT = f0 = 1KHz

Le comparateur de phase donne un signal constitué de deux composantes :

fréquence fIN + fOUT = 1,1KHz et

fréquence fIN - fOUT = 900Hz

Ces deux composantes sont éliminées par le filtre passe-bas parfait, u0 = 0V.

f (Hz)

100

20log

U

U

0

(dB)

Figure 4

Figure 5

fOUT (Hz)

U0 (V)

+5

+2,5

-2,5

-5

1200

1100

900

800

f0 = 1000

TpPll1 R&T Page 4 sur 24

100 Hz < fIN < 900 Hz

Le filtre fournit toujours u0 = 0V.

fIN = 900 Hz

La différence des fréquences donne 100 Hz. Nous sommes dans la bande passante du filtre ; u0 devient une composante

variable à 100 Hz. La fréquence de sortie du VCO est modifiée de telle sorte que l’écart | fIN - fOUT | diminue. La tension

u0 présente une fréquence de battement qui diminue et une valeur moyenne qui devient négative jusqu'à atteindre la

valeur de -2,5V, la fréquence de sortie est égale à celle de l’entrée : on dit que la boucle est verrouillée. La fréquence de

900 Hz est appelée fréquence de capture.

900 Hz < fIN <1200 Hz

La boucle reste verrouillée, la fréquence de sortie suit fidèlement la fréquence d’entrée.

fIN > 1200 Hz

La boucle se déverrouille. Le VCO oscille alors à sa fréquence libre f0.

La figure 6 résume le fonctionnement du système.

Tension d’entrée à fréquence décroissante :

Le raisonnement est identique au cas précédent et le fonctionnement est résumé sur la figure 6 :

La figure 6 nous permet de définir deux caractéristiques importantes des PLL :

la plage de capture fL = (f3 - f1)

la plage de verrouillage fH = (f2 - f4)

On a toujours : fH > fL

Précisons également que le verrouillage de la boucle ne se fait pas de manière instantanée et on a coutume de définir un

temps d’accrochage (lock-up time) qui est un paramètre important d’une PLL.

fIN

fIN

f0

f0

fL

fH

f1

900 Hz

f2

1200 Hz

f1

900 Hz

f4

800 Hz

f3

1100 Hz

Figure 6

TpPll1 R&T Page 5 sur 24

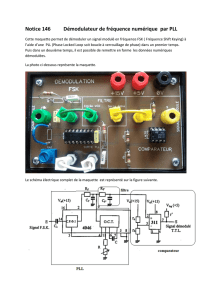

Présentation du circuit 4046

Ce circuit contient :

Un VCO (Oscillateur commandé en tension) dont les paramètres fmin et fmax sont réglables par trois éléments

extérieurs : R1(réglage de fmin-fmax), R2 (réglage de fmin) et C1.

Un suiveur permettant de lire la tension d’entrée du VCO.

Il contient deux comparateurs de phase :

- un circuit « OU EXCLUSIF » : CP1

- un circuit à sortie 3 états : CP2

-

I / ETUDE du V.C.O. (Oscillateur commandé en tension)

On veut que le VCO délivre en sortie un signal :

dont la fréquence fo dite fréquence centrale soit égale à 40 kHz

sur une certaine plage de fréquence notée : 2 fL = 4 kHz

1.1) Détermination des composants externes du VCO

En utilisant les caractéristiques du circuit données en (Annexe n°2) et notamment celles concernant le VCO

fonctionnant avec déviation de fréquence ( pages 23 24)

1.1.1) Donner l’expression de fmax et calculer sa valeur.

………………………………………………………………………

1.1.2) Donner l’expression de fmin et calculer sa valeur.

………………………………………………………………………

1.1.3) Calculer

min

max

f

f

min

max

f

f

………………………………….

1.1.4) A partir

min

max

f

f

et des caractéristiques de la figure 9 page 23.

Déterminer le rapport

1

2

R

R

, puis l’expression qui relie R2 à R1.

1

2

R

R

= ……………………………………………

………………………………………………………………………

1.1.5) On fixe R2 à 10 k

, déduire la valeur de R1.

………………………………………………………………………

R1 = ………………………...

1.1.6) Connaissant fmin et R2, déterminer la valeur de la capacité C1 d’après les caractéristiques de la figure 8

page 22.

C1 = …………………………………………..

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

1

/

24

100%