DECODAGE D`ADRESSE : TD n°1 - Sn-Bretagne

TD : DECODAGE D’ADRESSES

LYCEE LA FAYETTE 1/7

DECODAGE D’ADRESSES: TD n°1

Objectif : Au cours de ce TD, nous allons voir les notions fondamentales concernant le

décodage d’adresses:

- Quel est le but du décodage d’adresse.

- Comment est-il implémenté dans une architecture à microprocesseur.

- Comment établir un plan mémoire d’un système à microprocesseur existant.

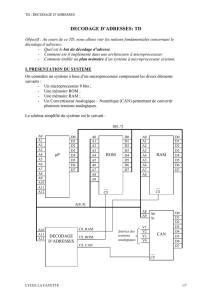

I. PRESENTATION DU SYSTEME

On considère un système à base d’un microprocesseur comprenant les divers éléments

suivants :

- Un microprocesseur 8 bits ;

- Une mémoire ROM ;

- Une mémoire RAM ;

- Un Convertisseur Analogique – Numérique (CAN) permettant de convertir

plusieurs tensions analogiques.

Le schéma simplifié du système est le suivant :

µP

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

ROM

A0

A1

A2

A3

A4

A5

A6

A7

D0

D1

D2

D3

D4

D5

D6

D7

A8

A9

A10

A11

A12

A8

A9

RAM

A0

A1

A2

A3

A4

A5

A6

A7

D0

D1

D2

D3

D4

D5

D6

D7

A8

D[0..7]

A[0..9]

DECODAGE

D’ADRESSES

A11

A12

A10

CAN

D0

D1

D2

D3

D4

D5

D6

D7

A8

A9

V1

V2

V3

V4

Entrées des

tensions

analogiques

CS

CS_RAM

CS_ROM

CS_CAN

CS

CS

S0

S1

TD : DECODAGE D’ADRESSES

LYCEE LA FAYETTE 2/7

II. VOCABULAIRE ET DEFINITION

Question II.1. Calculer la capacité de la mémoire RAM en octets et en kbits.

Capacité = 29 octets = 512 octets = 4 kbits

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question II.2. Calculer la capacité de la mémoire ROM en ko et en kbits.

Capacité = 210 octets = 1024 octets = 1 ko = 8 kbits

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question II.3. Comment se nome le bus D[0..7] ?

C’est le bus de données : C’est sur ce bus que sont présentes les données lues sur les

divers circuits du système.

…………………………………………………………………………………………………

Question II.4. Comment se nome le bus A[0..7] ?

C’est le bus d’adresses : C’est sur ce bus que sont présentes les adresses permettant

d’adresser les divers circuits du système.

…………………………………………………………………………………………………

Question II.5. Que signifie le terme

CS

? Sur quel état logique cette entrée est-elle valide ?

CS = Chip Select. Il permet la sélection du boîtier. Cette entrée est valide sur un état

logique bas.

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question II.6. Cocher la bonne réponse : Lorsque le signal

CS

de la RAM et de la ROM est

à l’état logique « 1 »….

Les sorties de la RAM et de la ROM sont à « 1 » ou à « 0 » suivant les

valeurs contenues dans les mémoires

Les sorties du circuit intégré sont en haute impédance « HZ »

Question II.7. Cocher la bonne réponse : Dans le cas où les signaux

CS

de la RAM et de la

ROM sont à l’état bas en même temps…

Il n’y a pas de conflit sur le bus de données

Il y a un conflit car les signaux D0 à D7 de ces deux composants sont

présents sur le bus de données.

TD : DECODAGE D’ADRESSES

LYCEE LA FAYETTE 3/7

Question II.8. Si on veut lire les données de la RAM, quels circuits doit-on désactiver afin

d’éviter un conflit sur le bus de données ?

Il faut désactiver la ROM et le CAN.

…………………………………………………………………………………………………

Question II.9. Si on veut lire les données de la ROM, quels circuits doit-on désactiver afin

d’éviter un conflit sur le bus de données ?

Il faut désactiver la RAM et le CAN.

…………………………………………………………………………………………………

Question II.10. Si on veut lire les données du CAN, quels circuits doit-on désactiver afin

d’éviter un conflit sur le bus de données ?

Il faut désactiver la RAM et la ROM.

…………………………………………………………………………………………………

Question II.11. Expliquer succinctement le rôle du décodage d’adresses dans un tel système.

Le décodage d’adresses permet de sélectionner un seul circuit parmi tous ceux présents

dans le système. Cela permet de mettre les sorties des circuits non utilisés lors de

l’adressage en haute impédance. Ainsi il n’y a pas de conflits.

…………………………………………………………………………………………………

III. FONCTIONNEMENT DU CAN

Le CAN utilisé dans ce système permet de convertir jusqu’à 4 tensions analogiques. Les

tensions analogiques à convertir sont sélectionnée à l’aide des broches S0 et S1.

La table suivante indique comment sont sélectionnées les tensions analogiques à l’entrée du

CAN :

S1

S0

Tension analogique sélectionnée

0

0

V1

0

1

V2

1

0

V3

1

1

V4

Question III.1. Compléter le tableau suivant :

A9

A8

Tensions analogique sélectionnée

0

0

V1

0

1

V2

1

0

V3

1

1

V4

TD : DECODAGE D’ADRESSES

LYCEE LA FAYETTE 4/7

IV. ETABLISSEMENT DU PLAN MEMOIRE DU SYSTEME

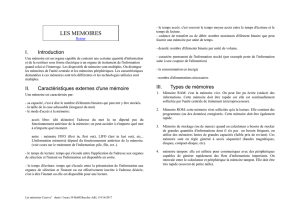

Afin de réaliser la fonction décodage d’adresses, on utilise un circuit 74138. Le schéma du

système est le suivant :

La table de vérité du circuit 74138 est la suivante :

Entrées

Sorties

4

2

1

0

1

2

3

4

5

6

7

0

0

0

0

1

1

1

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

0

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

0

µP

D0

D1

D2

D3

D4

D5

D6

D7

A0

A1

A2

A3

A4

A5

A6

A7

ROM

A0

A1

A2

A3

A4

A5

A6

A7

D0

D1

D2

D3

D4

D5

D6

D7

A8

A9

A10

A11

A12

A8

A9

RAM

A0

A1

A2

A3

A4

A5

A6

A7

D0

D1

D2

D3

D4

D5

D6

D7

A8

D[0..7]

A[0..9]

A11

A12

A10

CAN

D0

D1

D2

D3

D4

D5

D6

D7

A8

A9

V1

V2

V3

V4

Entrées des

tensions

analogiques

CS

CS

CS

S0

S1

&

EN

0

1

2

3

4

5

6

7

BIN/OCT

1

2

4

1

2

3

6

4

5

15

14

13

12

11

10

9

7

74LS138

CS_RAM

CS_ROM

CS_CAN

DECODAGE

D’ADRESSES

TD : DECODAGE D’ADRESSES

LYCEE LA FAYETTE 5/7

Question IV.1. Compléter le schéma structurel de la page précédente en reliant correctement

les broches 6, 4 et 5 (chacune au VCC ou à la masse) du 74138 afin de le valider.

Question IV.2. En vous aidant de la table de vérité du 74138, compléter le tableau suivant :

Adresses A[10..12]

Sorties du 74138

A12

A11

A10

0

1

2

3

4

5

6

7

0

0

0

0

1

1

1

1

1

1

1

0

0

1

1

0

1

1

1

1

1

1

0

1

0

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

1

1

1

1

1

0

0

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

0

1

1

1

1

1

1

0

1

1

1

1

1

1

1

1

1

1

1

0

Question IV.3. Quel doit être le niveau du signal CS_RAM pour sélectionner la RAM ?

Il faut CS_RAM = 0

Question IV.4. Quels doivent être les niveaux logiques sur A10, A11 et A12 afin de

sélectionner la RAM ?

Il faut A10=0 ; A11=0 et A12=0

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question IV.5. Quel doit être le niveau du signal CS_ROM pour sélectionner la ROM ?

Il faut CS_ROM = 0

Question IV.6. Quels doivent être les niveaux logiques sur A10, A11 et A12 afin de

sélectionner la ROM ?

Il faut A10 = 1 ; A11 = 0 ; A12 = 0

…………………………………………………………………………………………………

…………………………………………………………………………………………………

Question IV.7. Quel doit être le niveau du signal CS_CAN pour sélectionner le CAN ?

Il faut CS_CAN = 0.

Question IV.8. Quels doivent être les niveaux logiques sur A10, A11 et A12 afin de

sélectionner le CAN ?

Il faut A10 = 0 ; A11 = 1 et A12 = 0

…………………………………………………………………………………………………

…………………………………………………………………………………………………

6

6

7

7

1

/

7

100%