Décalages, Multiplication, Virgule Fixe, Machines d'État en VHDL

Telechargé par

xeni0islove

Décalage arithmétique et logique

Les décalages et les rotations arithmétiques et

logiques s'effectuent avec des fonctions qui font

partie des packages ieee.numeric_std: shift_left

(), shift_right (), rotation_left () et rotation_right

().

La différence entre les décalages arithmétiques

et logiques est codée dans le type du premier

argument de la fonction.

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity shift_ex is

port (

r_Shift1 : in std_logic_vector(3 downto 0) ;

r_Unsig_L : out unsigned(3 downto 0);

r_Unsig_R : out unsigned(3 downto 0);

r_Sig_L : out signed(3 downto 0) ;

r_Sig_R : out signed(3 downto 0) );

end shift_ex;

architecture arch of shift_ex is

begin

process (r_Shift1)

begin

r_Unsig_L <= shift_left(unsigned(r_Shift1), 1);

r_Sig_L <= shift_left(signed(r_Shift1), 1);

r_Unsig_R <= shift_right(unsigned(r_Shift1), 2);

r_Sig_R <= shift_right(signed(r_Shift1), 2);

end process;

end architecture arch;

S. Belkouch, ENSA Marrakech 2

architecture arch of shift_ex is

begin

process (r_Shift1)

begin

r_Unsigned_L <= shift_left(unsigned(r_Shift1), 1);

r_Signed_L <= shift_left(signed(r_Shift1), 1);

r_Unsigned_R <= shift_right(unsigned(r_Shift1),

2);

r_Signed_R <= shift_right(signed(r_Shift1), 2);

end process;

end architecture arch;

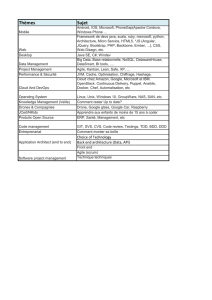

Multiplication

En général, les FPGAs contiennent

des blocs DSP pour faire le

traitement de signal. Ces blocs

contiennent des multiplicateurs

codés en VHDL. Sur Cyclone II, il y

a des multiplicateurs embarqués

18x18.

Signal P : signed(2 * N –1 downto 0);

Signal A, B : signed(N –1 downto 0);

…

P <= A * B;

signal Acc, mult: signed(2 * N –1 downto 0);

signal A, B : signed(N –1 downto 0);

…

process (clk)

begin

if rising_edge(clk) then

mult <= A * B;

Acc <= Acc + mult;

end if;

end process;

S. Belkouch, ENSA Marrakech

Nombres à virgule fixe

Package:

use ieee.fixed_pkg.all (n’est pas

supporté dans Quartus utilisé

dans les TPs)

Exemple d’addition

-nombres non signés

signal n1,n2 : ufixed(4 downto -3);

signal n3 : ufixed(5 downto -3);

begin

n1 <= to_ufixed (5.75,n1);

-- n1 = "00101110" = 5.75

n2 <= to_ufixed (6.5,n2);

-- n2 = "00110100" = 6.5

n3 <= n1+n2;

-- n3 = "001100010" = 12.25

-nombres signés:

signal s1,s2 : sfixed(4 downto -3);

signal s3 : sfixed(5 downto -3);

s1 <= to_sfixed (5.75,s1);

-- s1 = "00101110" = 5.75

s2 <= to_sfixed (-6.5,s2);

-- s2 = "11001100" = -6.5

s3 <= s1+s2;

-- s3 = "111111010" = -0.75

Exemple de soustration

-nombres non signés

n1 <= to_ufixed (5.75,n1);

n2 <= to_ufixed (6.5, n2);

n3 <= n2-n1; -- n3 = "000000110" = 0.75

-nombres signés

s1 <= to_sfixed (5.75,s1);

s2 <= to_sfixed (-6.5,s2);

s3 <= s2-s1;

-- s3 = "110011110" = -12.25

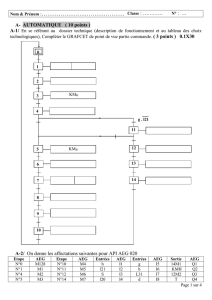

Machines à états finis

6

6

7

7

8

8

9

9

10

10

11

11

12

12

1

/

12

100%