INSTITUT NATIONAL POLYTECHNIQUE DE TOULOUSE

ECOLE NATIONALE SUPERIEURE D’ELECTROTECHNIQUE,

D’ELECTRONIQUE, D’INFORMATIQUE, D’HYDRAULIQUE ET DES

TELECOMMUNICATIONS

DEPARTEMENT D’ELECTRONIQUE - TRAITEMENT DU SIGNAL

COURS ET TRAVAUX PRATIQUES

DE

MICROPROCESSEUR

M.CATTOEN

Janvier 2003

-0-

TABLE DES MATIERES

INTRODUCTION..................................................................................................................................................3

CHAPITRE I..........................................................................................................................................................5

PRINCIPES GENERAUX DES CALCULATEURS NUMERIQUES .............................................................5

INTRODUCTION..................................................................................................................................................5

I-1 FONCTION MEMOIRE.................................................................................................................................8

I-1-1 DEFINITIONS ....................................................................................................................................................8

I-1-2 ORGANISATION DES MEMOIRES........................................................................................................................8

I-1-2-1 Organisation par bits...............................................................................................................................8

I-1-2-2 Organisation par mots...........................................................................................................................10

I-1-3 CLASSIFICATION DES MEMOIRES ....................................................................................................................11

I-1-3-1 Mémoires mortes ...................................................................................................................................11

I-1-3-2 Mémoires vives ......................................................................................................................................13

I-1-3-3 Association de mémoires .......................................................................................................................16

I-1-3-4 Autres types de mémoire........................................................................................................................17

I-2 L'UNITE DE TRAITEMENT ......................................................................................................................20

I-2-1 STRUCTURE INTERNE .....................................................................................................................................20

I-2-1-1 Rôle de l'ALU.........................................................................................................................................21

I-2-1-2 Registres de données .............................................................................................................................22

I-2-1-3 Registres d'adresses...............................................................................................................................22

I-2-1-4 Unité de commande ...............................................................................................................................23

I-2-2 ASPECT LOGICIEL...........................................................................................................................................24

I-2-2-1 Classification des instructions...............................................................................................................24

I-2-2-2 Format des instructions .........................................................................................................................24

I-2-2-3 Modes d'adressage ................................................................................................................................24

I-2-2-4 Instructions de saut................................................................................................................................28

I-3 LES ORGANES D'ENTREE-SORTIE........................................................................................................30

I-3-1 FONCTIONS DE BASE ......................................................................................................................................30

I-3-1-1 Isolation-Mémorisation .........................................................................................................................30

I-3-1-2 Synchronisation .....................................................................................................................................30

I-3-1-3 Adressage des organes d'E/S.................................................................................................................31

I-3-1-4 Adaptation du format des informations .................................................................................................32

I-3-2 PROCÉDURES D'ÉCHANGE ..............................................................................................................................32

I-3-2-1 Mode programmé par test de mot d'état................................................................................................33

I-3-2-2 Mode programmé par interruption........................................................................................................33

I-3-2-3 Mode en "accès direct mémoire (DMA)"...............................................................................................37

CHAPITRE II ......................................................................................................................................................41

ETUDE DE MICROPROCESSEURS ET D'ORGANES D'ENTREE-SORTIE ..........................................41

II-1 LE MICROCONTROLEUR 8051 ..............................................................................................................41

II-1-1 ORGANISATION EXTERNE .............................................................................................................................41

II-1-1-1 Chronologie des échanges avec la mémoire ........................................................................................42

II-1-2 ORGANISATION INTERNE ..............................................................................................................................45

II-1-3 LES INSTRUCTIONS DU 8051 .........................................................................................................................48

II-1-4 MODES D'ADRESSAGE...................................................................................................................................48

II-1-4-1 Mode implicite......................................................................................................................................48

II-1-4-2 Mode immédiat.....................................................................................................................................49

-1-

II-1-4-3 Mode direct ..........................................................................................................................................49

II-1-4-4 Mode indirect .......................................................................................................................................49

II-1-4-5 Mode indexé .........................................................................................................................................49

II-1-4-6 Mode relatif ..........................................................................................................................................49

II-1-4-7 Opérations spéciales ............................................................................................................................50

II-2 L'INTERFACE PARALLELE 8255 (PROGRAMMABLE PERIPHERAL INTERFACE PPI) ........53

II-2-1 PRESENTATION DU CIRCUIT ..........................................................................................................................53

II-2-1 MODES DE FONCTIONNEMENT ......................................................................................................................54

II-3 LES TRANSMISSIONS SERIE..................................................................................................................57

II-3-1 GENERALITES ...............................................................................................................................................57

II-3-1-1 Communications asynchrones..............................................................................................................57

II-3-1-2 Communications synchrones................................................................................................................58

II-3-2 EXEMPLE D'INTERFACE SERIE : L'ACIA MC 6850........................................................................................59

II-3-2-1 Présentation du circuit (Fig.II-3-2)......................................................................................................59

II-3-2-2 Fonctionnement....................................................................................................................................61

CHAPITRE III.....................................................................................................................................................65

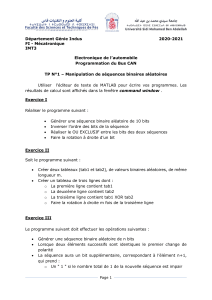

III-1 DESCRIPTION DU MATERIEL DE TRAVAUX PRATIQUES................................................................65

III-2 DESCRIPTION DE LA CARTE MICR0CONTROLEUR 8051..................................................................66

III-3 DESCRIPTION DE LA PLAQUETTE DE TP-CNA...................................................................................67

III-4 TRAVAIL A REALISER..............................................................................................................................69

III-4-1 Utilisation de l’environnement MUVISION ...........................................................................................69

III-4-2 Exercices de programmation..................................................................................................................70

III-4-3 Sortie d’informations..............................................................................................................................71

III-4-4 Conversion analogique-numérique ........................................................................................................72

III-4-5 Acquisition de données...........................................................................................................................73

BIBLIOGRAPHIE...............................................................................................................................................75

ANNEXES ............................................................................................................................................................76

-2-

INTRODUCTION

L'apparition des microprocesseurs date du début des années 1970. A cette époque,

deux événements favorables sont apparus :

- le concept de "LSI (Large Scale Integration)" permettant d'intégrer plusieurs milliers de

portes sur un même substrat,

- l'arrivée à maturité de la technologie MOS caractérisée par sa faible consommation.

La conjugaison de ces événements a permis de regrouper une unité centrale

d'ordinateur dans un seul circuit intégré appelé "microprocesseur".

Depuis, une multitude de composants de ce type sont apparus au sein de familles

provenant essentiellement de grands constructeurs américains : Intel, Motorola, Advanced

Micro Devices (AMD), Texas Instruments,... et japonais : NEC, Mitsubishi,...

Grâce aux progrés de l’intégration, l'augmentation des performances a porté sur :

- la vitesse de fonctionnement,

- la largeur des mots traités (8, 16, 32, 64 bits),

- le nombre et la complexité des opérations réalisables.

L’intégration a également permis de rassembler le microprocesseur et les éléments

associés (mémoire, organes d’entrée-sortie,...) au sein d’un seul circuit appelé

-3-

"microcontrôleur". Ce type de composant s’est répandu dans un très grand nombre de

domaines (télécommunications, télévision, électro-ménager, hifi...).

L'objectif de ce cours est double : présenter les notions de base nécessaires à la

compréhension des systèmes utilisant des microprocesseurs et réaliser des travaux pratiques

permettant de programmer en langage machine (assembleur) une application d’acquisition de

données.

Ce document est divisé en 3 chapitres.

Le premier chapitre présente les principes généraux de fonctionnement des éléments

constituant les calculateurs numériques.

Le deuxième chapitre est consacré principalement à l'étude du microcontrôleur 8051 et

du circuit d’interface parallèle 8255 (PPI) qui seront mis en oeuvre dans les travaux pratiques.

Le troisième chapitre présente le matériel utilisé en travaux pratiques ainsi que les

différents programmes d’application à réaliser.

En annexe sont fournies des spécifications techniques détaillées des composants

utilisés et des informations sur le matériel et le logiciel utilisés en travaux pratiques.

-4-

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

81

81

82

82

83

83

84

84

85

85

86

86

87

87

88

88

89

89

90

90

91

91

92

92

93

93

94

94

95

95

96

96

97

97

98

98

99

99

100

100

101

101

102

102

103

103

104

104

105

105

106

106

107

107

108

108

109

109

110

110

111

111

112

112

113

113

114

114

115

115

116

116

117

117

118

118

119

119

120

120

121

121

122

122

123

123

124

124

125

125

126

126

127

127

128

128

129

129

130

130

131

131

132

132

133

133

134

134

135

135

136

136

137

137

138

138

139

139

140

140

141

141

142

142

143

143

144

144

145

145

146

146

147

147

148

148

149

149

150

150

151

151

1

/

151

100%